# INTRODUCTION TO FPGA PROGRAMMING

LESSON 16: ADVANCED FPGA TOPICS

Dr. Davide Cieri<sup>1</sup>

<sup>1</sup>Max-Planck-Institut für Physik, Munich

September 2024

- This lecture shows an overview of other advance FPGA topics, that we didn't have time to cover during the course

- I will not provide too many details

- Starting point for further studies

### ADVANCED VERIFICATION METHODOLOGIES

- Verification is crucial for ensuring the correctness of VHDL designs

- VHDL already provides standard features to automatise your test-benches

- Methodologies (Libraries) provide structured approaches to verification.

- UVVM and OSVVM are two popular methodologies in the VHDL community.

#### UVVM AND OSVVM

- UVVM (Universal VHDL Verification Methodology) and OSVVM are both free, open-source methodology for VHDL verification.

- They aim to simplify and standardize the verification process.

- Provide a set of libraries and tools for writing and managing testbenches

- Both requires simulator with full support to VHDL-2008 (no Vivado)

# сосотв

- COroutine based COsimulation TestBench (CocoTB)

- Runs python code concurrently and synchronously to the simulation

- No HDL testbench needed

- All python packages available

- Use cases

- Python golden model

- Connect real hardware

- Low simulation performance (longer execution)

- No support to Vivado simulator (yet)

#### VUNIT

- VUnit Python based Test Runner

- Open source unit testing framework for VHDL/SystemVerilog

- Workflow:

- 1. Scan through all files in a folder and build a dependency tree

- 2. Search for testbenches

- 3. Compile the sources in the correct order

- 4. Start the simulation (in parallel)

- 5. Report the test results

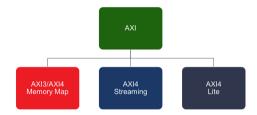

- AXI (Advanced eXtensible Interface) is an interface protocol defined by ARM.

- Nearly every Xilinx IP uses an AXI Interface

- Three types of AXI4-Interfaces:

- AXI4 (Full AXI4): For high-performance memory-mapped requirements.

- AXI4-Lite: For simple, low-throughput memory-mapped communication (for example, to and from control and status registers).

- AXI4-Stream: For high-speed streaming data

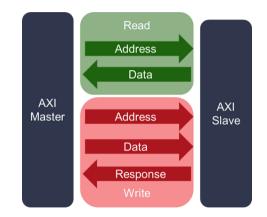

## AXI READ AND WRITE CHANNELS

- The AXI protocol defines 5 channels:

- Two for Read transactions:

- Read Address

- Read Data

- Three for Write Transactions:

- Write Address

- Write Data

- Write Response

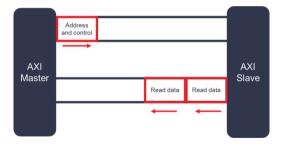

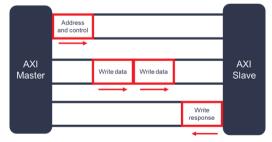

### AXI READ AND WRITE TRANSACTIONS

- AXI Master always initiates the transactions

- Multiple data can be transmitted on the same AXI address (burst)

#### **AXI REALITY**

| myip_v1_0vhd ? _ 1                                                                                                                           | Ξ'nΧ |

|----------------------------------------------------------------------------------------------------------------------------------------------|------|

| /home/dcieri/ip-repo-tests/myip_1_0/hd/myip_v1_0.vhd                                                                                         | ×    |

|                                                                                                                                              | •    |

| 31 :<br>32⊖ Ports of Axi Mester Bus Interface M00 AXI                                                                                        | ^    |

| 33 m00 axi init axi txn : in std logic;                                                                                                      |      |

| 34 moQ_axi_txn_done : out std_logic:<br>35: moQ axi_error : out std_logic;                                                                   |      |

| 36 m00_axi_aclk : in std_logic;                                                                                                              |      |

| 37 m00_axi_aresetn : in std legic;<br>38 m00 axi_wid : out std legic vector(C M00 AXI ID MIDTH-1 downto D);                                  |      |

| 39 m00 axi awaddr : out std logic vector(C M00 AXI ADDR NIDTH-1 downto 0);                                                                   |      |

| 40 m00_xx1_avlen : out std1legic_vector(7 downto 0);<br>41 m00_xx1_avize : out std1legic_vector(7 downto 0);                                 |      |

| 41 m00 xxi_mvsize : out stdlegic;vector(2 downto 0);<br>42 m00 xxi_wvburst: out stdlegic;vector(2 downto 0);                                 |      |

| 43 m00_axi_avlock : out std logic;                                                                                                           |      |

| 44 m00_xx1_avcache : out stdlegic_vector(3 downto 0);<br>45 m00 xx1 avprot : out stdlegic_vector(2 downto 0);                                |      |

| 46 m00_axi_awgos : out stdlogic vector(3 downto 0):                                                                                          |      |

| <pre>47 m00_axi_awuser : out stdlogic_vector(C_M00_AXI_AWUSER_WIDTH-1 downto 0);</pre>                                                       |      |

| 48 m00_exi_evvalid i out std[legic]<br>49 m00 exi_evvadv i in std[legic]                                                                     |      |

| 50 m00 axi wdata : out std logic vector(C_MO0_AXI_DATA_NIDTH-1 downto 0);                                                                    |      |

| 31: noO_axi_watb : out stdlegic_vector(C_MOO_AXI_DATA_NIDTh/08-1 downto 0);<br>52: noO_axi_wat : out stdlegic:                               |      |

| 53 moo as wiser : out stillogic vector(C MOO AXI WUSER NIDTH-1 downto 0);                                                                    |      |

| 54 m00 axi wvalid : out std logic;                                                                                                           |      |

| 55: moO_axi_wready : in std_legic.]<br>56: moO_axi_build : in std_legic.vector(C.MOO_AXI_ID_WIDTH-1_downto_0);                               |      |

| 57 m00_axi_bresp : in std logic_vector(1 downto 0);                                                                                          |      |

| 58 mOO_xxl_buser : in stdlegic_vector(C_MOO_AXI_BUSER_WIDTH-1 downto 0);<br>59 mOO xxi bwald : in stdlegic.                                  |      |

| 59 BOO_sxi_ovalid : in stat_oopic;<br>60 BOO_sxi_ovalid : out std leaf;                                                                      |      |

| 61 m00_axi_arid : out stdlogic_vector(C_M00_AXI_ID_WIDTH-1 downto 0):                                                                        |      |

| 62 m00_xx1_araddr : out stdlegic_vector(C_M00_AX1_A000_NUTDH-1 downto 0);<br>63 m00_xx1_arlen : out stdlegic_vector(Z downto 0);             |      |

| 64 m00 axi arsize : out std logic vector(2 downto 0):                                                                                        |      |

| 65 m00_axi_arburst : out stdlogic_vector(1 downto 0):                                                                                        |      |

| 06 m00_xxi_arlock : out stdlegic;<br>67 m00_xxi_arcache : out stdlegic vector(3 downto 0):                                                   |      |

| 68 m00 axi arprot ; out std logic vector(2 downto 0);                                                                                        |      |

| 69 m00_axi_arops : out std[legic_vector(3 downto 0);<br>70 m00_axi_arops : out std[legic_vector(3 downto 0);                                 |      |

| 70: m00_axi_aruser : out stdlegic_vector(C_M00_AXI_ARUSER_MIDTH-1 downto 0);<br>71: m00_axi_arusid : out stdlegic;                           |      |

| 72 m00 axi arready : in std logic;                                                                                                           |      |

| 73 mo0_axi_rid : in std_logic_vector(C_MO0_AXI_ID_MIDTH-1 downto 0);<br>74 mo0 axi_ridat : in std_logic_vector(C_MO0_AXI_AXIMDH-1 downto 0); |      |

| 75 m00_axi_rresp : in stdlogic vector(1_downto 0);                                                                                           |      |

| 70: moO_axi_rlast : in stdlogic;<br>77: moO_axi_ruser : in stdlogic; exctor(C.MOO_AXI_RUSER_NIDTH-1_downto_0);                               |      |

| //: BOU_sx1_ruser :: in std_togic_vector(c_MU_sx1_RuseK_NLDIH-1 downto 0);<br>78 : m00 axi_ruslid :: in std_togic;                           |      |

| 79 m00 axi rready : out std logic                                                                                                            |      |

| 80 ; );<br>81 ⊖ end myip_v1_0;                                                                                                               |      |

| 82 :<br>R3 — architecture arch imm of avin v3.0 is                                                                                           | ~    |

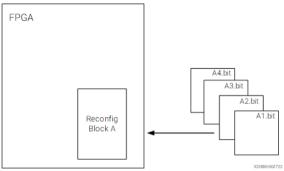

## PARTIAL RECONFIGURATION

- Partial Reconfiguration or Dynamic Function eXchange, allows for reconfiguration of modules within an active design

- A full bitstream is loaded on the FPGA, including FPGA regions that can be reconfigured

- Partial bitstream is loaded on the FPGA (dynamic configuration) during operation, to modify reconfigurable regions

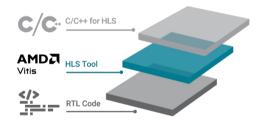

## **HIGH LEVEL SYNTHESIS**

- Major vendor provides tool to translate C/C++ code into RTL

- Xilinx AMD Vitis HLS

- Write code in C++ / C / System C

- Code converted by Vitis HLS into RTL

- C simulation available to validate functionalities

- Eventually, RTL is packed in an IP, and can be implemented in Vivado

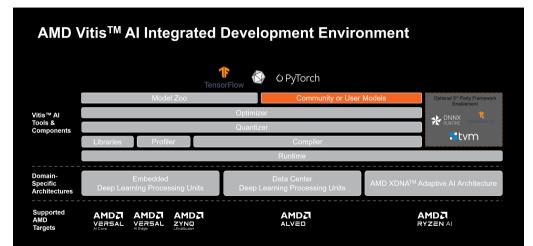

- Due to their ability of processing large chunks of data in parallel, FPGAs are ideal to infe machine learning algorithms

- Different options for the implementations:

- Write your own VHDL implementation of the algorithm

- Vitis-Al

- HLS4ML

#### **VITIS AI**

HLS4ML

- HLS4ML is a python package that translates machine learning models into C++ code for HLS

- Optimizes the algorithm for FPGA implementation

- Executes Vitis-HLS within python, to run synthesis and IP exportation

## CONTINUOUS INTEGRATION AND VERSION CONTROL

- Source code control in VHDL project is fundamental, especially in large collaboration

- Even small changes in the design, can result in large differences in the implementations

- Vivado projects are not git-friendly (long xml files)

- Hog (HDL-on-Git) is an open-source tool, that help maintaining HDL projects with git

- It also provides templates for Continuous Integration workflow, building and simulating HDL projects

The figures in these slides are taken from:

- Digital Design: Principles and Practices, Fourth Edition, John F. Wakerly, ISBN 0-13- 186389-4. ©2006, Pearson Education, Inc, Upper Saddle River, NJ. All rights reserved

- allaboutfpga.com

- nandland.com

- docs.amd.com

- https://www.symmetryelectronics.com/

- https://www.edn.com/

- Stephen A. Edwards, Columbia University, Fundamentals of Computer Systems, Spring 2012

- adafruit.com

- www.icdesigntips.com

- techdocs.altium.com

- anysilicon.com

- Yngve Hafting 2021, University of Oslo

- www.myomron.com