# EDET INSTRUMENT FIRMWARE - STATUS AND PLANS

Semiconductor Laboratory of the Max Planck Society

Mishal Rizwan

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

### **AGENDA**

Introduction

**DMC overview and Operation Modes**

MISHAL RIZWAN

**Old and New Sequencer IP**

**Data capturing**

**Summary and Outlook**

### INTRODUCTION

#### What we want:

- Implement various Operation Modes (OpModes) envisioned for the EDET Instrument (previous talk by J. Treis)

- Use the different features of the DMC-65 chip to accomplish this

- Well-designed sequences required by the DMC to realize the OpModes

- Formatting the data frames received from the DMC

- Specialized Firmware essential!

#### What we already have:

DHPT command sequencer

#### Can it do what we want?

### **DMC OPERATION MODES**

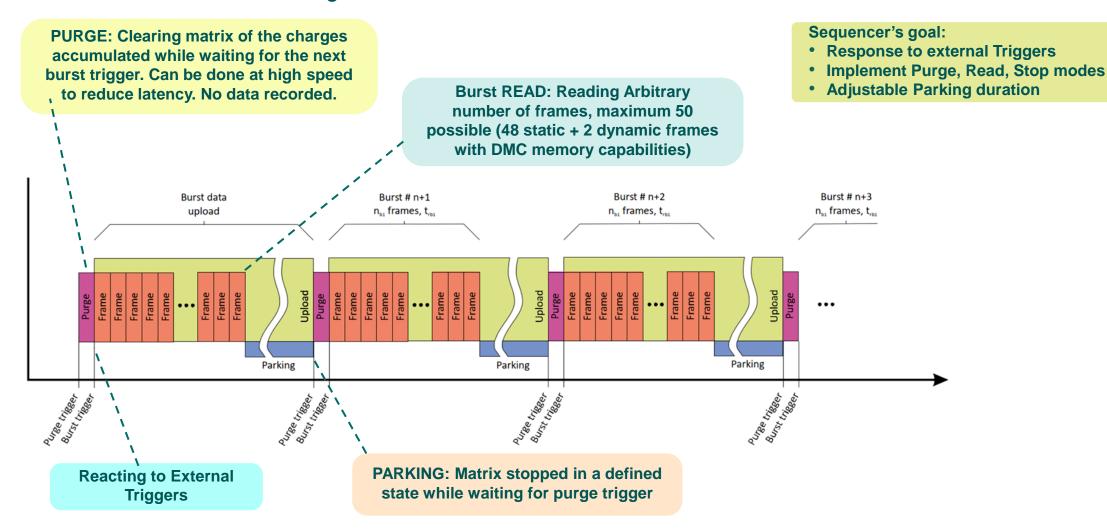

**EXAMPLE 1: Standard Purge/Burst**

### **DMC OPERATION MODES**

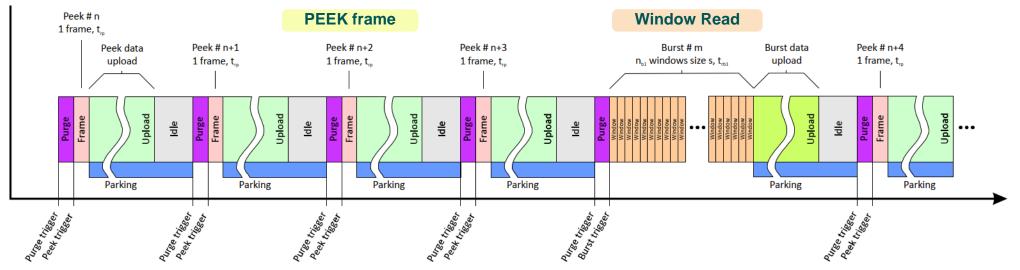

**EXAMPLE 2: Peek/Burst**

**Burst READ after observing** something scientifically **PEEK frame for observing some process** interesting in the Peek frame Purge → Read → Wait → Repeat Burst data Peek # n upload 1 frame, t, Peek # n+1 Peek # n+2 Peek # n+3 1 frame, t, 1 frame, t. 1 frame, t, Burst # m Peek data n, frames, t, upload Peek # n+4 1 frame, t. ldle **Parking** Parking **Parking Parking Parking Parking** Sequencer's goal: Short Exposure before frame read **Adjustable Parking**  Response to external Triggers duration while waiting • Implement Purge, Read, Stop modes Adjustable Parking duration

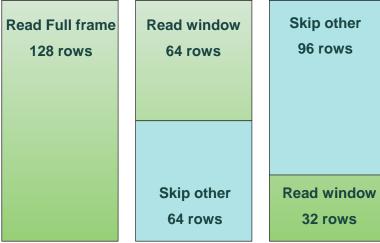

### **DMC OPERATION MODE**

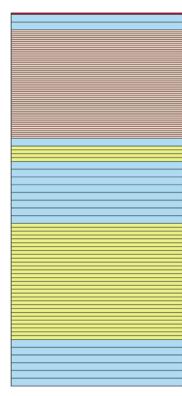

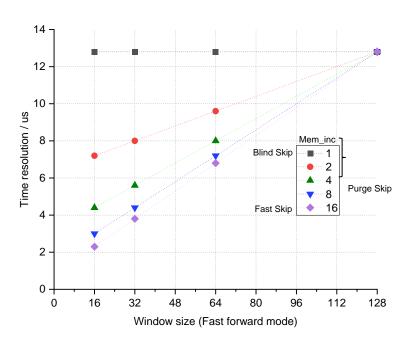

#### **EXAMPLE 3: Window Read**

#### Window Read Example

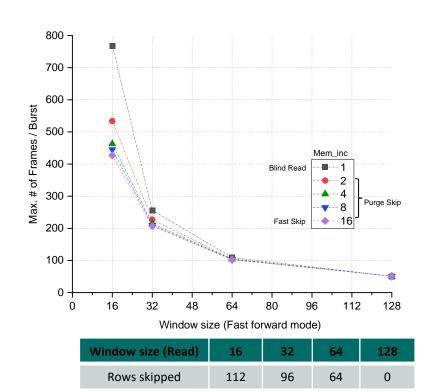

- Instead of reading the full frame, only read Region-of interest (ROI) rows

- Fast forward through the non-ROI rows

- Boost in time resolution

- More frames captured per burst

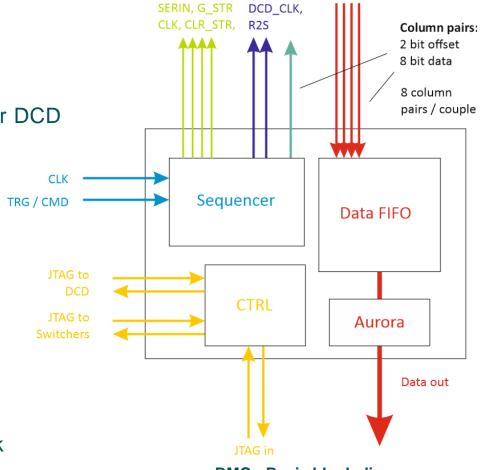

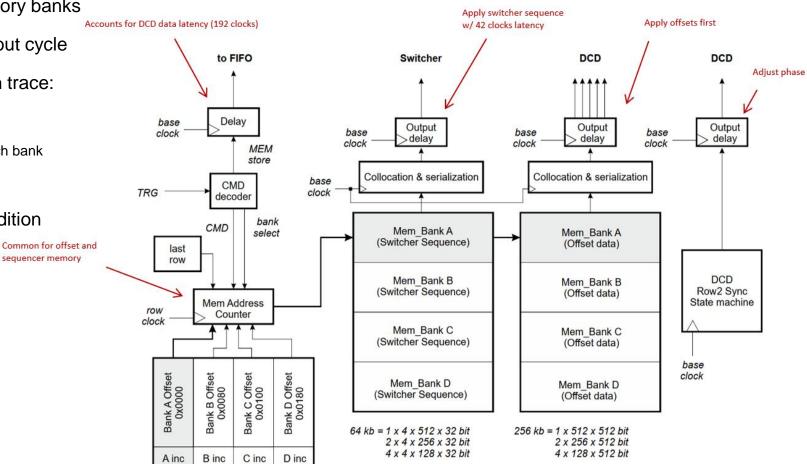

### **DEPFET MOVIE CHIP(DMC 65) – OVERVIEW**

#### COMBINED SEQUENCER / DIGITAL BACKEND / DATA BUFFER IC FOR EDET

#### Sequencer

- Memory banks with selectable memory increment

- Store sequence configurations for Switchers and Offset data for DCD

- Sync signal (R2S) to synchronize DCD digitization

- Decoding of TRG/CMD stream

#### **Control block**

JTAG configuration and PLL generation

#### **Data FIFO**

Data storage in FIFO and Serial Transmission via AURORA link

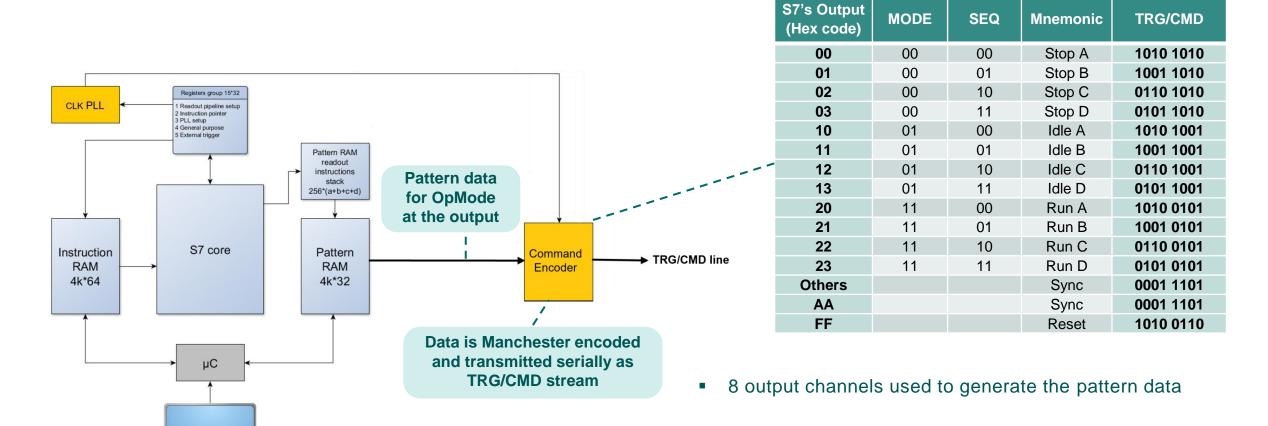

### **DMC OPERATION MODE DATA**

- Implement some simple and complex OpModes using different features of the DMC 65

- 3 constituents of OpMode configuration data

- 1 Command stream (TRG/CMD)

- 2 DMC Sequence data

- 3 Configuration settings

- Sequence of instructions from XU1 SoC

- Switches between different modes and memory banks

- Patterns for Switcher tracks

- Memory addresses and Offset data

- Frame size

- Memory increment and start addresses

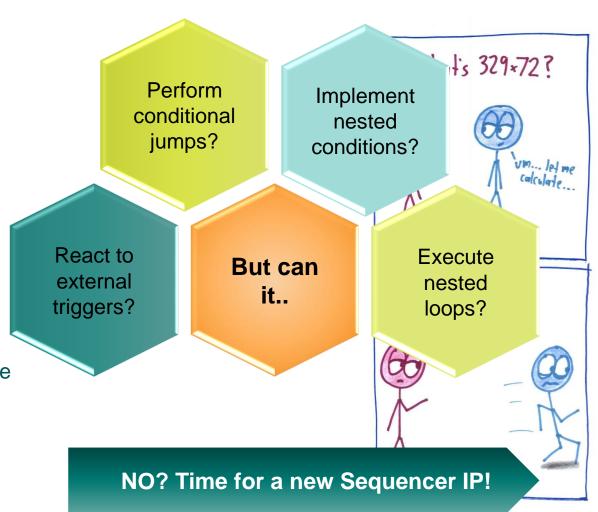

### **DHPT SEQUENCER - BELLE HERITAGE**

#### What we already have:

**DHPT Sequencer**

#### What it can do:

- Basic "Pattern Generator" approach

- Implements sequences as written in its memory

- Only deterministic and repetitive sequences possible

- Memory block is read and translated to TRG/CMD

### **DHPT SEQUENCER - BELLE HERITAGE**

#### What we already have:

**DHPT Sequencer**

#### What it can do:

- Basic "Pattern Generator" approach

- Implements sequences as written in its memory

- Only deterministic and repetitive sequences possible

- Memory block is read and translated to TRG/CMD

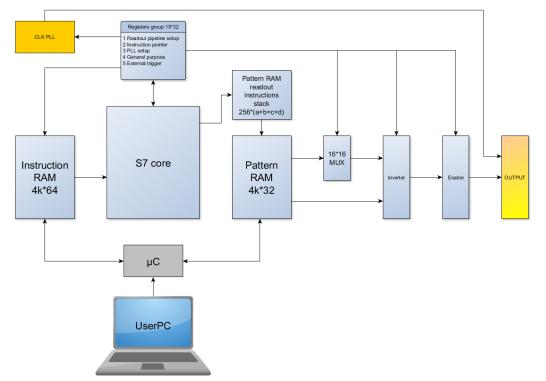

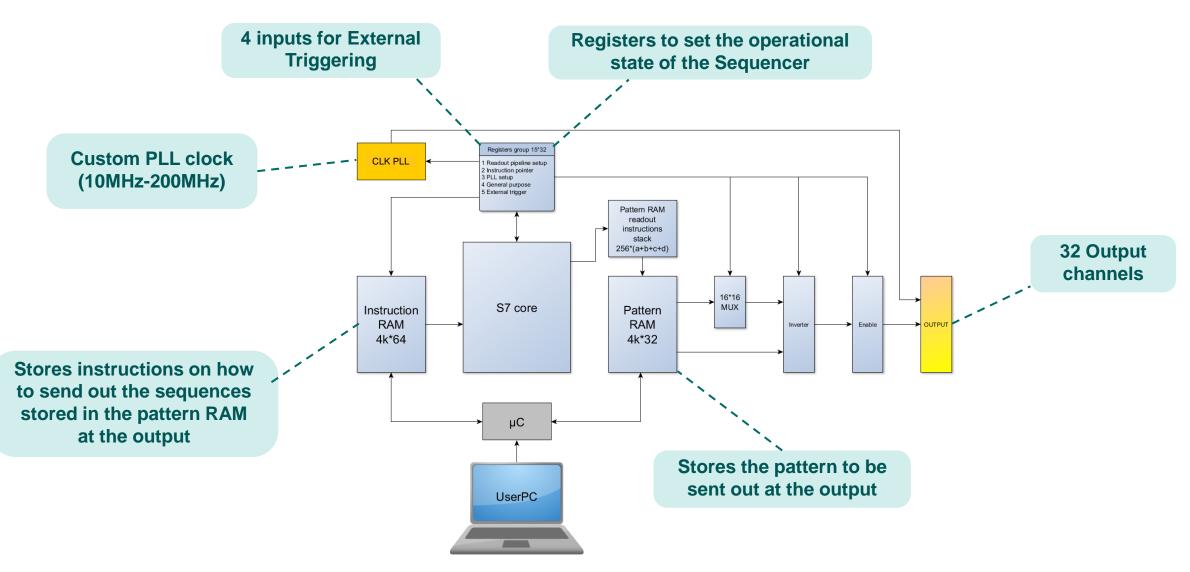

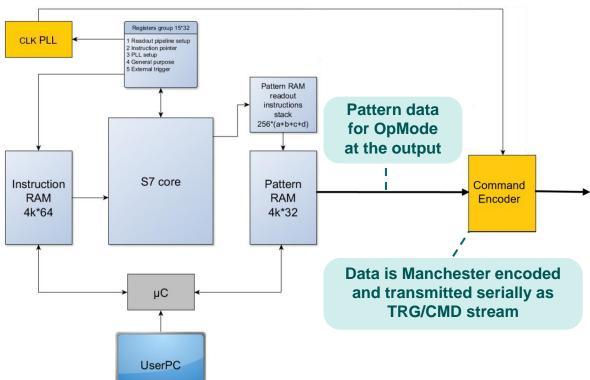

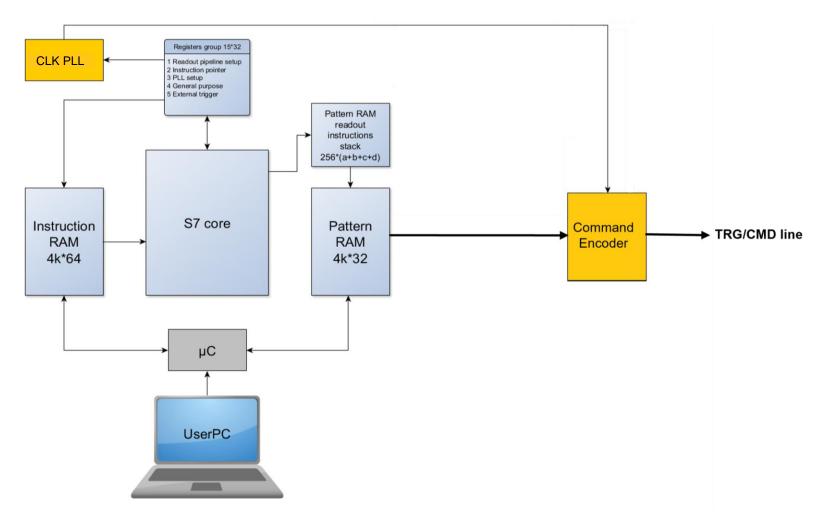

### **SEQUENCER IP DEVELOPMENT**

#### **S7 SEQUENCER**

- Already being used in different projects: FSP, PXD-13...

- Digital scheme with memory blocks, registers, PLL clock

- Outputs data from a Pattern RAM as described by the Instruction RAM

- Various abilities:

- Respond to multiple external triggers

- Implementation of loops/conditional jumps

- Customizable clock/ operating frequency

- Increased flexibility

### **S7 SEQUENCER**

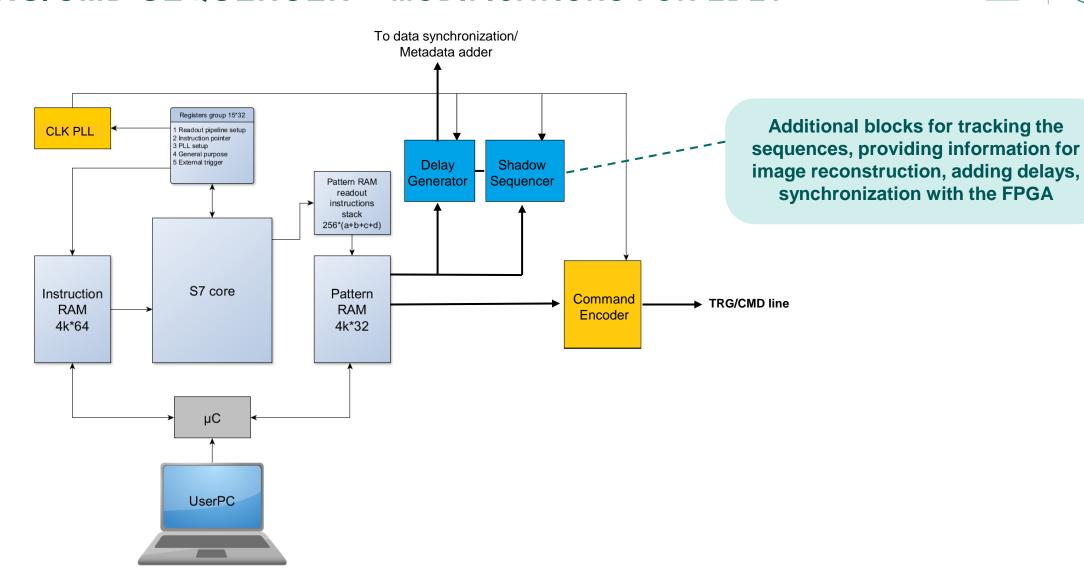

### **S7 SEQUENCER- Modifications for EDET**

#### TRG/CMD SEQUENCER

#### Coding scheme for TRG/CMD line

UserPC

### TRG/CMD SEQUENCER

#### What it can do:

- Controls repetitions, sequence and duration of modes

- Change its ouput in reaction to external triggers

- Supports parking, purging, exposure, windowing

- Variable durations of each state possible

➤ TRG/CMD line

#### What else do we need:

Information for formatting primary stream of data frames

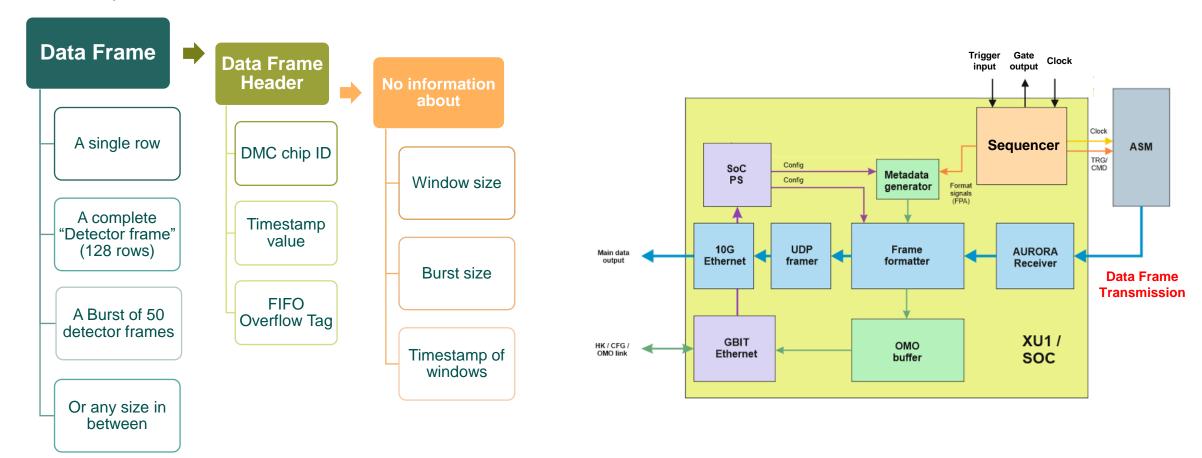

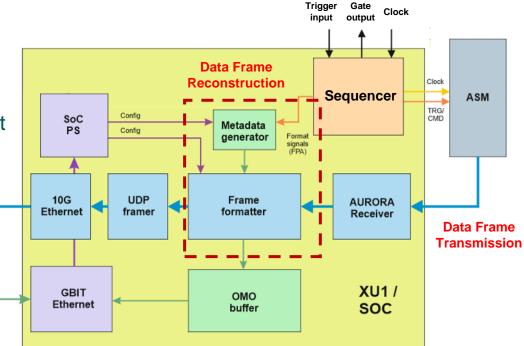

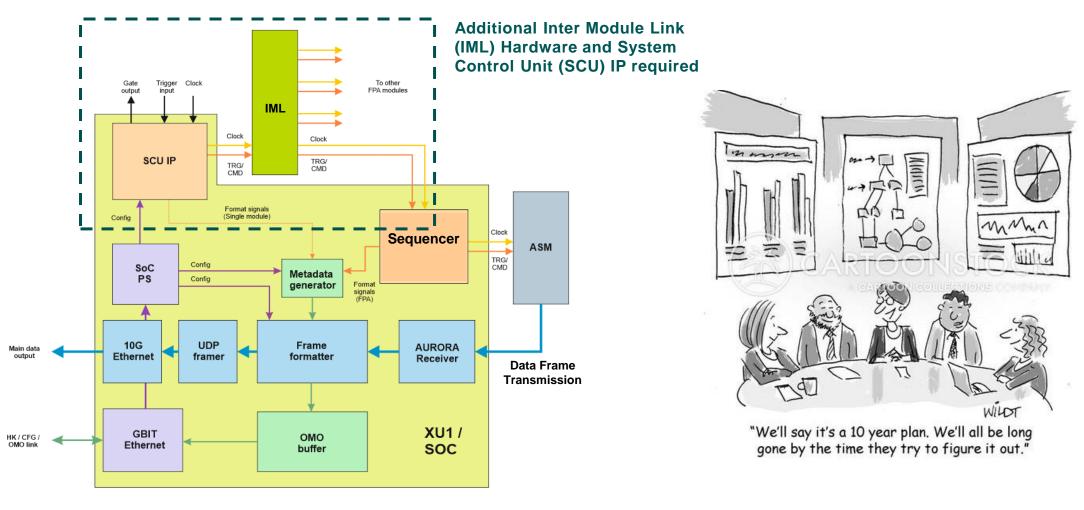

### MODULE IP AND DATA CAPTURING

DMC provides data in the form of AURORA data frames

### MODULE IP AND DATA CAPTURING

DMC provides data in the form of AURORA data frames

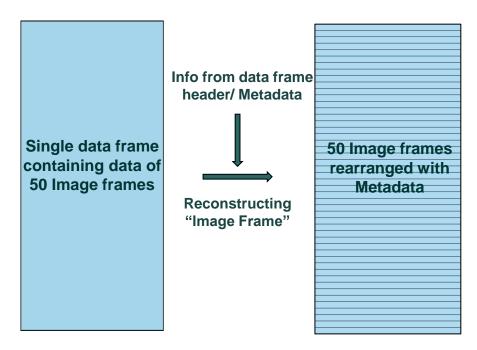

After data acquisition by the SoC, reconstruction of image frames from data frames is necessary

Data from primary aurora stream is to be rearranged to reflect actual image frames and processed with Metadata

Main data

HK / CFG / OMO link

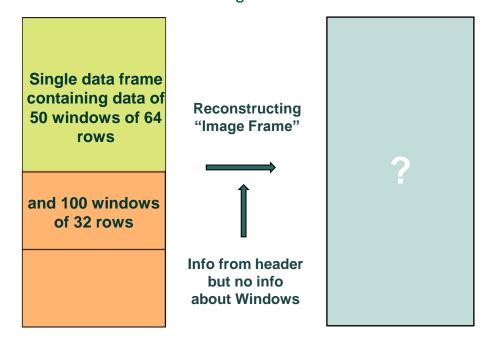

## DATA CAPTURING

### **EXAMPLE**

#### Standard burst of 50 frames

Frame formatter have some information from data frame header

Comparatively simple to rearrange data frames to image frames

#### Window burst of 150 frames

Same number of rows are read as for the standard burst

Receiver does not have any information about windows

Individual windows are not distinguished as discrete frames

### DATA CAPTURING AND RECONSTRUCTION

Added complexity to reconstruct a burst with variable window sizes

#### Sequencer should be able to:

- Keep track of the operation mode

- Follow any changes in the sequence in response to an external trigger

- Convey this information to the Frame Formatter

- Provide information about frame/window/burst size

Accurate reconstruction of primary stream of data frames to stream of image frames requires processing using the format data from the Sequencer

This is also used to generate the **Metadata** to be added to the image frames

Window burst with

17 frames with 128 rows

34 window frames with 64 rows

56 window frames with 32 rows

### TRG/CMD SEQUENCER - MODIFICATIONS FOR EDET

### TRG/CMD SEQUENCER - MODIFICATIONS FOR EDET

### **SUMMARY AND NEXT STEPS**

Upgraded Sequencer IP to support DMC 65 features

Implementation of different OpModes possible

Supports parking, exposure, purging windowing

Reaction to external trigger signals

### Looking ahead:

Experimental testing of the sequencer firmware on the small prototype system

Addition of Metadata to fast data stream during data acquisition

Synchronization of firmware and data capturing routine

### **OUTLOOK - SYSTEM IP**

Expansion of the firmware to operate all four quadrants

### THANK YOU FOR YOUR ATTENTION . . .

Halbleiterlabor der Max-Planck-Gesellschaft

Mishal Rizwan

Isarauenweg 1

85748 Garching bei München

Tel.: +49 (0)89 839400-23

E-Mail: mir@hll.mpg.de

Internet: www.hll.mpg.de

# Comments/ Questions?

#### **BACKUP SLIDES**

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

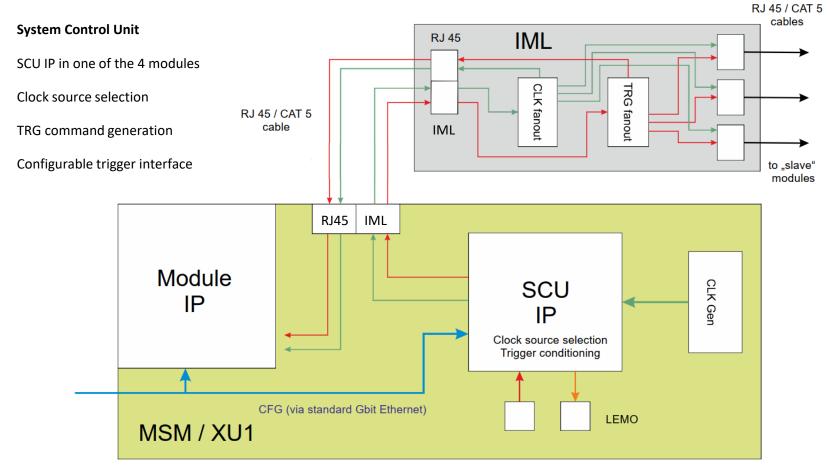

#### "Trigger" in "Gate" out

#### **IML** Hardware

Consists essentially of a two-fold LVDS fanout

Delay adjustment via identical cables

TRG/CMD distribution to other modules

Coordinated operation of 4 modules on one FPA

Distribution of clock and trigger signals

- Up to four independently selectable pattern memory banks

- Individually commandable for every 100 ns readout cycle

- •Stop mode with individual parameter set for each trace:

- ·Loop / Freeze mode setting

- •Freeze can be enabled for every track individually for each bank

- •Bank dependent freeze position

- Programmable address offsets after RESET condition

- Programmable return address

- Flexible use of memory banks

- ·Bank individual memory increment for

- Fast purging

- •Fast forwarding (e.g. during windowing)

### **WINDOW MODE**

- Tradeoff between time resolution and movie length (max. # of frames/burst)

- Fastest read (2.3us) for the smallest window size for mem\_inc = 16 and window size = 1