## PXD<->DAQ interface

R.Itoh, KEK

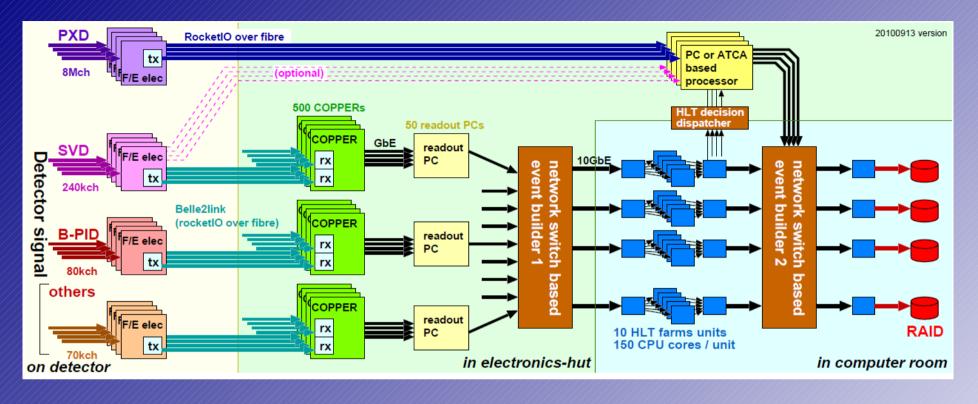

## Integration of Pixel Detector (PXD) readout

\* Track parameters are obtained in High Level Trigger and sent to PXD readout processor.

\* Only the hits associated with tracks in HLT-passed events are sent.

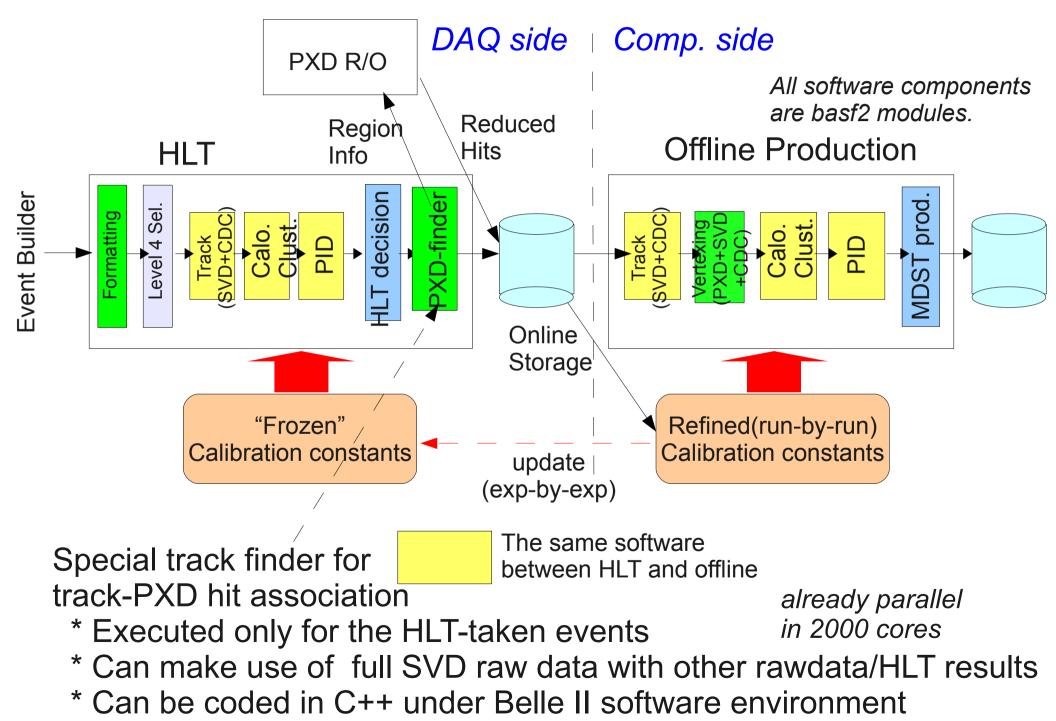

## Event Reconstruction Chain at Belle II

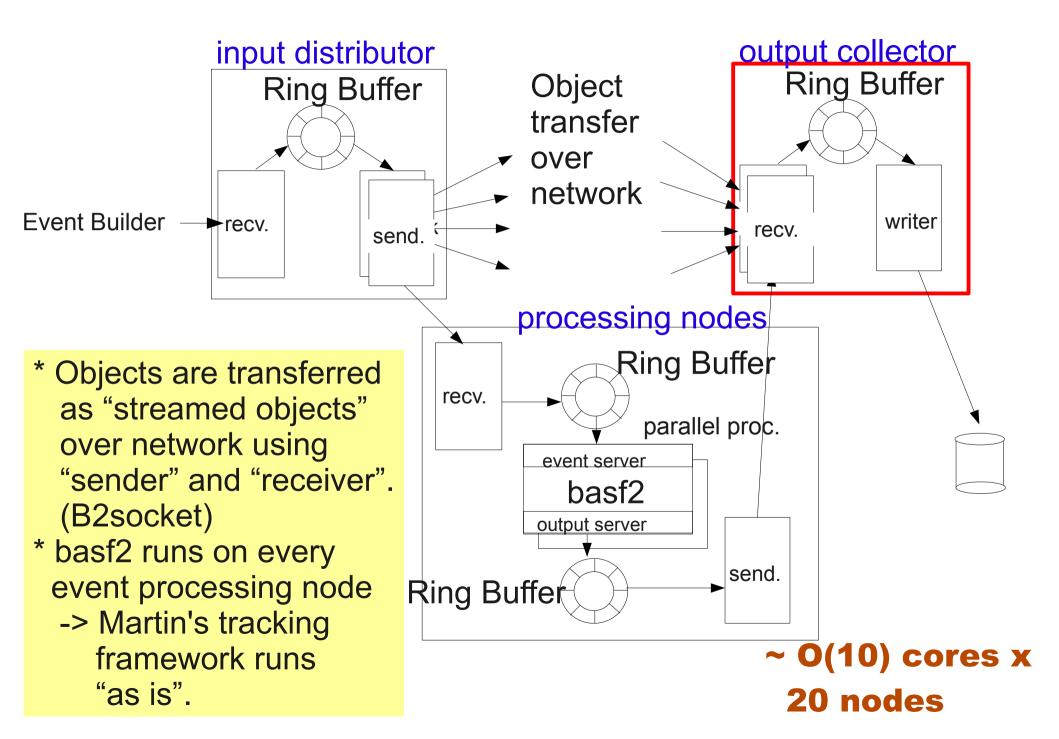

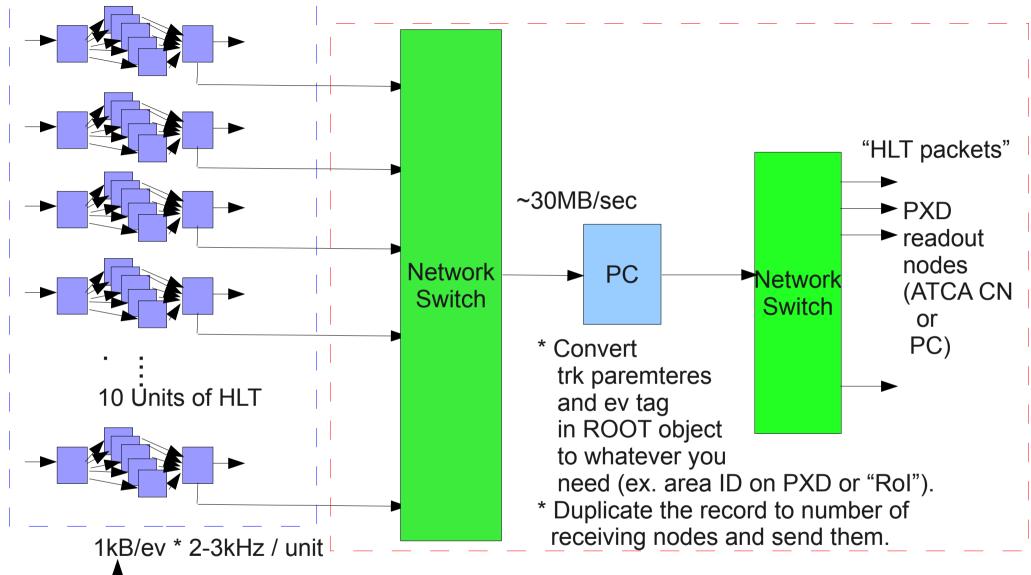

#### Software framework of HLT (1 unit) = pbasf2 for PC cluster

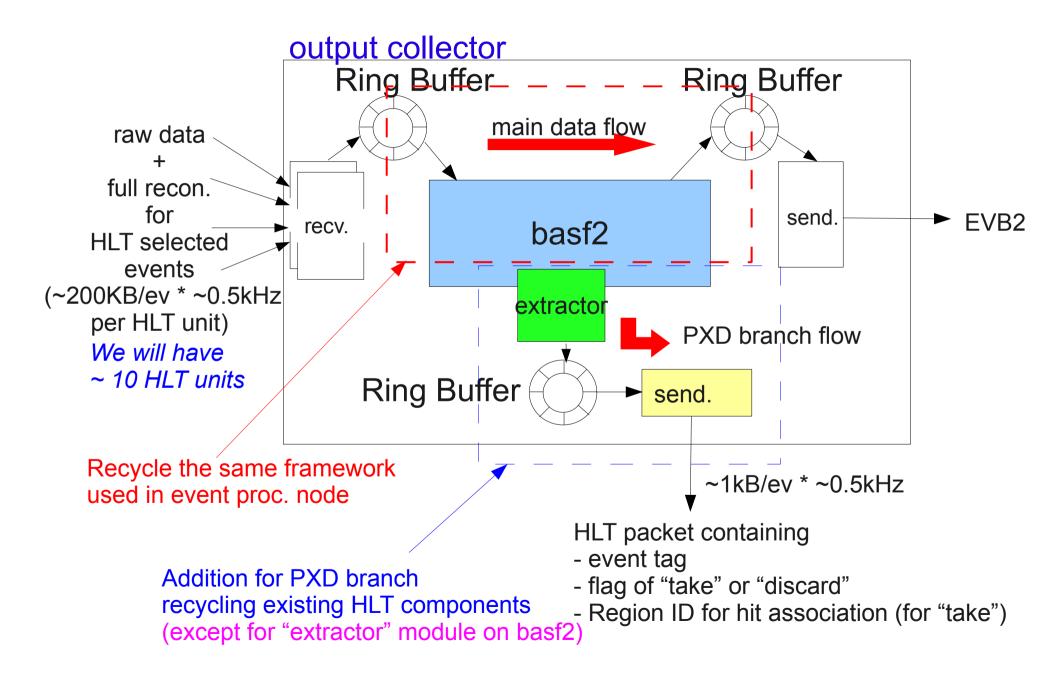

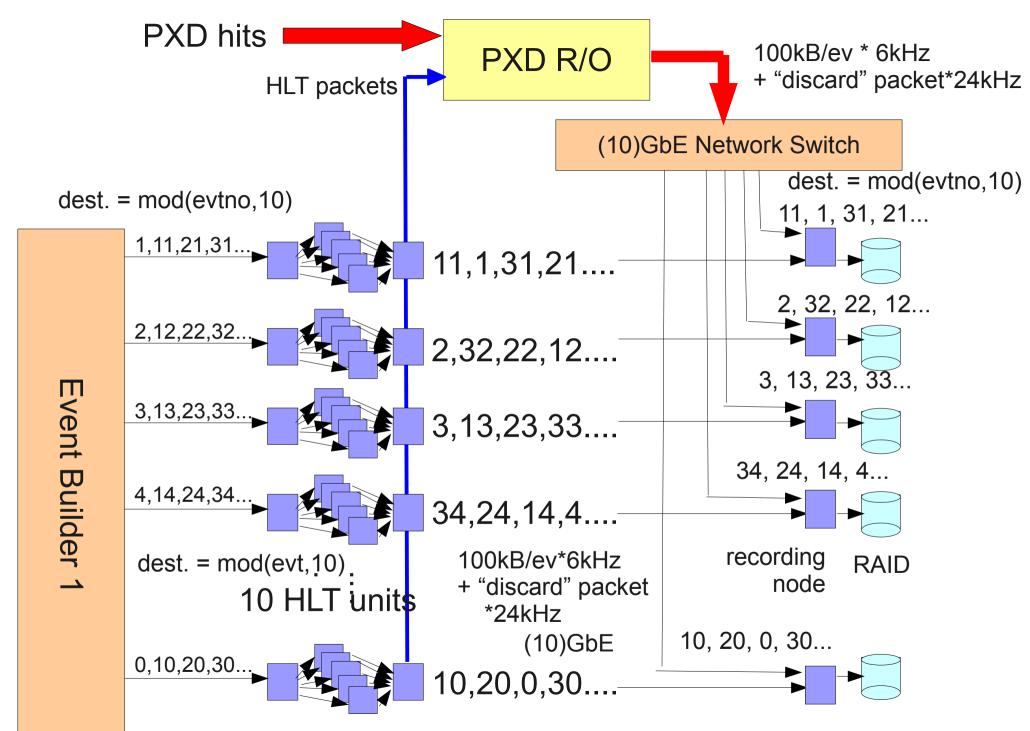

#### **HLT-PXD** interface

"HLT packets" Passed events:

evtag + track parameters Discarded events:

evtag + "discarded" flag

- Event sequence of HLT packets are disordered because of parallel processing.

=> Could be a problem in further processing (track-hit matching, 2<sup>nd</sup> level event building) Processing framework in PXD R/O box

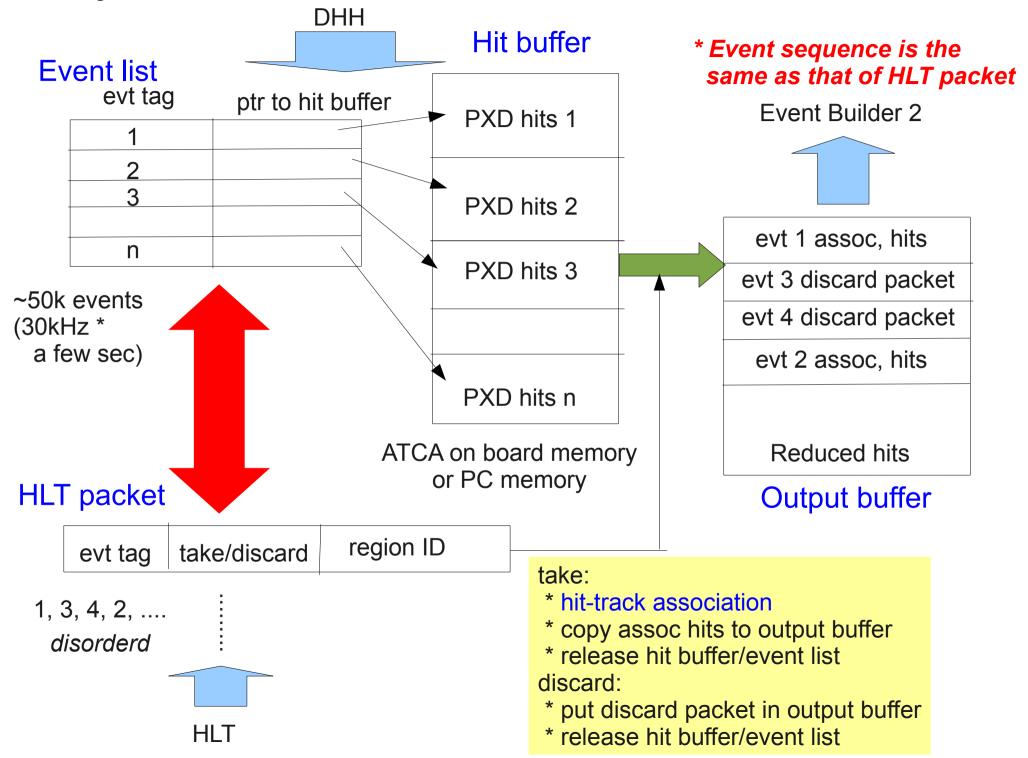

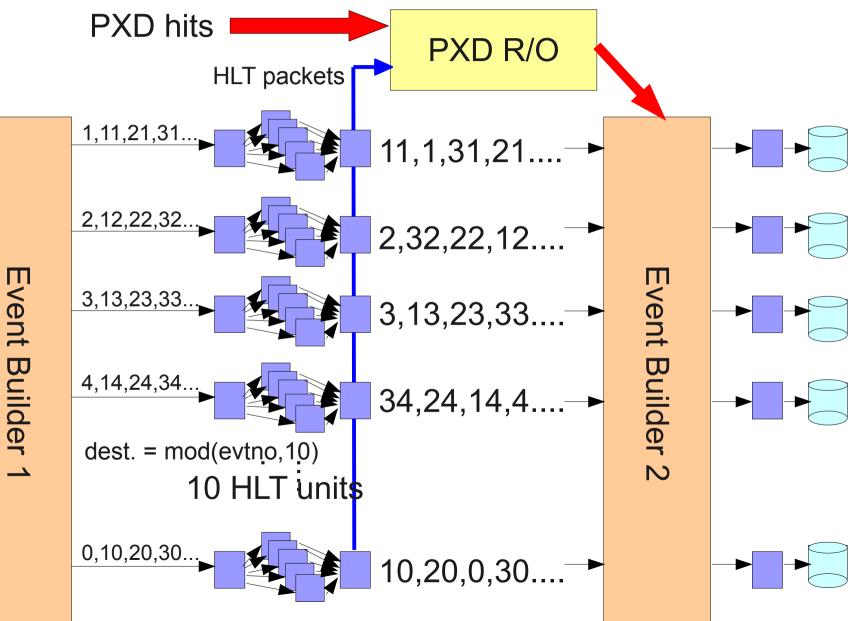

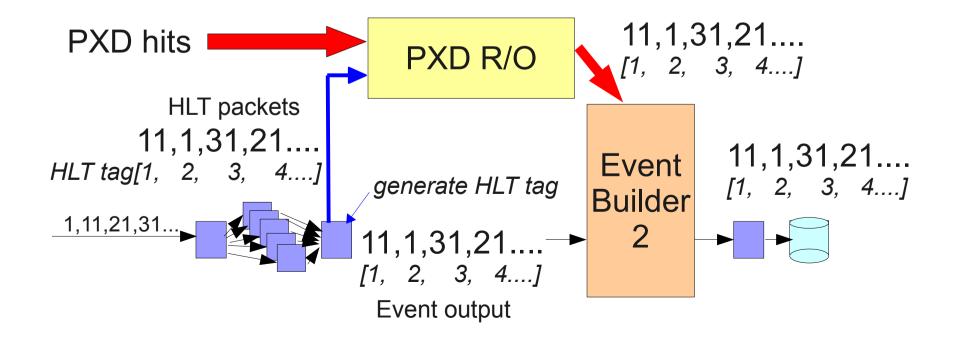

## Idea on 2<sup>nd</sup> level event building (EVB2)

- Event sequence from HLT is disordered.

- Do we need to "sort" events for the 2<sup>nd</sup> level event building?

HLT sends the event output to EVB2 and HLT packets to PXD R/O in the same order, although event tag is disordered.

Idea: place new "HLT tag" both in "event output" and "HLT packet" and build event using the tag at EVB2.

- Processing on PXD R/O does not break the ordering of HLT packets.

No sorting is required although the event tag is disordered in recording RAID.

\* Event disordering in output RAID is harmless!

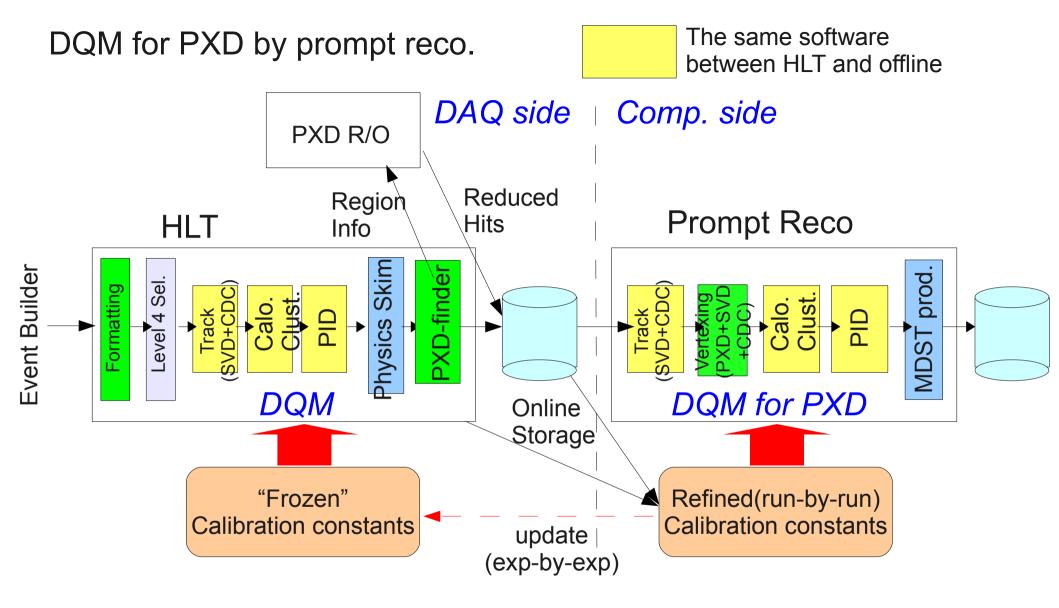

- \* Idea is, to run offline reconstruction instead of raw data copy right after a run is completed.

- \* DQM modules can be inserted in Prompt Reco script.

- \* Since full event reconstruction with PXD is supposed to be done in prompt reco, detailed monitoring of PXD data quality even at physics level becomes possible.

## Discussion

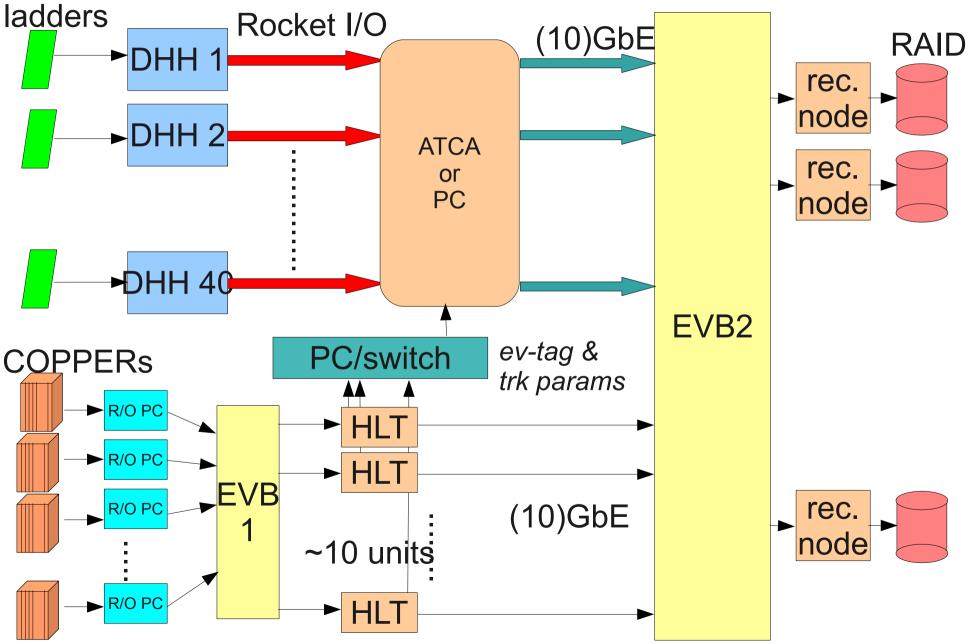

- HLT is supposed to provide HLT trigger decision with track information for PXD readout box in any cases of PXD R/O options (ATCA(baseline and challenge), and PC).

- PXD-specialized tracking/Rol generation can be done on HLT using full SVD raw data + other detector info + HLT processing results. -> very versatile. Standard C++ coding under Belle II env.

- The "event disordering problem" can be solved by considering the algorithm of event matching with HLT packets in PXD readout box. -> Is it OK?

- Regardless of having ATCA based tracking or not, HLT decision is fed into PXD readout box and it is supposed that all PXD data matched with HLT tag are sent to 2<sup>nd</sup> level event builder.

- How do we implement DQM for PXD?

- \* Is it possible to implement the function in ATCA board?

- \* Full event monitoring after 2<sup>nd</sup> level event building is difficult.

- \* Prompt Reco is required for detailed monitoring.

# Backup Slides

## **PXD** integration

### PXD

Do we really need 4GB/DHH for data buffering?

- Average HLT latency for an event is expected to be less than 1 sec as shown in previous meeting.

- Thanks to parallel processing, the HLT packets for events with shorter processing latency come faster. Not necessary to wait for the 5 sec latency for one particular problematic event.

- The PXD hit buffer is supposed to be released immediately after the hit-track association (if the algorithm shown in previous slide is used).

## We don't have to buffer every event for 5sec.

- \* It seems the required buffer size is much smaller than 30kHz\*5sec\*600MB/sec.

- <- This size is necessary only when 5 sec latency is consumed by all of ~2000 cores in HLT at one time. ==> very rare!

- \* We need a simple MC study to estimate the actual size.

- \* Sophisticated memory management scheme is required on FPGA in case of Option 12, anyway.