LMU München - Excellence Cluster Universe

# UPDATE on PS development

Stefan Rummel

#### Overview

- Organization

- Updates on requirements

- Engineering aspects

- System overview

- Multichannel prototype

- PS form factor & space needs

- HV channel

- Outlook

- Group from Krakow interested to join the PS development effort

- Started with hardware tests

- Will look into Overvoltage protection / Hardware safety system

- Organizing a longer stay of a designer in Munich

- Manpower

- More and more students are interested to work in our group

- Helpful support for testing & Labview programming

- Firmware development is ongoing

- $\rightarrow$  See my next talk

## Update on requirements

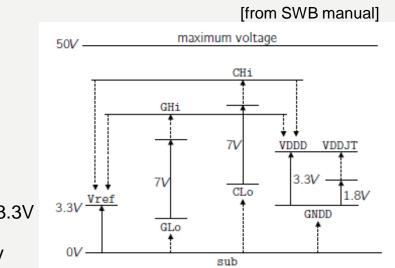

- New input from HLL  $\rightarrow$  have to be prepared for threshold voltage shift

- Segmentation of MOS-structures

- 3 Gate\_On 3 CCG voltages

- Range of voltages has increased (CCG, Gate)

- Ability to put Gate\_On below GND

- Gate\_OFF needs bipolar output (~ +5 to -5V)

$\rightarrow$ SW\_SUBS can't be put on GND anymore

Old biasing: New biasing: VREF : SW\_DVDD VREF : -10V + 3.3V SW\_SUB : GND SW\_SUB : -10V

- Need 6 additional voltages

- With this scheme steering voltages can be easily applied with respect to source

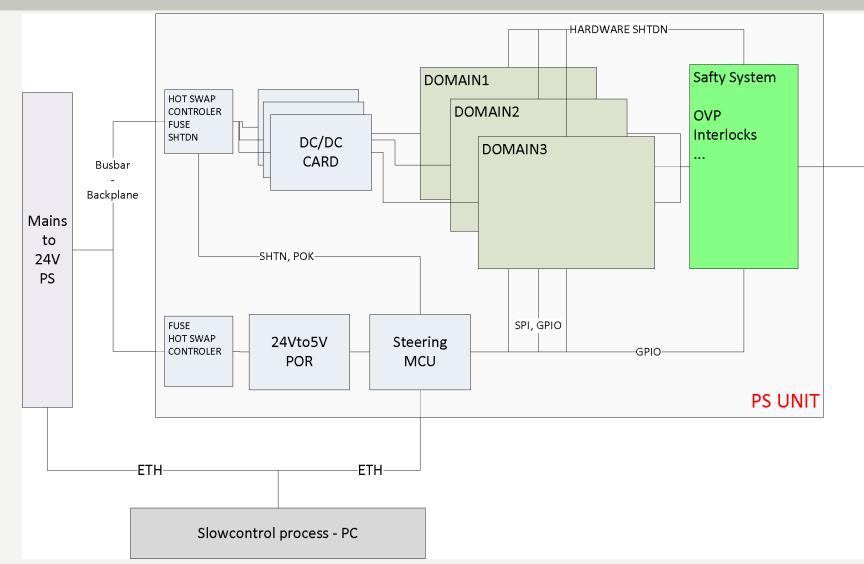

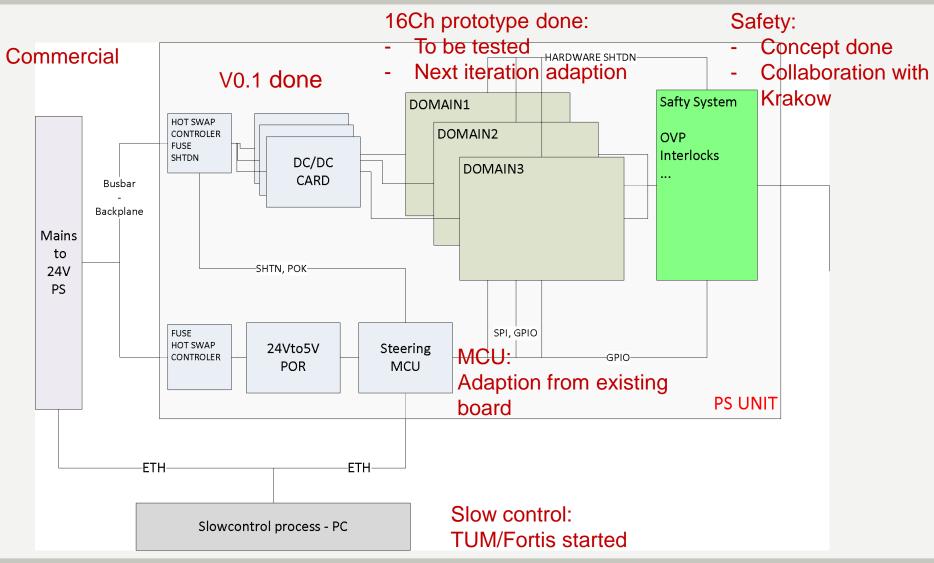

## System overview

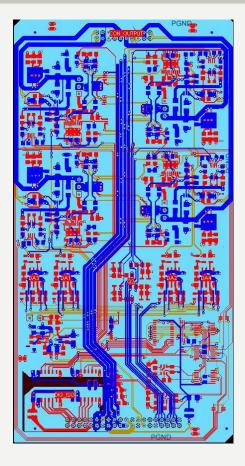

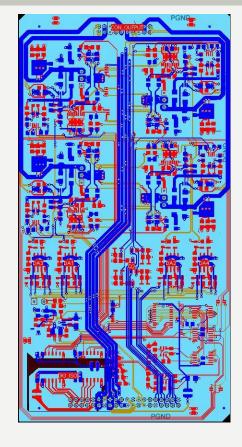

Design of multichannel prototype finished - "Analog Prototype"

prototype

- Digital interface via DAC-PCI card and ADC

- Organized in 4 modules with 4 channels

- 4 layer PCB, 75\*145mm2

- Flexible design:

- With/without remote sensing

- Positive- or Negative Output, sink or source

- Flexible over current protection

- Clear\_OFF can be derived form Clear\_On

- Monitoring of currents and voltages

- Status outputs

Compact channel (~9cm2)

Regulator (~2.5 cm) + pass element (.5cm2)

prototype

- Space for heat sink (~2cm2)

- Monitoring (~2.5cm2)

- Current sense

- Voltage sense

- Current source @ each output (.8cm2)

- Allows the regulator to sink current

- Interesting for DCD\_AVDD, steering voltages

- Auxiliary circuitry

- Digital isolators (now for steering of MUX, later for SPI)

- Range adjustment for the DAC output

- Common shutdown

- ightarrow Layout is there and will serve as baseline for the next iteration

- ightarrow Based on this we can make a first estimate on system-size

- $\rightarrow$  After commissioning first tests with DEPFET-system can be done

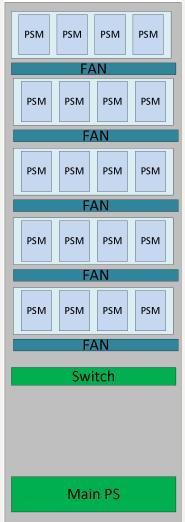

- Baseline for electro-mechanics

- $\rightarrow$  Use of standard 19" components

- $\rightarrow$  Good HF properties

- 24V Main power supply (e.g. TDK-Lambda GENSYS, 2U)

- 3 kW (**E** DC/DC, **E** regulator, auxiliary)

- 24V power distribution via bus bar + backplane

- PS modules standard cassettes 6HE-21TE  $\rightarrow$  10 crates

- Cooling 19" fan unit 1U  $\rightarrow$  1 per crate

- Connectivity ETH Switch ~2U

- Cooling interlock via backplane

- Connectivity (ETH, JTAG, Detector output) on front-side of PS-module

- $\rightarrow$  First estimate: 2 two racks more precise estimate by Autumn

19" Rack – 220cm

## HV - channel

- First prototype ready & tested

- HV DC/DC converter

- Shunt post regulator

- Specifications

- 0-200V output settable

- 1mA output current

- Precise current and voltage monitoring

- Performance

- Noise 2.2mVrms (0.1Hz-20MHz)

- Still switching remnants visible 8mVpp

- $\rightarrow$ Second iteration with better filtering should solve this problem

| c1<br> |                        |              |     |                            |                                                                                                                 |                       | LeCroy            |

|--------|------------------------|--------------|-----|----------------------------|-----------------------------------------------------------------------------------------------------------------|-----------------------|-------------------|

| C2 17  | AND MADE OF A PARTY OF |              |     | here the a strength of the | al forder blede van de blede de state de blede state de blede state de state de state de state de state de stat |                       | The second second |

|        |                        |              |     |                            |                                                                                                                 |                       |                   |

|        |                        |              |     |                            |                                                                                                                 |                       |                   |

|        |                        |              |     | <u> </u>                   |                                                                                                                 |                       |                   |

| Mea    | sure                   | P1:sdev(C1)  | P2: | P3:mean(C2)                | P4:                                                                                                             | P5:                   | P6:               |

| valu   | е                      | 2.18 mV      |     | -127.5 V                   |                                                                                                                 |                       |                   |

| mea    | n                      | 2.2064 mV    |     | -127.491 V                 |                                                                                                                 |                       |                   |

| min    |                        | 2.12 mV      |     | -127.5 V                   |                                                                                                                 |                       |                   |

| max    |                        | 2.35 mV      |     | -127.5 V                   |                                                                                                                 |                       |                   |

| sdev   |                        | 36.2 µV      |     | 17 mV                      |                                                                                                                 |                       |                   |

| num    |                        | 525          |     | 525                        |                                                                                                                 |                       |                   |

| statu  |                        | 1            |     | 1                          |                                                                                                                 |                       |                   |

| C1     | BwLIDC1M               | 2 BWL DC1M   |     |                            | 1                                                                                                               | Timebase 500 µs Trig  | ger <b>CilDC</b>  |

|        | 5.00 mV/div            | 50.0 V/div   |     |                            |                                                                                                                 | 5.00 ms/div Auto      |                   |

|        | 18.20 mV               | 0.0 V offset |     |                            |                                                                                                                 | 1.00 MS 20 MS/s Edg   |                   |

| L      | -15.37 mV 1            |              |     |                            |                                                                                                                 |                       | -50.00 µs         |

| ſ      | -15.23 mV 1            |              |     |                            |                                                                                                                 | X2= -75.00μs 1/ΔX= -3 |                   |

| Δy     | 140 μV <mark>2</mark>  | ∆y 600 mV    |     |                            |                                                                                                                 | ла толооро пане л     | 20.00 10 12       |

## Next steps

- Next steps

- Integrate DAC/ADC into Multichannel prototype

- $\rightarrow$  Adaption of existing design

- MCU Steering card

- ightarrow Adaption of evaluation board

- Hardware safety OVP

- $\rightarrow$  Krakow

- Since our last Ringberg meeting in May 2009 we made significant progress

- Full scale electrical prototype by end of this year