# Dünne Silizium-Sensoren und 3D-Integration für den ATLAS Pixel-Detektor am HL-LHC

Philipp Weigell<sup>a</sup>,

L. Andricek<sup>a,b</sup>, A. Macchiolo<sup>a</sup>,

H.-G. Moser<sup>a,b</sup>, R. Nisius<sup>a</sup> und R.-H. Richter<sup>a,b</sup>

<sup>a</sup>Max-Planck-Institut für Physik, <sup>b</sup>Max-Planck-Institut Halbleiterlabor

In Kollaboration mit

FIMILI

### Zukunft des ATLAS Inneren Detektors

#### Eckpunkte

- Zweistufiger Ausbau:

- Insertable B-Layer (IBL) ~2013/4

- Ersatz des Inneren Detektors je nach Performanz

~2018 (Wird 2013 entschieden)

- Luminosität:  $(2-3) \cdot 10^{34} 10^{35} / (\text{cm}^2\text{s})$

- $\Rightarrow$  Strahlenbelastung:  $\phi_{eq} \approx 10^{15} 2 \cdot 10^{16} \, n_{eq} / cm^2$

#### Strategie

- Sensortechnologie offen für Upgrades nach IBL:

n-in-p exzellenter Kandidat für große Flächen.

- Einseitiger Prozess → niedrigere Kosten.

- Strahlenhärte: wie n-in-n

- Kompaktes Design

- Weniger Vielfachstreuung

- Größere aktive Fläche

- F&E: Derzeitiger ATLAS Auslesechip

### **Unser Pixel Modulkonzept**

### Aktuelles Design

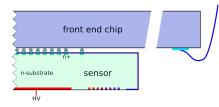

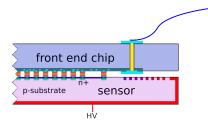

#### Dünne Sensoren + ICV-SLID

#### Vier neue Technologien

- N-in-p

- Geringere Produktionskosten

- Dünne Sensoren (MPP-HLL Prozess)

- Höhere

Ladungssammlungseffizienzen

(CCE) nach Bestrahlung

- Weniger Vielfachstreuung

- SLID: Solid Liquid Inter-Diffusion

- Ermöglicht vertikale Integration

- Separation von analogen und digitalen Teilen (mit ICV)

- ICV: Inter-Chip-Vias

- Kompakter: "Balkon" zur Signalextraktion nicht benötigt

- Vergrößerung der aktiven Fläche

### Dünne Sensoren Prozess am MPP/HLL

Implant backside

on sensor

3. Thin sensor side to desired thickness

Process on top side

Structure resist, etch backside up to oxide

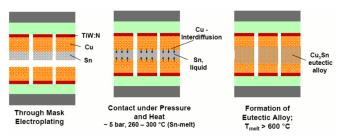

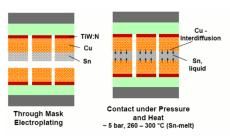

### SLID: Solid Liquid Inter-Diffusion

#### Alternative zum Bump Bonding

#### Pros

- Vertikale Integration möglich (T<sub>schmelz</sub>).

- Beliebige Geometrien und kleinere Abstände möglich.

- Weniger Prozessschritte → geringere Kosten.

- Wafer-zu-Wafer und Chip-zu-Wafer möglich.

#### Cons

- Planarität von 1 μm benötigt.

- Homogener Druck benötigt.

- Kein "rework" möglich.

- Chip-zu-Chip noch nicht möglich.

Page 5

### SLID: Solid Liquid Inter-Diffusion

**Eutectic Allov:**

T<sub>melt</sub> > 600 °C

Alternative zum Bump Bonding

#### Pros

- Vertikale Integration möglich (T<sub>schmelz</sub>).

- Beliebige Geometrien und kleinere Abstände möglich.

- Weniger Prozessschritte → geringere Kosten.

- Wafer-zu-Wafer und Chip-zu-Wafer möglich.

#### Cons

- Planarität von 1  $\mu$ m benötigt.

- Homogener Druck benötigt.

- Kein "rework" möglich.

- Chip-zu-Chip noch nicht möglich.

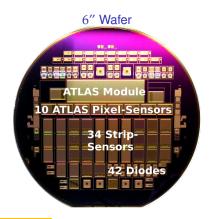

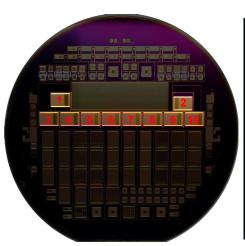

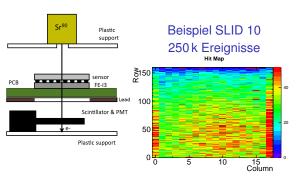

### Chip-zu-Wafer

### Quellenmessungen

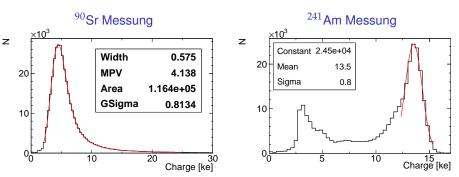

- $^{90}$ Sr ( $\beta$ ) und  $^{241}$ Am ( $\gamma$ ) Quellen zur Bestimmung der Ladungssammlung

- Trigger

Extern Via Szintillator (<sup>90</sup>Sr) Intern Chip-Trigger (<sup>241</sup>Am)

### Eigenschaften vor Bestrahlung

- Leckströme unter 100 nA für alle Module.

- $\bullet\,$  Durchbruchspannungen über 120 V vollständige Verarmung  ${\sim}40$  V.

- Schwellen zwischen 2500 und 3500 e eingestellt.

- Ladungen entsprechen im Rahmen der Kalibrationsunsicherheiten den Erwartungen für 75  $\mu$ m Dicke.

- Die Ladungssammlung ist homogen für alle Module.

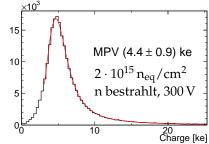

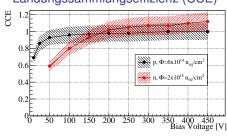

### Ladungssammlung nach Bestrahlung

### Bestrahlungen

• Ljubljana:  $2 \cdot 10^{15} \, n_{eq}/cm^2$

• KIT:  $6 \cdot 10^{14} \, \text{n}_{\text{eq}} / \text{cm}^2$

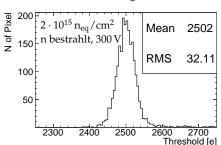

• Schwelle: 2500 e Rauschen: 170 e

Für beide Fluenzen volle CCE erreichbar

(Band: korrelierte Unsicherheiten)

## <sup>90</sup>Sr Messungen

#### Tuning

### Landungssammlungseffizienz (CCE)

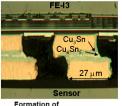

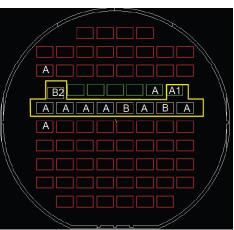

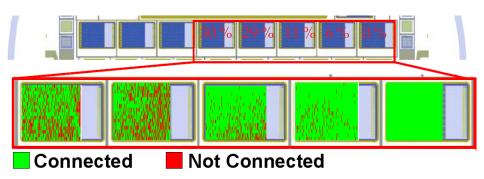

### Überblick über die SLID-Verbindungseffizienzen

- Zahl der unverbundenen Kanäle steigt zur Wafermitte auf Grund nicht perfekt geöffneter BCB-Passivierung.

- Stabil nach Bestrahlung bis zu  $2 \cdot 10^{15}$  n<sub>eq</sub>/cm<sup>2</sup> und thermischen Zyklen.

### Grund: BCB-Passivierungs-Öffnung

Die Passivierung muss geöffnet werden, um eine Verbindung zwischen Chip und Sensor zu ermöglichen. Dieser Prozessschritt ist nicht vollständig erfolgt.

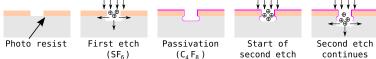

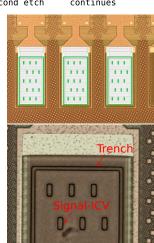

### Inter-Chip Vias (ICV) auf ATLAS Chips

- Via-Ätzung im Bosch-Prozess.

- Wolframfüllung der Vias

- Dünnen des Chips zur Zieldicke.

- SLID-Verbindung.

- Erste Ätzversuche auf Test-Wafer erfolgreich.

- Mai: Ätzen des Chip-Wafers

EMFT erreicht aspect ratios von: 8:1 (Wichtig für Einzelpixelverbindungen).

### Zusammenfassung & Pläne

#### Zusammenfassung

- Erste Single Chip Module mit SLID Verbindungen zeigen gute Eigenschaften:

- Geringe Leckströme & hohe Durchbruchspannungen

- Gesammelte Ladung wie erwartet

- Hohes CCE nach Bestrahlung

- Trend unverbundener Kanäle zur Wafermitte auf Grund von fehlenden BCB-Passivierungs-Öffnungen → d.h. nicht auf Grund der Verbindungstechnologie!

- Erste ICVs auf Test-Wafer erfolgreich

#### Pläne

- ullet Bestrahlung bis zu  $\phi=10^{16}\,\mathrm{n_{eq/cm^2}}$

- Demonstrationsmodul mit SLID und ICV