### DHH Test Beam Report

#### Dima Levit

Physik Department E18 - Technische Universität München

#### DHH Test Beam Report June 14th, 2013

supported by: Maier-Leibnitz-Labor der TU und LMU München, Cluster of Excellence: Origin and Structure of the Universe,

BMBF

Bundesministerium für Bildung und Forschung

Hardware Problems

**Firmware Problems**

**Slow Control**

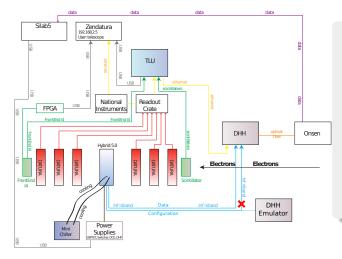

- in operation 10.05-12.05

- recorded approx.

2.5 Mio events

- mostly 8 DHP frames per trigger

- DHP interface: 1.6 Gbps Aurora

- ONSEN interface: 3.125 Gbps Aurora

#### Hardware Problems

**Firmware Problems**

**Slow Control**

## Hardware Problems

- Broken Ethernet port on one of DHH card out of three taken to DESY

- Wrong deserializer clock for DHP

- used 160 MHz instead of 152.652 MHz

- correct clock was generated by programmable clock synthesizer, source of the DHP reference clock

- Problem with configuration of the clock synthesizer over I2C (probably not a hardware problem)

- power cycle required to correct the bug

- rare bug: only few times spotted before

Hardware Problems

#### **Firmware Problems**

**Slow Control**

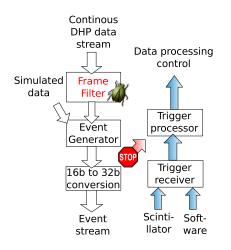

## 🛞 Data Processing

#### Issues with Frame Filter

- Runs 254-273: double DHP frame headers hint at data loss

- fixed in newer runs

- DHH header corruption if 1 clk cycle between DHP frames

- can be fixed in offline software

- firmware bug fixed

## 🛞 Data Processing

#### **Issues with Frame Filter**

- Runs 254-273: double DHP frame headers hint at data loss

- fixed in newer runs

- DHH header corruption if 1 clk cycle between DHP frames

- can be fixed in offline software

- firmware bug fixed

#### Firmware Issues

- Last DHH firmware skips TLU triggers

- will be investigated at HLL

- Wrong event size in some events

- fixed in the frame generator module

- I2C master replaced with OpenCores.org implementation

- no errors for a test over week-end

- Order of DHP words in 32b DHH words changed in newer firmware

- FPGA temperature measurements bug

Hardware Problems

**Firmware Problems**

#### Slow Control

- EPICS app as JTAG and IPBus driver

- IPBus: DHH control

- JTAG: DHP and DCDB control

## Slow Control Issues

#### • DHP DCDB configuration issue

- DCDB switch on/off via JTAG register works (power consumption increases)

- data scrambled in full frame data

- o possible causes:

- DHP-DCDB JTAG chain switched off if not used. Always on with DHH emulator

- wrong configuration parameter

- under investigation at the HLL

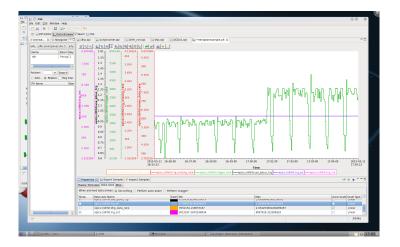

## GUI Examples

Technische Universität München

| ] 🗈 🗟 ] 🥂 ] 🔯 ] 🖉 ]                                                                                                                                                                                                                                                                                                                                           | 🚰 🛛 🖗 🖉 🖉                                               | R R 100%                                                                                                                                | • (>* )                                                                                       |   |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|---|-----|

| 📑 🔛 OPI Runtime                                                                                                                                                                                                                                                                                                                                               |                                                         |                                                                                                                                         |                                                                                               |   |     |

| 🚰 dhp.opi 🛛 🔛 DHH_ctrl.op                                                                                                                                                                                                                                                                                                                                     | pi 🕄 🕌 DHH_ADV.opi                                      |                                                                                                                                         |                                                                                               |   | - e |

| DHP Channel Up<br>DHP PLL locked<br>ONSEN Channel Up<br>ONSEN PLL locked                                                                                                                                                                                                                                                                                      | Enable trigger                                          | Short RST                                                                                                                               | Read full frame                                                                               |   |     |

| TLU Settir                                                                                                                                                                                                                                                                                                                                                    | ngs                                                     | DHP Trigg                                                                                                                               | er Settings                                                                                   |   |     |

| Mas bis<br>1327UOL<br>1327UOL<br>Clock slow down factor<br>Clock slow down factor<br>Def Alan coulter<br>Def Alan coulter<br>Def Alan coulter<br>Def Alan coulter<br>Def Alan coulter<br>OrdEN das coulter | 1.07199004E8<br>1451987<br>544,552 Bps<br>265019<br>876 | Trigger wildth<br>Trigger delay<br>FCK Length<br>Timeout<br>FCK trobe wildt<br>Interest<br>CK Didder<br>DCDB Settlings<br>DHP Settlings | 4.099 ±<br>9 ±<br>512 ±<br>502 ±<br>5 ±<br>0 ±<br>0 ±<br>0 ±<br>0 ±<br>0 ±<br>0 ±<br>0 ±<br>0 |   |     |

| 0*                                                                                                                                                                                                                                                                                                                                                            |                                                         |                                                                                                                                         |                                                                                               | ] | ]   |

## GUI Examples

Technische Universität München

| mode TEST                                                                                                                                                                                                                                                           | TEST                                                                                                                                 | chip id lo c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                                                                                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|

| Disable Channel                                                                                                                                                                                                                                                     |                                                                                                                                      | swenable 🗸 🖌                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                           |

| Preventional solution correction<br>invert input values<br>send buf data only<br>dcd use right<br>latency<br>last row<br>rand gen on out fifo<br>rame sync proc dly<br>row2 sync dcd clk dly<br>row2 sync dcd clk dly<br>row offset<br>pedestal offset<br>threshold | 0      10        31      11        60      40        17      17        0      40        27      27        60      40        5      5 | we clear stort      7      2      2        swe clear stort      7      2      7        swe glot stort      7      3      7        swe glot stort      7      3      13        swe glot stort      7      3      13        swe flot stort      11      3      13        swe flot stort      0      3      0        offset core stort      0      0      0        other core stort      0      0      0 | J'DHFL_control/iniTiles/DHP Ini<br>Open ind fiel in<br>editor<br>run DHP ini<br>errin<br>klick to choose pedestal ini Tile<br>run parseMem<br>Mask Pipets |

|                                                                                                                                                                                                                                                                     | write to<br>ITAG                                                                                                                     | read JTAG                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Row Set to value Execute Python                                                                                                                           |

Technische Universität München

Hardware Problems

**Firmware Problems**

**Slow Control**

## DHH for Test Setups

- Data flow similar to the test beam firmware

- New: 4 DHP chips

- round robin algorithm for read-out of the filtered frames

- Data read-out over IPBus

- IPBus on the second ethernet interface

- 10 Mbps on 100 Mbps network

- data saved in ONSEN format

- full frame read-out synchronous with trigger signal

- test JTAG on large chain

## BHH for Test Setups

- Data flow similar to the test beam firmware

- New: 4 DHP chips

- round robin algorithm for read-out of the filtered frames

- Data read-out over IPBus

- IPBus on the second ethernet interface

- 10 Mbps on 100 Mbps network

- data saved in ONSEN format

- full frame read-out synchronous with trigger signal

- test JTAG on large chain

# Thank you!

# **Backup Slides**

## DHP Interface Timing Diagram

| <pre>_ rx_src_rdy_n</pre> | 1    | 1    |     |         |        |               |     |      |      |       |                |   |  |      |      |       |  |    |    |

|---------------------------|------|------|-----|---------|--------|---------------|-----|------|------|-------|----------------|---|--|------|------|-------|--|----|----|

| ⊶ rxd                     | 8B4D | 8B4D | _Х. | . )(вв5 | \$685Å | 3 <b>85</b> ₿ | в5≬ | )(зв | 5∰3B | 5)¥88 | 6 <b>0</b> 8B6 |   |  |      |      |       |  | (8 | B6 |

| — <mark>rx_sof_n</mark>   | 1    | 1    |     |         |        |               |     |      |      |       |                | 1 |  |      |      |       |  |    |    |

| - rx_eof_n                | 1    | 1    |     |         |        |               |     |      |      |       |                |   |  |      |      |       |  |    |    |

| — dhp_fck_i               | 0    | 0    |     |         |        |               |     |      |      |       |                |   |  |      |      |       |  |    |    |

| <pre>_ dhp_trg_i</pre>    | 0    | 0    |     |         |        |               |     |      |      |       |                |   |  | <br> | <br> | <br>1 |  |    |    |

|                           | - I  | _    |     |         |        |               |     |      |      |       |                |   |  |      |      |       |  |    |    |