## **Test Beam Preparations**

C. Marinas University of Bonn

cmarinas@uni-bonn.de

#### Global Schedule (Preliminary) DECEMBER 2013

| Monday         | Tuesday             | WEDNESDAY | Thursday                | Friday | Saturday | Sunday |

|----------------|---------------------|-----------|-------------------------|--------|----------|--------|

| MARCO<br>@TB24 |                     |           |                         |        |          | 1      |

| 2              | 3                   | 4         | 5<br>PocketDAQ<br>@TB24 | 6      | 7        | 8      |

| 9              | 10                  | 11        | 12                      | 13     | 14       | 15     |

|                | DHH/ONSEN with EMCM |           |                         |        |          |        |

| 16             | 17                  | 18        | 19                      | 20     | 21       | 22     |

|                | DATCON              |           |                         |        |          |        |

| 23             | 24                  | 25        | 26                      | 27     | 28       | 29     |

| 30             | 31                  |           | PXD<br>SVD<br>PocketDAQ | 3rd    |          |        |

# Laboratory Meeting

Laboratory Meeting Friday 22<sup>nd</sup> November in Bonn

Participants from Bonn, HLL, TUM

L. Germic, C. Marinas, F. Müller, D. Levit, Ch. Koffmane, M. Valentan, F. Lütticke, M. Lemarenko

Preparations towards PXD6 lab and beam tests: ASICs, Sensors, Hardware Components, Software, Firmware

### **ASICs**

• SwitcherB1.8G

SwitcherB1.8G assembled on Hybrid5.0 (DHP0.2) Tex files for SW sequences (non-gated operation) to be prepared

• DCDBv2

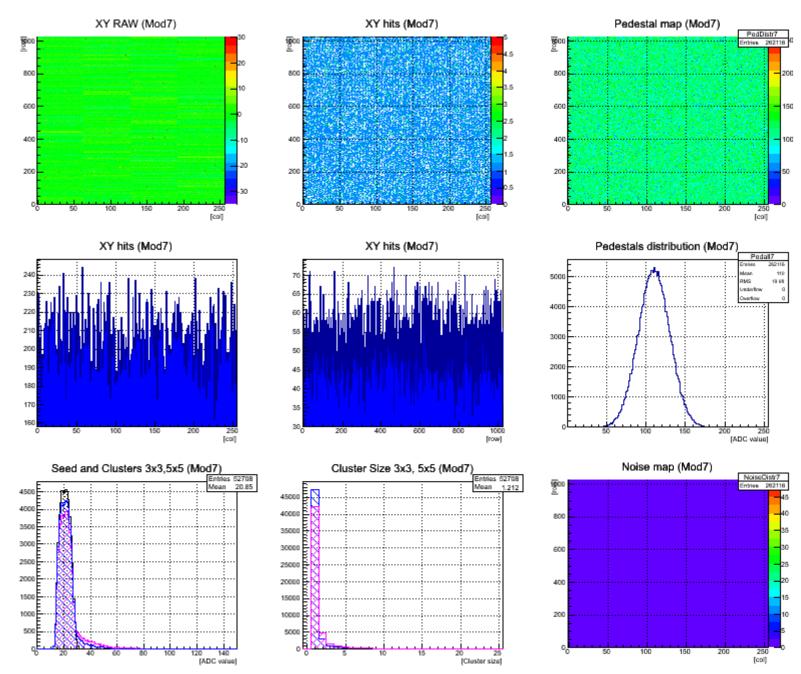

Common set of previously found optimal DACs and RefIn+AmpLow Acquisition of 3x256 (L+R) ADC transfer curves If acceptable, no detailed individual optimization Baseline operation: 250 MHz

DHP0.2

Pedestal compression to be tested

Pedestal calculation from DHH → PC

### Sensors

I06

Belle II Standard Design

50x75 µm<sup>2</sup>

5 SwitcherB1.8G

3 DCDBv2

3 DHP0.2

• J00

Capacitive Coupled ClearGate and PolyCover (externally applied) 50x75 μm<sup>2</sup> 4 SwitcherB1.8G 3 DCDBv2

- 3 DHP0.2

- Both sensor types have been characterized using small PXD6 (H4+H5)

- Asynchronous readout  $\rightarrow$  Data merging via Trigger number

- Only one pair of DCD+DHP read at a time

# Components

- PCB Hybrid 6.0 PXD6-1 arrived Assembly this week

- PCB Hybrid 6.0 PXD6-2 (mirrored) End of this week

- 6 Infiniband cables (15 m) available 8 more ordered

- EMCM jig to be PXD6 adapted  $\rightarrow$  Enlarged opening for lab testing

- Breakout board (20x10 cm<sup>2</sup>)  $\rightarrow$  Attachment to the PCMAG needed

- Carbon-copy of software/firmware/hardware at HLL and Bonn

- DAQ and OnlineMonitor  $\rightarrow$  Ready

- EMCM kept as backup plan

cmarinas@uni-bonn.de

# Thank you

cmarinas@uni-bonn.de