# **PXD9 Status and Plans**

**Rainer Richter**

for the MPG Halbleiterlabor

- PXD9 production status

all wafers on hold - waiting for metallization EMCM4 almost finished - nice results talk by Paola (next time and/or earlier via SeeVogh)

- Pilot production

Proposal: Going ahead with

2(or3) PXD9 wafer + 4(or3) PXD9-3 dummies (matrix not functional)

Time line:

Metal1/Metal2 ready by end of January intermediate test Thinning and Cu metallization by March Final static measurements by end of April

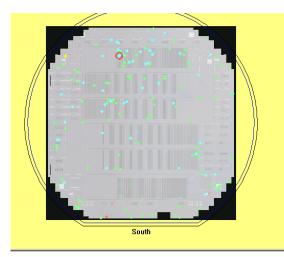

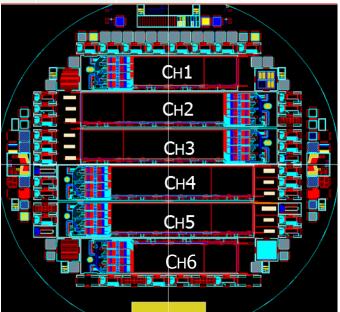

### Selection wafers with of cat. 2 chips based on yield statistics

|       | 0  | 1 | 2 | 3 | 4 | 5 | sum |

|-------|----|---|---|---|---|---|-----|

| Chip1 | 10 | 9 | 2 | 2 | 1 | 6 | 30  |

| Chip2 | 16 | 7 | 1 | 0 | 0 | 6 | 30  |

| Chip3 | 16 | 4 | 3 | 2 | 0 | 5 | 30  |

| Chip4 | 11 | 4 | 5 | 3 | 1 | 6 | 30  |

| Chip5 | 12 | 4 | 4 | 2 | 2 | 6 | 30  |

| Chip6 | 15 | 4 | 2 | 2 | 1 | 6 | 30  |

#### 0 – no severe defects

- **1** single pixel

- 2 -single rows and columns

- 3 whole modul affected?

- 4 whole module killed

- 5 -to be clarified

## • PXD9 Pilot production (ii)

### Pros

- PXD9 dummies are representitive 'EMCMs' (EMCM5 would need a redesign)

- available together with new ASICS and new Kapton

- realistic qualifying of all chips and components

- realistic exercising of the remaining production steps (first on dummies) (wafer thinning, Cu metallization, intermediate and test procedures)

- Smooth production transition from 'EMCM-likes' dummies to PXD9 modules

- Test of Gated mode operation needs real modules (on EMCM limited relevance)

Modules needed:

- -> Fall 15 Testbeam

- -> Beast Phase II

relaxed timing for preparation and tests if we start now

(Start 1/2015 anyway necessary)

## PXD9 Pilot production (iii)

### Cons

Risk to loose of 2 or 3 (2nd grade) PXD9 wafers

if we finally find still a severe bug on EMCM modules

No time to wait with the remaining wafer on the results of fully equipped and tested modules

But we could wait with the first batch for the intermediate tests of metal1/metal2

And we could stop before Copper in order to be able to react in the third metal layer on unforeseen results (e.g. Gated Mode)