# **DHPT test status and roadmap**

6<sup>th</sup> Belle II PXD/SVD Workshop

01-03 October 2014, Pisa, Italy

Leonard Germic, Carlos Marinas, Hans Krüger, Norbert Wermes

**University of Bonn**

ボン大学

Contents

- Status of Test system

- Estimation of test duration

Outlook to the full scale test system

| EMCM results<br>!gated mode! | Metal deposition PXD9 |             |             |                       | PXD9 assembly |  |

|------------------------------|-----------------------|-------------|-------------|-----------------------|---------------|--|

|                              | tape-out<br>DHPT 1.1  | 3 mc        | onths later | receiving<br>DHPT 1.1 | Testing       |  |

| October/Novemb               | <br>ber '14 D         | ecember '14 |             | <br>April '15         |               |  |

- Assumes: Design review of all ASICs on the PXD module after Pisa Workshop ~ <u>October/November</u>

- Gated-mode has to be tested before Design review!!!

- Tape-out of the new revision of DHPT after tested gated mode

DHPT 1.1 testing starts from Q2 '15

| EMCM<br>!gated |        | Metal der            | position PXD9 |             |                       |  | PXD9 assembly |  |

|----------------|--------|----------------------|---------------|-------------|-----------------------|--|---------------|--|

|                |        | tape-out<br>DHPT 1.1 | 3 ma          | onths later | receiving<br>DHPT 1.1 |  | Testing       |  |

| We are here    |        |                      |               |             |                       |  |               |  |

| October/       | Novemt | <br>per '14 De       | ecember '14   |             | <br>April '15         |  |               |  |

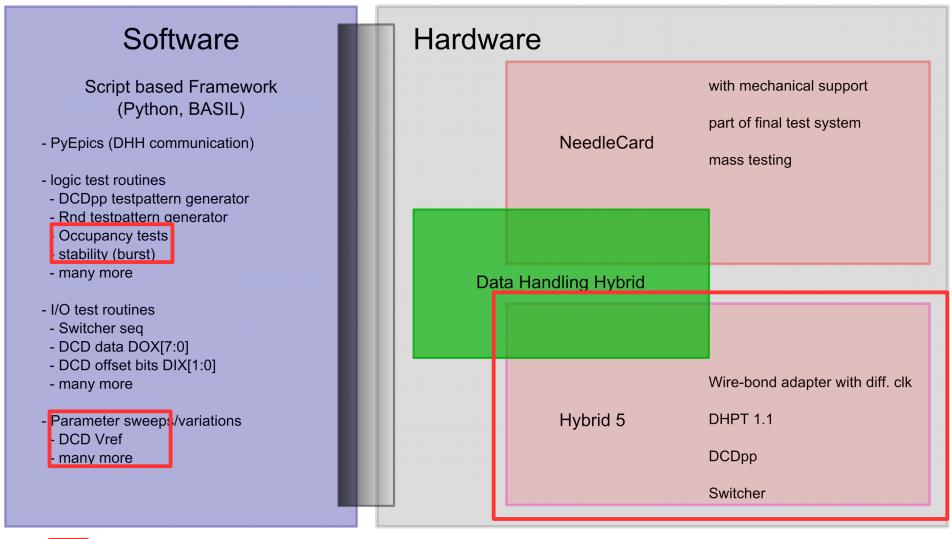

- Development phase of the test system

- **Early I/O tests of the DCD and switcher interface**

- 10x DHPT 1.0 without any fail

- Random switcher sequences (also with switching between sequences)

- Random DCD data read-out

| EMCM results<br>!gated mode! | Metal de             | position PXD9 |          |                       | PXD9 assembly |      |

|------------------------------|----------------------|---------------|----------|-----------------------|---------------|------|

|                              | tape-out<br>DHPT 1.1 | 3 mont        | hs later | receiving<br>DHPT 1.1 | Testing       |      |

| October/Novem                |                      | ecember '14   |          | <br>April '15         | We want to be | here |

## Development phase of the test system

- Early I/O tests of the DCD and switcher interface

- 10x DHPT 1.0 without any fail

- Random switcher sequences (also with switching between sequences)

- Random DCD data read-out

#### not yet finished

#### DHH emulator will be replaced by real DHH

| EMCM results<br>!gated mode!      | Metal deposition PXD9 |                |  |                       |  | PXD9 assembly |  |

|-----------------------------------|-----------------------|----------------|--|-----------------------|--|---------------|--|

|                                   |                       |                |  |                       |  |               |  |

|                                   | tape-out<br>DHPT 1.1  | 3 months later |  | receiving<br>DHPT 1.1 |  | Testing       |  |

|                                   | DHPT 1.0 bug fixes    |                |  |                       |  |               |  |

|                                   |                       |                |  |                       |  |               |  |

| October/November '14 December '14 |                       |                |  | April '15             |  |               |  |

- Bug fixes of DHPT 1.0 and results of the EMCM3 testing at HLL

- Important! Testing of gated mode on full system → EMCM

- phase tuning, delay

- cannot be done on DHPT standalone tests

#### Minor bug fixes of DHPT 1.0

- CML

- Optimized layout for lower parasitic resistance  $\rightarrow$  Improvement of the output amplitude

- Serializer block

- Improved robustness against process variations: current MPW production suffered from 'slow' NMOS which needed to be compensated by higher VDD supply

- Logic

- Minor changes in data format (header information) and additional items to be addressed according to the outcome of the E-MCM tests

| EMCM results<br>!gated mode! | Metal de             | position PXD9  |                                |       | PXD9 assembly |  |

|------------------------------|----------------------|----------------|--------------------------------|-------|---------------|--|

|                              | tape-out<br>DHPT 1.1 | 3 months later | onths later receiving DHPT 1.1 |       | Testing       |  |

|                              |                      |                |                                | deliv | very rate     |  |

| October/Novemb               | <br>per '14 D        | ecember '14    | <br>April '15                  |       |               |  |

\_

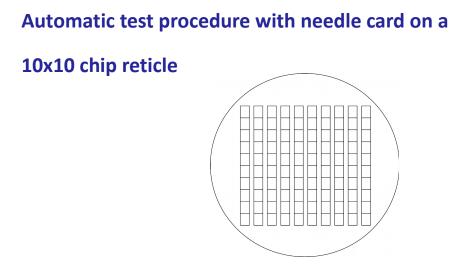

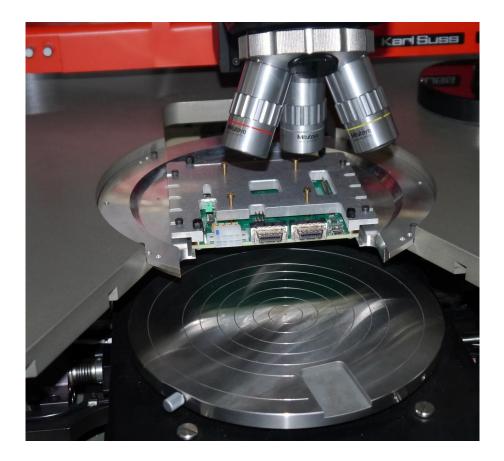

First estimation of DHPT delivery rate

Assuming worst case scenario

Time estimation for full scale testing (assuming "bad" conditions)

- PXD9: 3 batches à 13, 8 and 8 wafers

- $\rightarrow$  29 wafers with 6 half modules  $\rightarrow$  29 x 6 x 4 DHPs ~ 700 DHPs

- Estimated yield 75% (for 65nm TSMC ~ 90% exp.) → 950 tested Dhps

- 1+9 Wafer (100 DHP / wafer)

- Full scale test duration ~ 1h / chip

Tuning parameters: Test duration/DHP, Yield, Worktime

Starting at Q2 '15 -> finishing at ~ Q4 '15 (end of '15)

- Automatic movement from chip to chip

- No optical pattern recognition → manual touch down with the needle

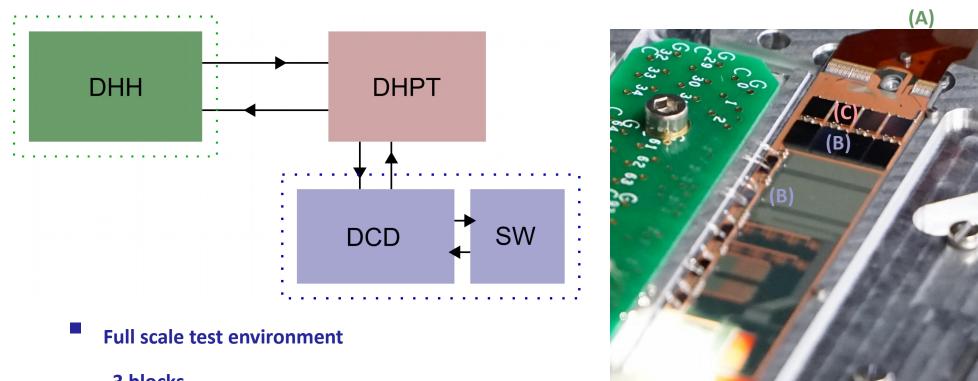

| 3 | b | 0 | C | kS |  |

|---|---|---|---|----|--|

|   |   |   |   |    |  |

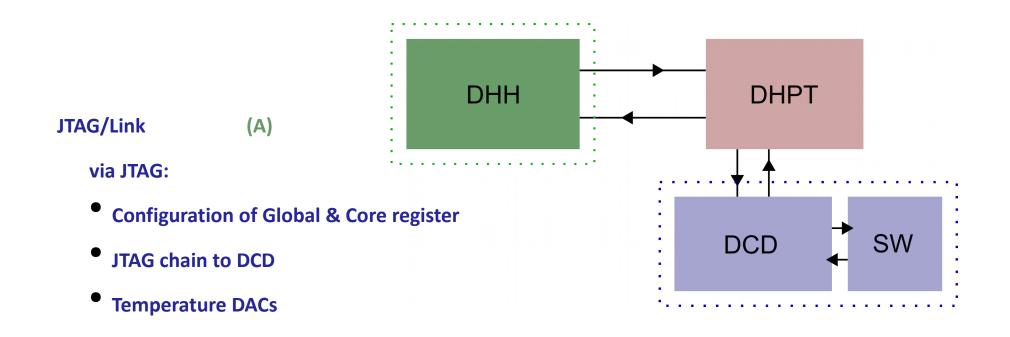

| JTAG/Link | (A)        |

|-----------|------------|

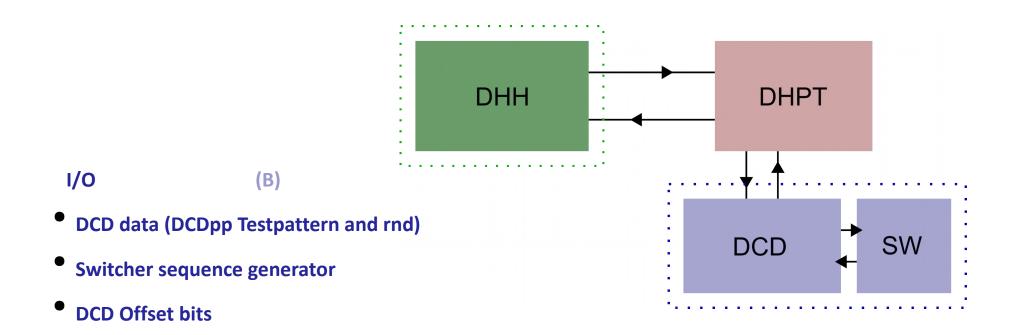

| I/O       | <b>(B)</b> |

| Logic     | (C)        |

#### Via current consumption:

Check CML driver DACs (Gbit Serial Link)

### Logic

- Zero-suppression

- Occupancy test / stability

- Threshold / hit finder

- SRAM tests

- standardized pattern, i.e. 0xaa

- bit error counter (for single bit flip compensation)

- Full scale testing starts in Q2 '15 (assuming design review in October/November)

- Total estimated testing time ~ 6 months (dependent on the conditions, yield + test routine duration)

- reasonable is a delivery rate up to 30DHP/week

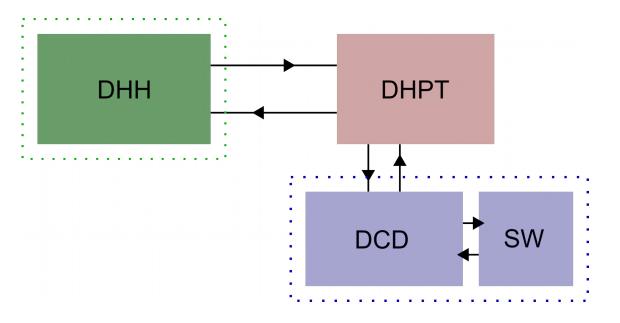

- Final full scale testing consists of three major blocks

- i.e. I/O tests, JTAG/Gbit Link and Logic tests

- I/O tests already successfully performed on 10 chips → Correct working test algorithm

- Needle card stability tested (→ Nevertheless one additional card as backup is foreseen)

We are in time, but there's a lot more to go for!!!

# Thank you