### PXD ASICs Review, JTAG Issues

#### Dima Levit

Physik Department E18 - Technische Universität München

July 22th, 2014

supported by: Maier-Leibnitz-Labor der TU und LMU München, Cluster of Excellence: Origin and Structure of the Universe,

**BMBF**

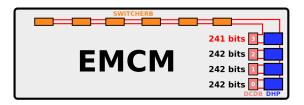

- last DCDB requires one bit less during configuration

- same situation on the module with only one DHP-DCD pair

- work around implemented in software to mitigate the problem

# Problem Localization

- not easy to debug because reading back DCD register is not supported

- trick to localize problem:

- program DHP and DCD simultaneously

- read back DHP register and analyze its content

- repeat with the same bitstream on the next pair

- Switch on DCD0: DCD0 ON. Read data: 01020304 ..

- Switch on DCD1: DCD1 ON. Read data: 01020304.

- Switch on DCD2: DCD2 ON. Read data: 01020304.

- Switch on DCD3: all DCDs OFF. Read data: 01020304.

- Switch on DCD3, remove one bit: DCD3 ON. Read data: 02040608 ...

## Problem Localization

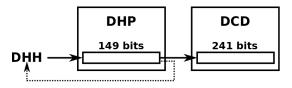

- not easy to debug because reading back DCD register is not supported

- trick to localize problem:

- program DHP and DCD simultaneously

- read back DHP register and analyze its content

- repeat with the same bitstream on the next pair

- Switch on DCD0: DCD0 ON. Read data: 01020304.

- Switch on DCD1: DCD1 ON. Read data: 01020304.

- Switch on DCD2: DCD2 ON. Read data: 01020304 ..

- Switch on DCD3: all DCDs OFF. Read data: 01020304.

- Switch on DCD3, remove one bit: DCD3 ON. Read data: 02040608.

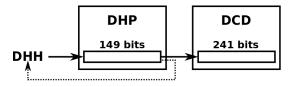

## Problem Localization

- not easy to debug because reading back DCD register is not supported

- trick to localize problem:

- program DHP and DCD simultaneously

- read back DHP register and analyze its content

- repeat with the same bitstream on the next pair

- Switch on DCD0: DCD0 ON. Read data: 01020304 ..

- Switch on DCD1: DCD1 ON. Read data: 01020304 ..

- Switch on DCD2: DCD2 ON. Read data: 01020304 ...

- Switch on DCD3: all DCDs OFF. Read data: 01020304 ...

- Switch on DCD3, remove one bit: DCD3 ON. Read data: 02040608 ...

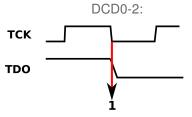

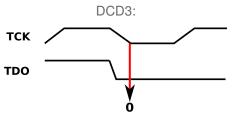

- clock and data equally fastprevious bit sampled

- requires additional bit for compensation

- long TCK line:

- large capacitance

- slow signal transition

- does not require dummy bit

### (S) Implications/Solutions

### **Implications**

- uncertainty in the configuration because of metastability

- we can loose 1/4 of the matrix

#### Solutions

- Use DHPT TDO delay to adjust signal timing:

- has to be tested in hardware

- Software workaround: remove one bit if configuring DCD which is connected to Switchers

- very ugly solution: two affected DCD positions depending on the half ladder layout.

- uncertainty remains

- Fix DCD JTAG design

### IDCODE Problems in DCD (not critical)

- After resetting JTAG FSM (5xTMS High) bypass register with '0' is loaded instead of IDCODE. IDCODE is still present.

- Unique IDCODE for DCD Pipeline?

## Back up slides