# DHP

L. Germic, T. Hemperek, T. Kishishita, H. Krüger, F. Lütticke, <u>C. Marinas</u>, N. Wermes University of Bonn

cmarinas@uni-bonn.de

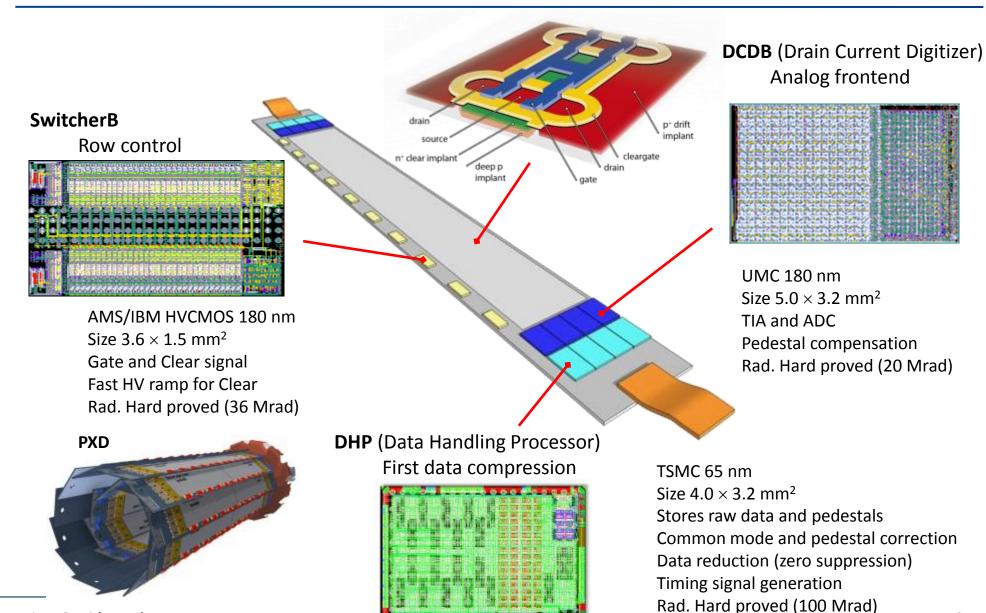

### **The DEPFET Ladder**

cmarinas@uni-bonn.de

2

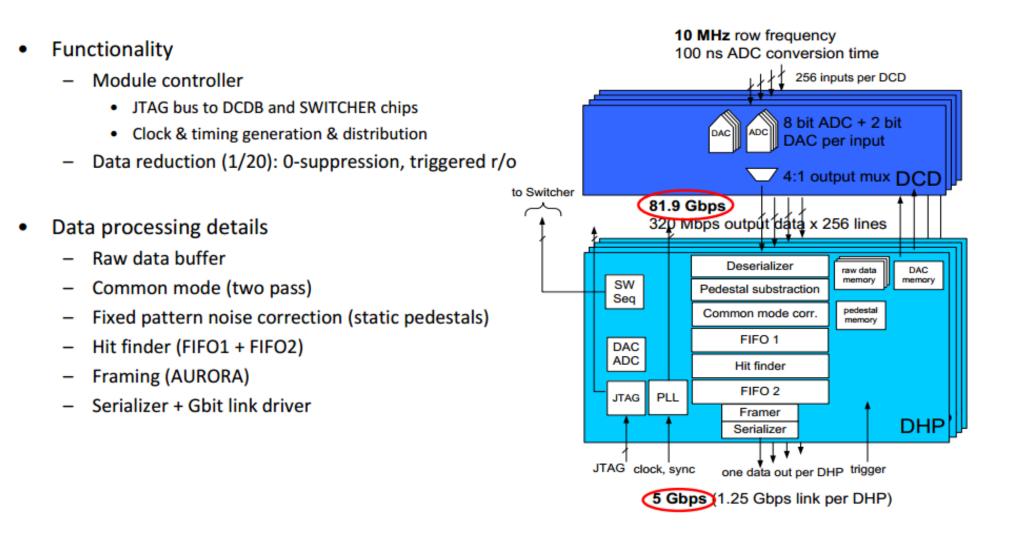

The DHP is a digital chip used to reduce data rates produced by the DCD

To do the data reduction, the DHP does:

- Data pre-processing: triggered frame selection, pedestal subtraction, common mode correction and zero suppression.

- Serial formatting to send the data to the DHH through a specially designed current mode logic serial link.

- Correct for pedestal spread sending the offset sequence.

- The DHP is responsible for the control sequence generation for the Switcher-B chips chain, thus steering the matrix.

## **DHP Functional Overview**

## **DHP Functionality**

- Data processing

- SWITCHER sequencing

- Inter-chip communication

- Serial link

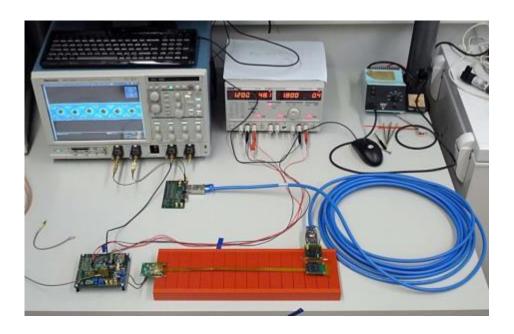

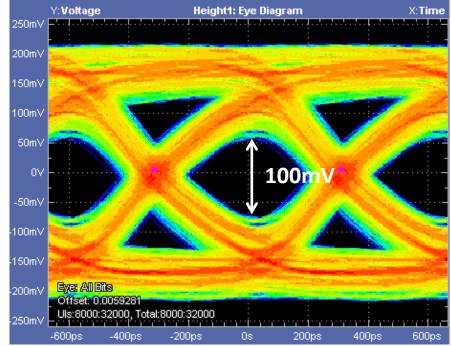

#### Irradiated (100 Mrad) DHPT 0.1, can drive 20 m of Infiniband cable

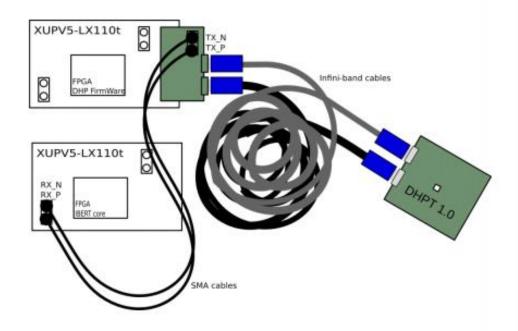

**BER Tests**

• Error rate tests and parameters optimization for designed 15m cables

Parameter optimization for 15m data cable

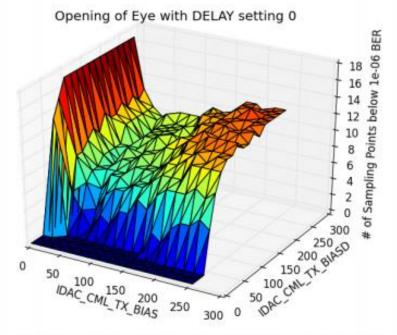

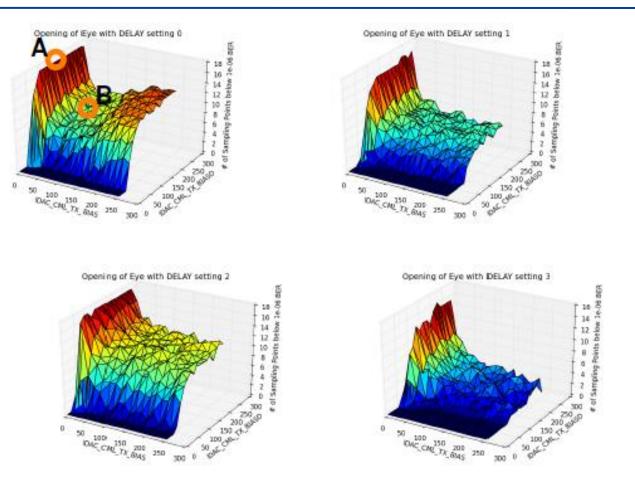

## **Optimal Working Point**

Figure: Sweep results at a threshold of  $BER_{thr} = 10^{-6}$ . Higher is better - wider opening at  $BER_{thr}$

cmarinas@uni-bonn.de

## **Status of the Funcional Verification**

|                 | IP Block / Task                         | Status       | Comment                               |

|-----------------|-----------------------------------------|--------------|---------------------------------------|

|                 | Gbit Link Driver                        | ✓            |                                       |

|                 | PLL / Serializer                        | (✓)          | Works with adjusted VCC / CLK freq.   |

| P               | Temperature Sensor                      | ✓            |                                       |

| Custom          | LVDS IO                                 | $\checkmark$ |                                       |

| Cus             | Interface DHP-DCD                       | TBD          | Need new WB adapter (LVDS DCDCLK)     |

|                 | Interface DHP-Switcher                  | (✓)          | Gated mode operation not verified yet |

|                 | Bias DAC, Current reference             | ✓            |                                       |

| ٥d              | Command Interface (Manchester encoded)  | $\checkmark$ |                                       |

| essin           | Memory Access (via JTAG)                | ✓            |                                       |

| Data Processing | Data Processing: Channel Masking        | TBD          |                                       |

|                 | Double Precision Common Mode Processing | ✓            |                                       |

| Δ               | Overflow Handling                       | TBD          |                                       |

- Fix serializer (small change in the schematic/layout)

- Improve CML AMPLITUDE

#### **Plans**

- Hybrid 5.0:

- Tests communication DCD ↔ DHP

Irradiation, temperature, 2b DAC, timing and phase alignment

- Assembly planned within the next 4 weeks

- Tests to be finished by March

- EMCM:

- System related aspects

Link stability and parameter optimization

- PXD modules a sensitive to single-point-of-failure of the DHP

- We had very little statistics of the DHP yield (limited to wire bond adaptors)

- Need to qualify the chips before flip-chip mounting

- What do we do in terms of QC on the DHPs?

- How do we make sure the chips delivered are OK for mounting on the PXD?

cmarinas@uni-bonn.de

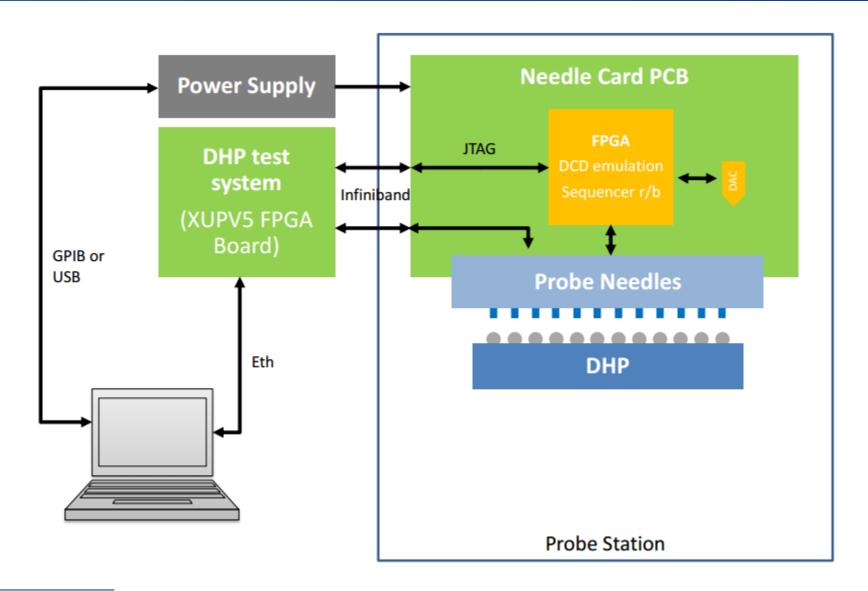

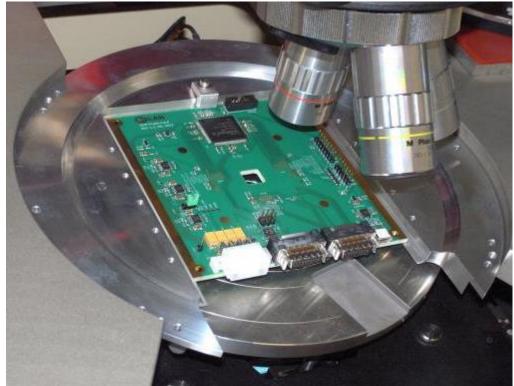

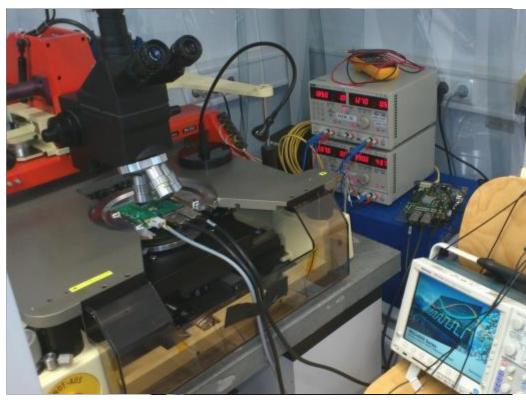

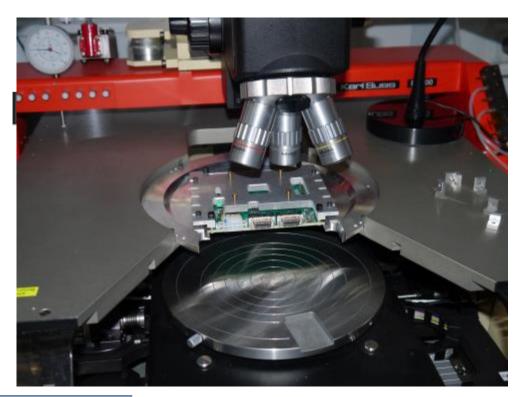

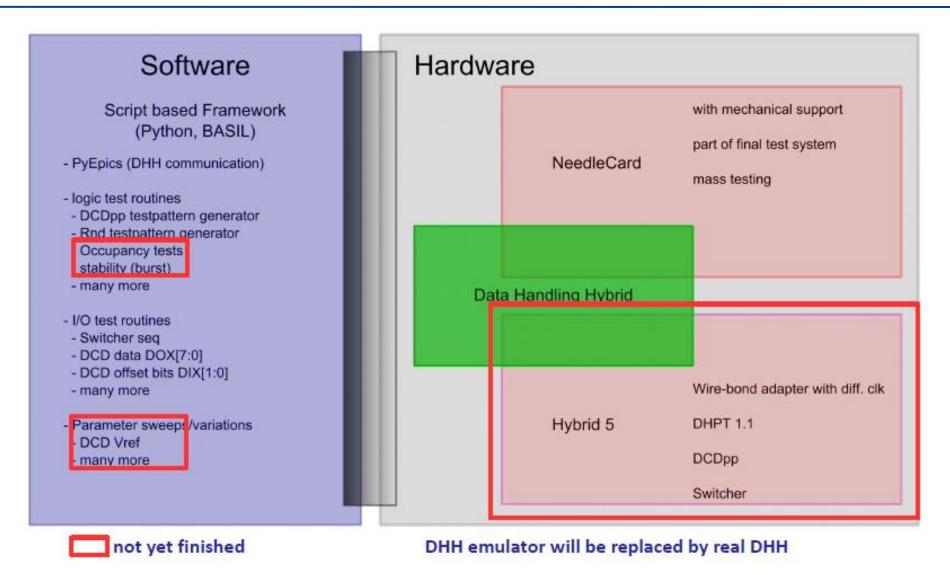

- Needle card fixture

- We have diced chips only

- Put single chips on chuck (Ok for now)

- External components:

- Power supply

- VDD = 1.2 V, VDD\_CML = 1.2 V and DVDD = 1.8 V

- Xilinx XUPV5 Evaluation Platform (DHHemulator)

- 1 GHz Oscilloscope

- Needle card fixture

- We have diced chips only

- Put single chips on chuck (Ok for now)

- External components:

- Power supply

- VDD = 1.2 V, VDD\_CML = 1.2 V and DVDD = 1.8 V

- Xilinx XUPV5 Evaluation Platform (DHHemulator)

- 1 GHz Oscilloscope

cmarinas@uni-bonn.de

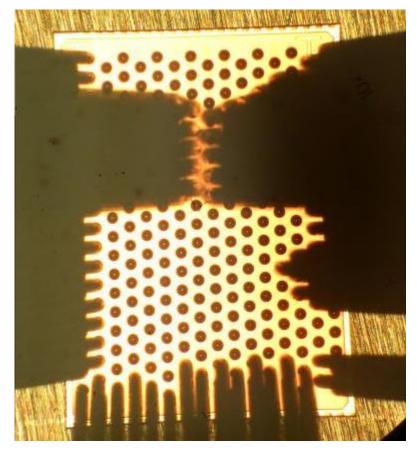

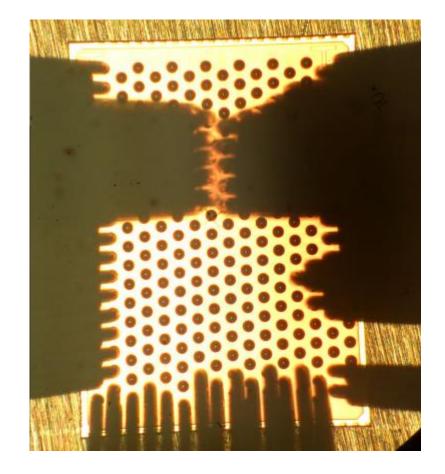

## **Needle Card**

- Xilinx Spartan 6 (DCD emulator)

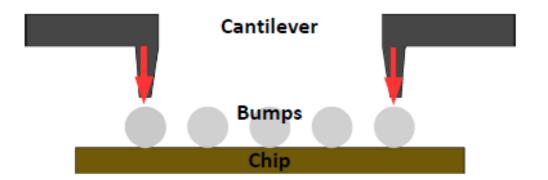

- Cantilever Needles

- Power Connector

- Infiniband Connector to DHHe (Data, JTAG)

## universität**bonn**

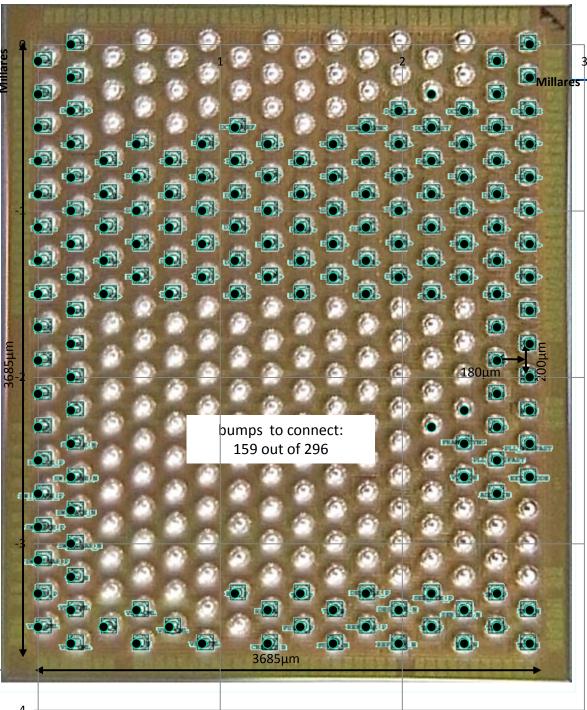

- 159 bumps need to be connected

- Material: SAC

- Pitch: 200 μm (y), 180 μm (x)

- ~110 μm diameter

- Connections:

- JTAG (4x LVDS)

- Timing (4x LVDS) DHP test system

- Data Link (1x CML)

- Aux clock (2x LVDS)

- SWITCHER (4x LVDS)

- DCD out (8x 8 HSTL)

- DCD in (8x 2 CMOS)

- DCD timing (2x CMOS)

- DCD JTAG

- DCD\_ref (analog)

- Power (8x VSS, 4x VDD, 2x VDD\_CML)

- PLLxx2Fast

- FrameSync

- ResetB (CMOS)

- Analog IO test signals

- 159 bumps connected Power, JTAG, DCD I/O and SW

- Over travel after last needle contacted ~10  $\mu m$

- Manual alignment and touchdown

- If card not used for days, needles pre-cleaned

- 159 bumps connected

Power, JTAG, DCD I/O and SW

- Over travel after last needle contacted  ${\sim}10~\mu m$

- Manual alignment

- If card not used for days, needles pre-cleaned

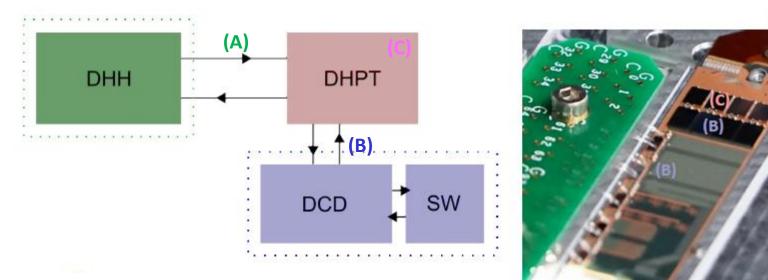

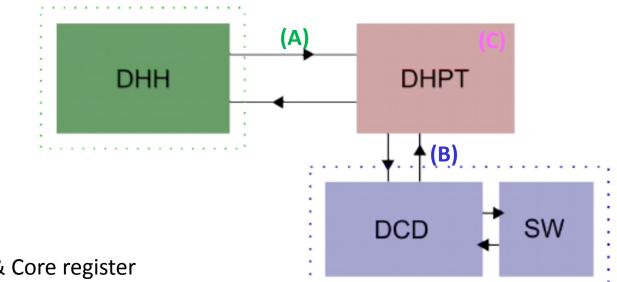

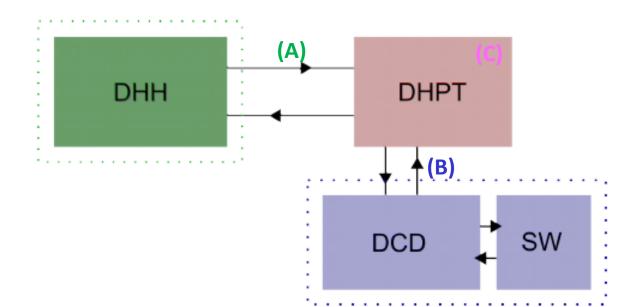

#### **Test System**

(A)

The tests must include 3 blocks:

- JTAG/Link (A)

- I/O (B)

- Logic (C)

#### JTAG/Link (A)

- Configuration of Global & Core register

- JTAG chain to DCD

- Temperature DACs

- Check CML driver DACs (Gbit Serial Link) via current consumption

#### I/O (B)

- DCD data (DCDpp test pattern and rnd)

- Switcher sequence generator

- DCD offset bits

cmarinas@uni-bonn.de

#### Logic (C)

- Zero-suppression

- Occupancy tests

- Threshold/hit finder

- SRAM tests

- Standardized pattern (Oxaa)

- Bit error counter (single bit flip compensation)

cmarinas@uni-bonn.de

## **Status of the Funcional Verification**

|            | IP Block / Task                         | Status | Comment                               |

|------------|-----------------------------------------|--------|---------------------------------------|

|            | Gbit Link Driver                        | ✓      |                                       |

|            | PLL / Serializer                        | (✓)    | Works with adjusted VCC / CLK freq.   |

| ٩          | Temperature Sensor                      | ✓      |                                       |

| Custom     | LVDS IO                                 | ✓      |                                       |

| Cus        | Interface DHP-DCD                       | TBD    | Need new WB adapter (LVDS DCDCLK)     |

|            | Interface DHP-Switcher                  | (✓)    | Gated mode operation not verified yet |

|            | Bias DAC, Current reference             | ✓      |                                       |

| ۵۵         | Command Interface (Manchester encoded)  | ✓      |                                       |

| Processing | Memory Access (via JTAG)                | ✓      |                                       |

| roce       | Data Processing: Channel Masking        | TBD    |                                       |

| Data F     | Double Precision Common Mode Processing | ✓      |                                       |

| Δ          | Overflow Handling                       | TBD    |                                       |

- Functional verification

- Analog blocks

- Digital signal processing  $\rightarrow \checkmark$ , ongoing (high occupancy test)

- − Interface DCD, Switcher  $\rightarrow$  ( $\checkmark$ ) gated mode operation, tbd.

- Serializer too slow  $\rightarrow$  needs non standard operation conditions (higher VDD supply)

- Probe station test to deliver KGD for prototype module assemblies ongoing

- Continue with in-system verification using E-MCM and PXD9 pilot modules

- Switching of operation modes

- Signal integrity (high speed link)

- TID sensitivity

- Planned re-design DHPT 1.1

- Serializer bug fix

- Anything else that eventually shows up (Data processing, E-MCM operation ...)

- Hybrid 5.0:

- Tests communication DCD ↔ DHP

Irradiation, temperature, 2b DAC, timing and phase alignment

- Planned within the next 4 weeks

- EMCM:

- System related aspects

Link stability and parameter optimization

- After B2GM

- Pilot Run PXD9

- Gated mode and timing

- April 2015

#### $\rightarrow$ Final submission after positive feedback from these tests

cmarinas@uni-bonn.de

#### • 33 DHPT1.0 tested

#### 4 non operational (1 broken, 3 with bump issues)

| #Chip<br>ID | Power |             | JTAG     |     |     | DCD         | Serial Link |     | Issues     |             |

|-------------|-------|-------------|----------|-----|-----|-------------|-------------|-----|------------|-------------|

|             | GCK   | VDD+VDD_CML | DVDD     | DHH | DCD | sw sequence | Data        | PLL | CML dirver |             |

| 1           | x     | <10mA       | <30mA    | x   | n/A | n/A         | n/A         | n/A | n/A        | no response |

| 2           | ok    | ~90mA       | ~37mA    | ok  | ok* | ok**        | n/A         | ok  | ok**       |             |

| 3           | ok    | ~82mA       | ~42mA    | ok  | ok* | ok**        | n/A         | ok  | ok**       |             |

| 4           | ok    | ~104mA      | ~31mA    | ok  | ok* | ok**        | n/A         | ok  | ok**       |             |

| 5           | ok    | ~105mA      | ~39mA    | ok  | ok* | ok**        | n/A         | ok  | ok**       |             |

| 6           | ok    | ~102mA      | ~38mA    | ok  | ok* | ok**        | n/A         | ok  | ok**       |             |

| 7           | ok    | ~103mA      | ~38mA    | ok  | ok* | ok**        | n/A         | ok  | ok**       |             |

| 0           | ok    | ~0.0m A     | ~2.2 m A | ak  | ok* | ak**        | n/A         | ok  | ak**       |             |

ok\* loop back: DHH emulator  $\rightarrow$  TDI  $\rightarrow$  DCD emulator  $\rightarrow$  TDO  $\rightarrow$  DHH emulator ok\*\* Oscilloscope inspection (incl. Gated mode via veto (trigger) and LFSR output)

- Optical inspection: Missing balls, scratches on the passivation

- Tests with needle card (grounding, handling, reinforcing plate)

- Metrology after needle card testing (flattened balls ~3-5 μm)

- No issues found after several flip chip assemblies at IZM

- MPW submission

- Two MPW runs per month, turn-around ~12 weeks

- PXD production

- Can be done with MPW production + extra wafers, no engineering run needed

- 30 wafers on PXD9, 6 modules per wafer, 4 DHPT1.1 per module = **720 DHPT1.1** units

- We assume so far a yield of 65 % (extrelemy pessimistic)  $\rightarrow$  1100 DHPT1.1

- Full scale testing

- 'Chess board' fixture with 10x10 array of cavities for production testing

- Backup needle card

- Realistic scenario: 85 % yield, 5 chips/day, 5 days/week → 8 months to deliver fully tested DHPs enough to populate the 180 modules from PXD9

cmarinas@uni-bonn.de

# Thank you

#### **Status of the Test System**

cmarinas@uni-bonn.de

Automatic test system

- 1) Current and Voltage check (so far manually)

- 2) Configuration of JTAG registers

- 3) I/O testing

- 3a) DCD emulator memory filled with random data (random bit gen.) and read by DHPT

$\rightarrow$  Comparison (5 cycles)

- 3b) DHPT switcher sequence is filled with random data

- $\rightarrow$  Switcher sequence is read and switcher mem blocks are swapped back and forth (5 cycles)

- 3c) DHPT offset bits are generated and read by the DCD emulator

- $\rightarrow$  Comparison (5 cycles)