#### SVD slow control progress

#### Szymon Bacher

Institute of Nuclear Physics, Polish Academy of Science, Kraków, Poland University of Science and Technology, Kraków, Poland

#### Personal change

- Juan is about to leave SVD Slow control soon,

- I have signed contract with IFJ-PAN

#### Recent progress

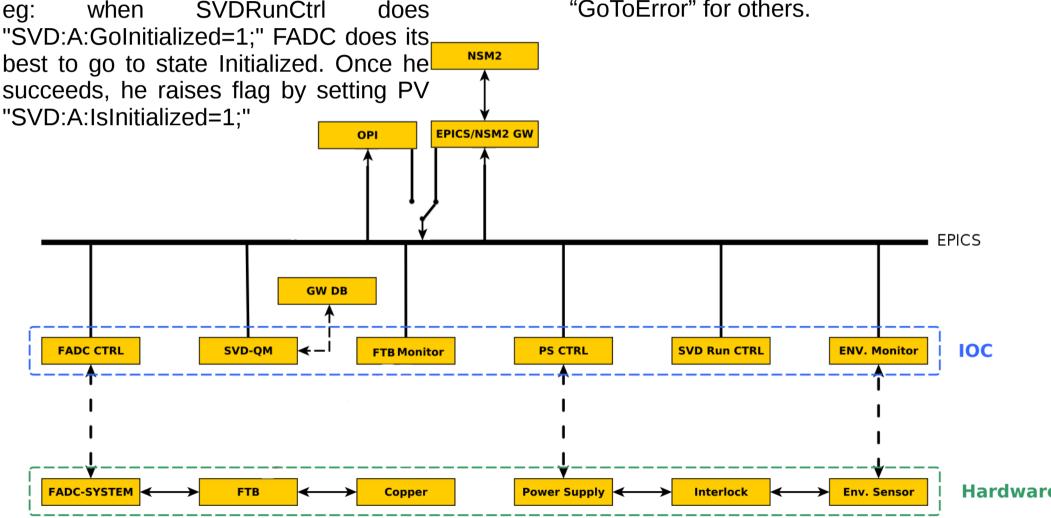

- Power supplies: first version of IOC prepared and tested by Juan seems to work.

- Works on Epics wrapper for former "TuxDAQ" and "TuxOA" started by Hao. First drafts of interface exist and look promising.

- Draft SVD run ctrl is being tested. We chose flag driven approach, with hierarchical state machines.

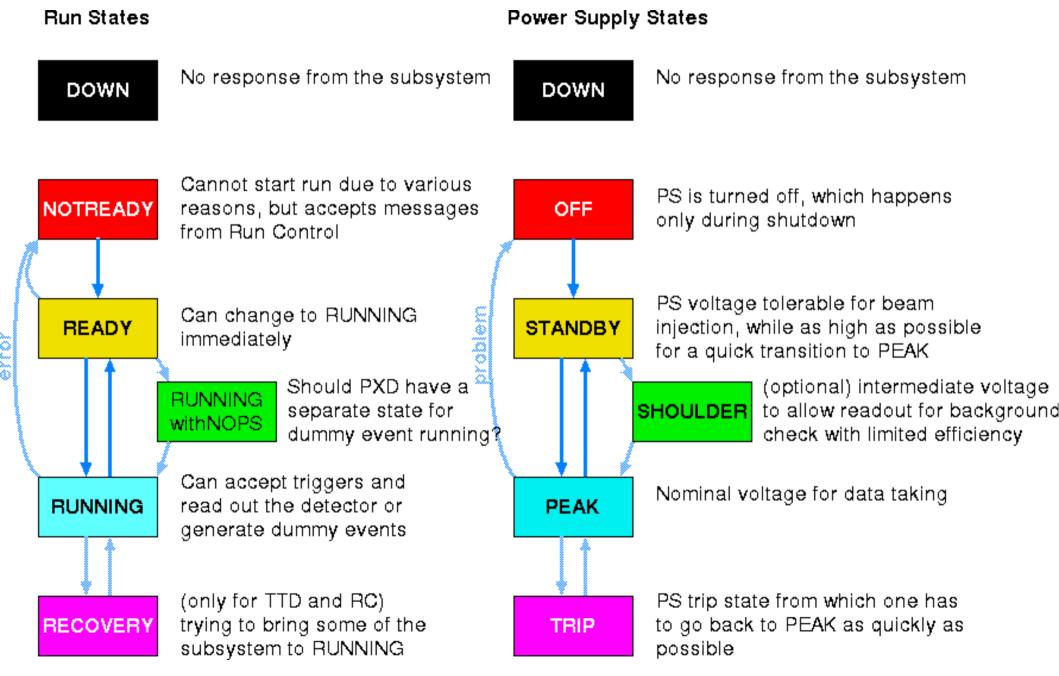

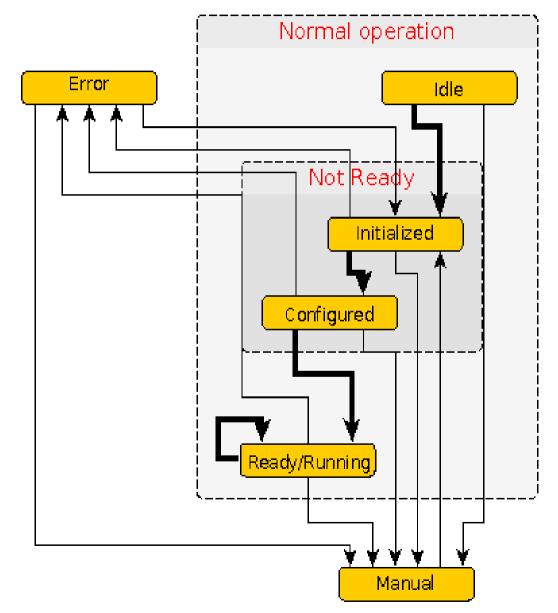

#### State machine concept

### State machine concept

Startup steps can be divided into two groups:

- Things to do before low voltage is on

- Things to do after low voltage is on

eg: setting up APV must happen after ramping LV.

because of that, Nakao-san`s "NotReady" step is subdivided into two steps:

- Initialized

- Configured

# All IOCs have their own state machine,

with identical states.

For IOCs other then SVDRunCTRI state transitions are dependent of flags raised by SVDRunCtrl.

SVDRunCtrl

does

when

If any IOC is stuck as some step (eq. PS waits for "Standby", whole system will wait. Also, every IOC can issue "GoToError" for others

### Hierarchical design merits

- Hierarchical design meant for simplicity and separation of IOCs.

- SVDRunCtrl does not care about number of thermometers Environmental Monitors have, since Env IOC would not rapport readiness if system would be to hot.

- Same goes for other IOCs.

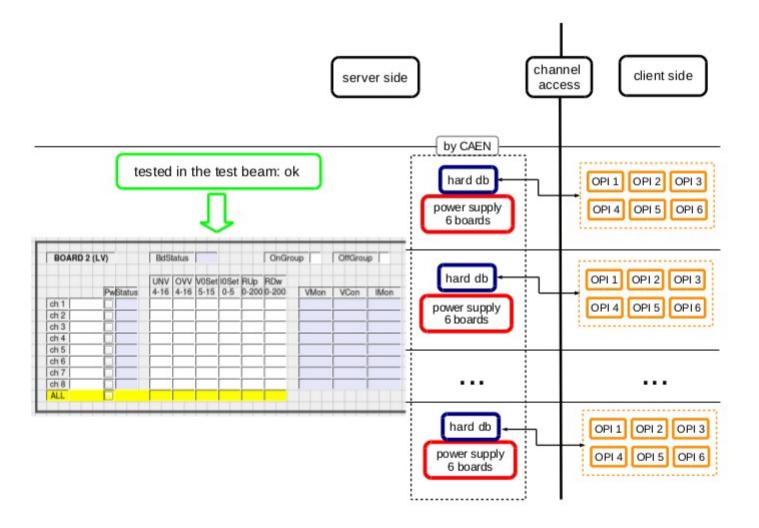

#### **Power supplies**

- New CAEN power supplies are EPICS-friendly (db files provided)

- Juan prepared IOC with state machines for test PS we have

- All have been tested during CERN beam time.

they have been tested in the test beam and they look like reliable so, task completed

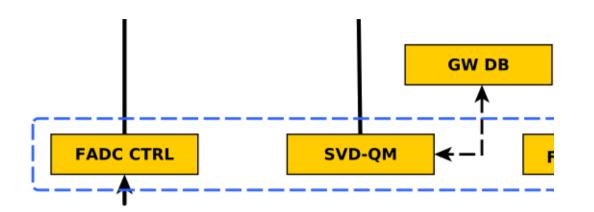

### FADC CTRL, and SVD-QM

- TuxDAQ is being reimplemented to be more modular and easier to read.

- First version of interface have been prepared.

- Start of integration works due in march.

#### Recent agreements

- We will share with PXD not only code, but also GUI layout - dedicated meeting is being considered

- SVD Slow Control programmers started having independent TelCons, they will become regular.

- FADC-ctrl and Database are our main focus right now.

#### Thank you for listening

#### Backup, functions of blocks.

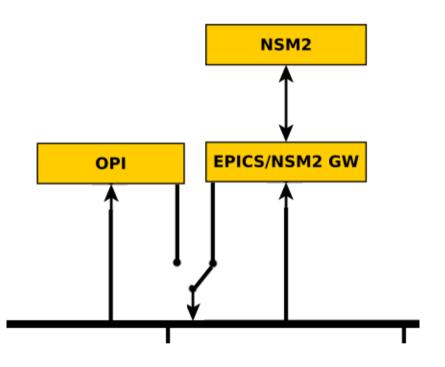

### Communication with outside world

#### Local/Global run:

Read access is always granted to SVD operator and to Master RC, but write access is always granted to only one of them.

Status: Waiting for Gateway to be developed.

### FADC control and quality monitor

#### Status:

- Communication are working.

- Epics wrapper for them is next thing to develop now.

## Monitoring FTB functionality

Status: Waiting for NSM/EPICS GW

### **Power Supplies**

- Tender process for PS is about to finish.

- IOC for sample from CAEN works well.

### **Environment monitor**

**PS CTRL**

**Power Supply**

#### Status:

- Sensors are still being developed.

- At beginning of 2015 I should have access to prototype.

### **Run Control**

#### Purpose:

- In global run: translate state transition signals from Master RC to changes of local Pvs.

- In local: translate state transition signals from OPI to changes of local Pvs, stand by, during manual mode.

#### Status:

- First draft being developed right now.

- Fine grain steps of startup procedure have to be subdivided into Run States.

#### Thank you for listening