### **Design Changes for DHPT 1.1**

H. Krüger, Bonn University DEPFET Workshop, Seeon, May 10-13, 2015

Slides from

#### DHPT 1.1 - Internal Design Review, HLL, Munich, April 16-17, 2015

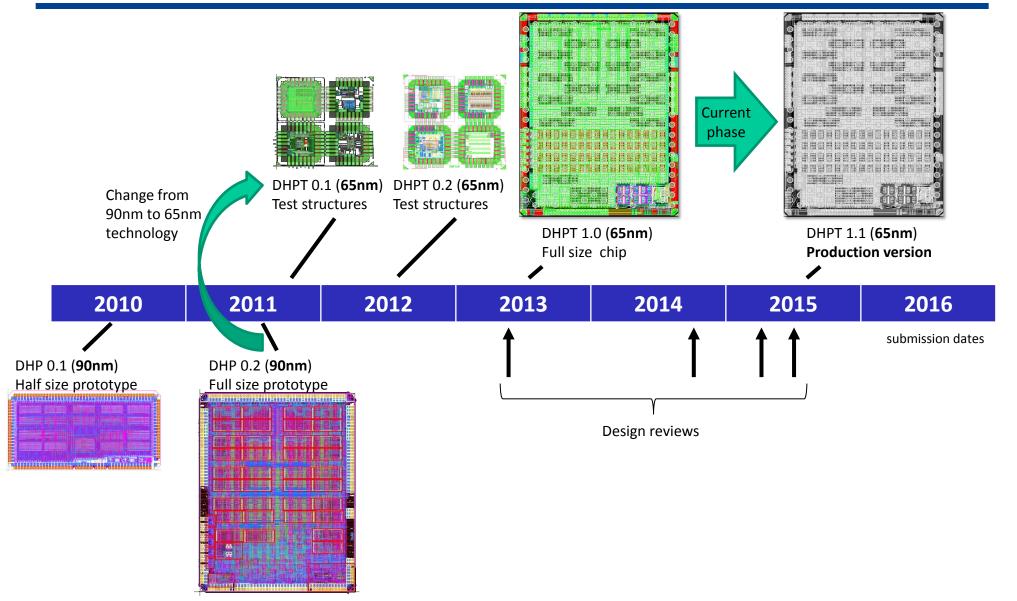

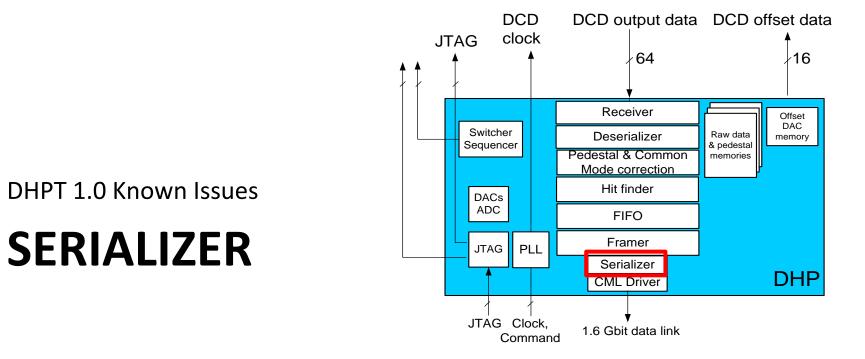

Known DHPT 1.0 issues that shall be improved (or are still open):

- Serializer: timing bug

- CML driver enhancement : reduce parasitic resistance

- Prog. delay elements issue: duty cycle distortion

- Data receiver robustness: duty cycle distortion with non-symmetric input edges

- Data processing enhancements (?)

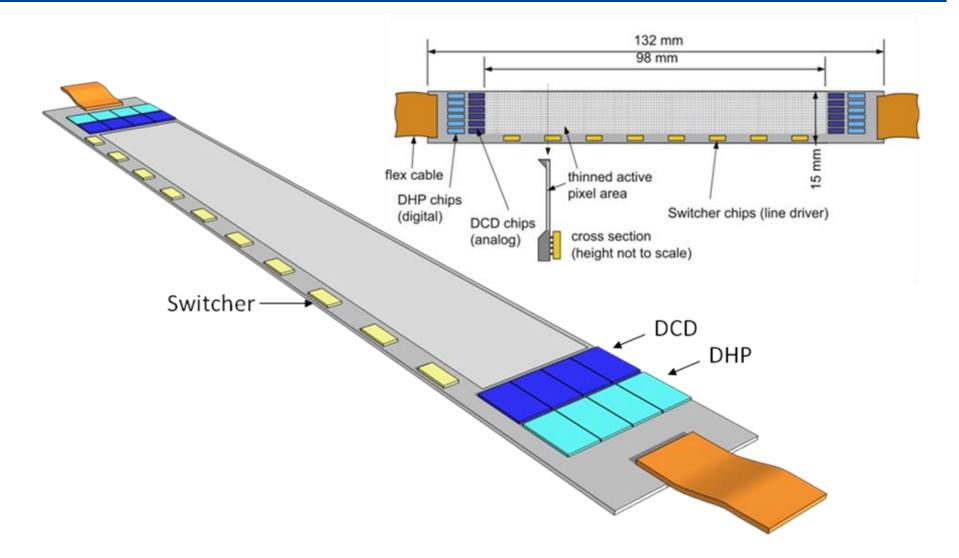

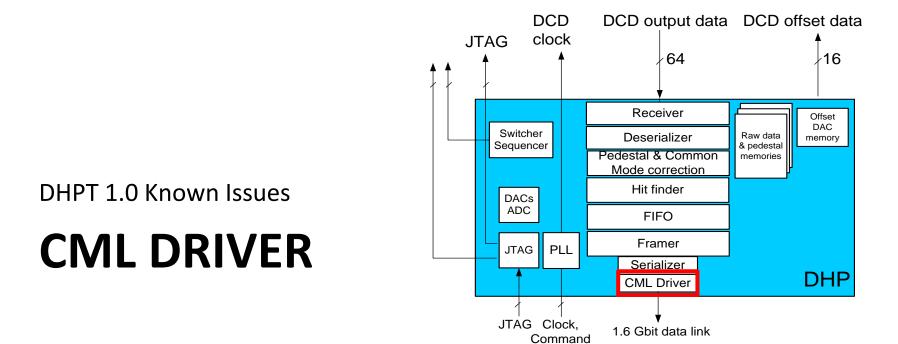

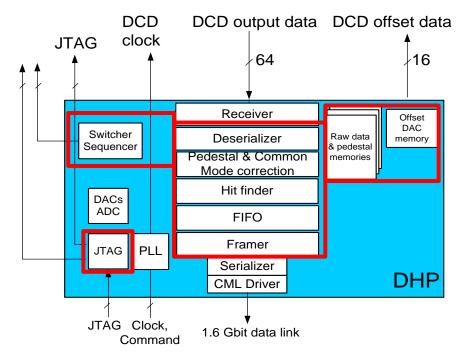

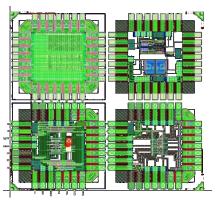

#### **ASICs for the DEPFET PXD**

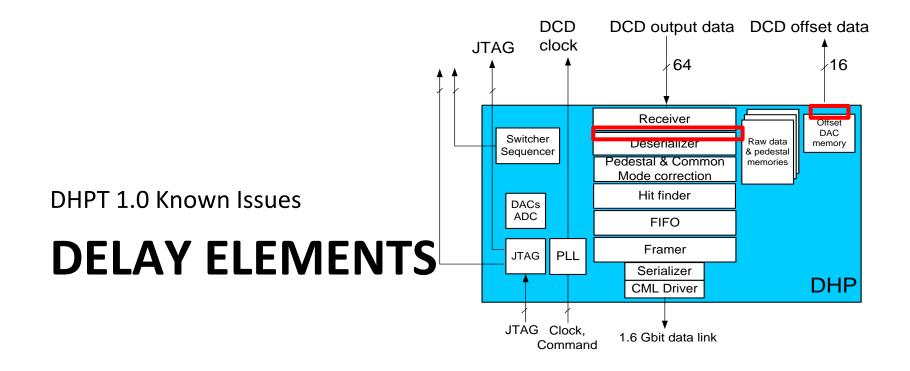

### **Data Handling Processor - DHP**

- Functionality

- Module controller

- JTAG bus to DCDB and SWITCHER chips

- Clock & timing generation & distribution

- Data reduction (1/20): 0-suppression, triggered r/o

- Data processing details

- Raw data buffer (two frames, 40µs)

- Common mode (two pass)

- Fixed pattern noise correction (static pedestals)

- Hit finder (FIFO1 + FIFO2)

- Framing (AURORA)

- Serializer + Gbit link driver

#### **Data Handling Processor Development**

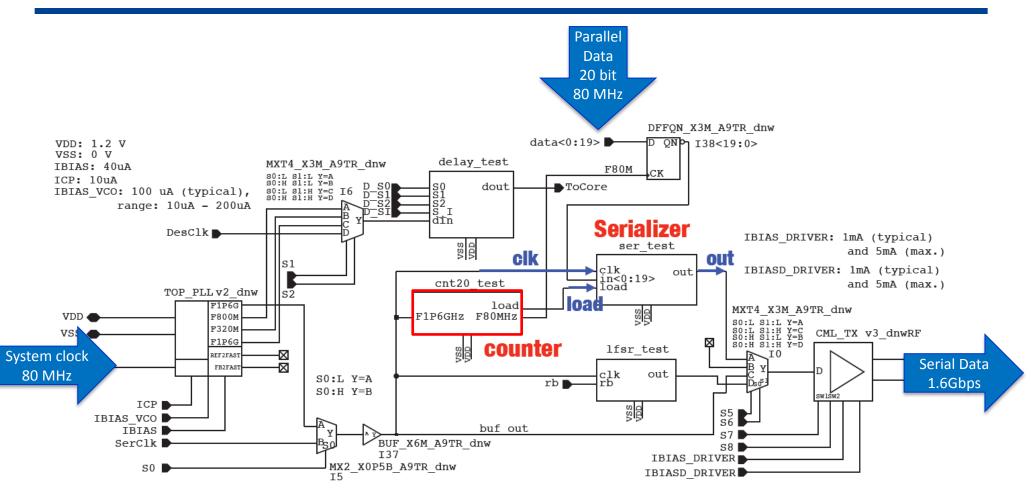

#### PLL + SER Block Diagram

#### **Serializer Bug**

- Mistake made during simulation of the extracted layout with all process corners

- Serializer works, but VCC and/or GCK have to be adjusted:

- GCK= 80 MHz  $\rightarrow$  VCC = 1.6V (works but should not be applied for a long time)

- GCK= 60 MHz  $\rightarrow$  VCC = 1.4V (ok)

- Manufacturer test data → wafer batch has "slow NMOS" (too high threshold)

| PARAMETER | BY LOT:      | SPEC LO    | SPEC HI | MIN        | MAX   | MEAN       | STD DEV   |

|-----------|--------------|------------|---------|------------|-------|------------|-----------|

| VT1 N4    | (N/.3/.06/1) | 0.300      | 0.490   | 0.368      | 0.490 | 0.423      | 0.029     |

| Isof N4   | (N/.3/.06/1) | -1.400E-07 |         | -8.958E-10 |       | -2.339E-10 | 2.063E-10 |

| Isat_N4   | (N/.3/.06/1) | 0.491      | 0.735   | 0.547      | 0.673 | 0.593      | 0.031     |

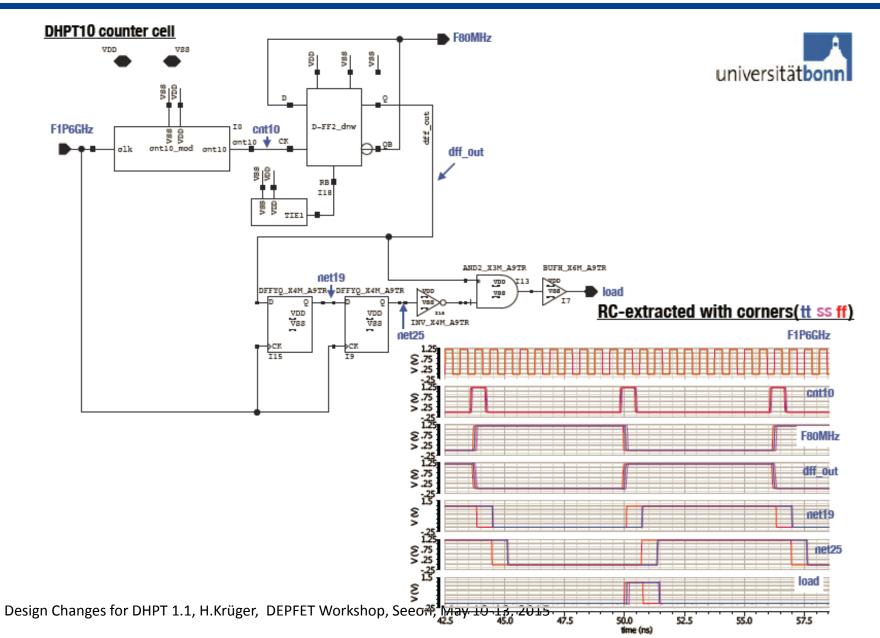

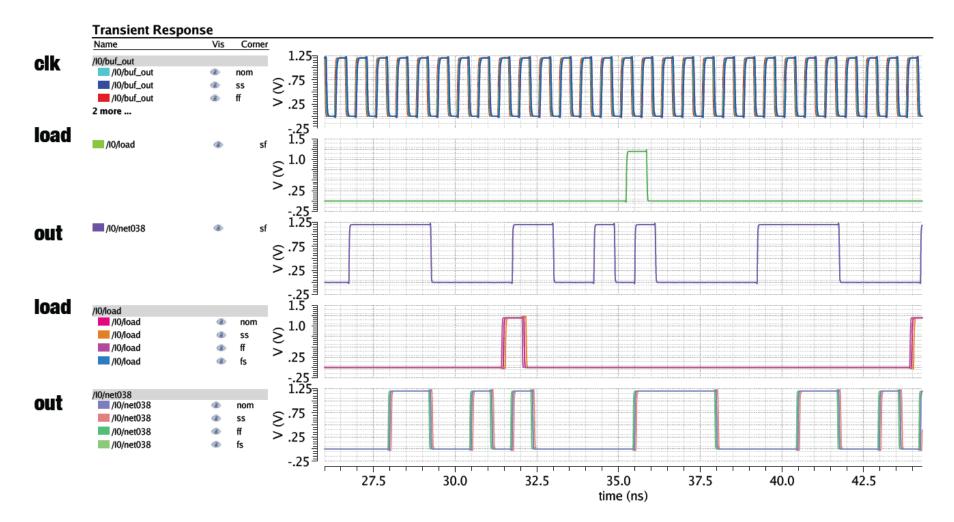

#### Timing of "load" is not provided correctly, except fast-fast corner.

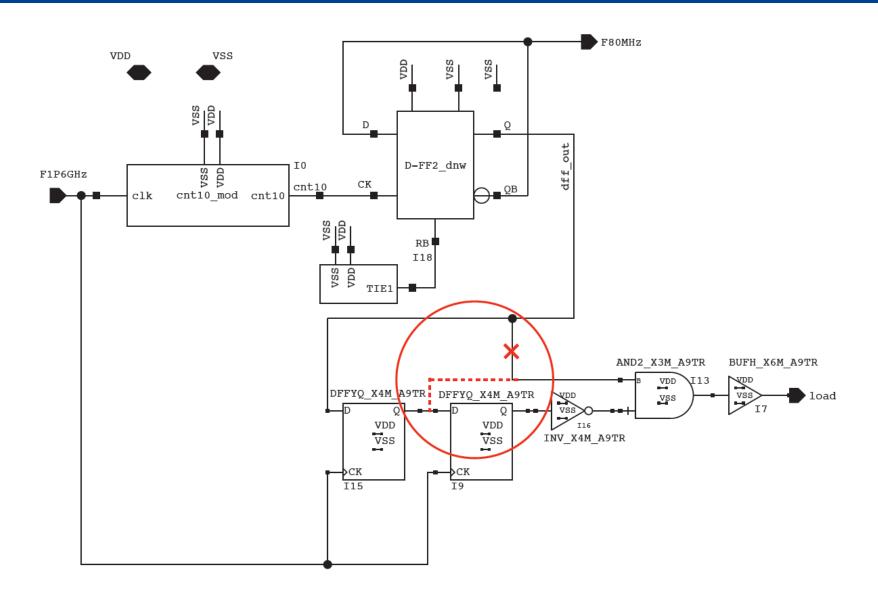

### **Design Fix in the Counter Circuit**

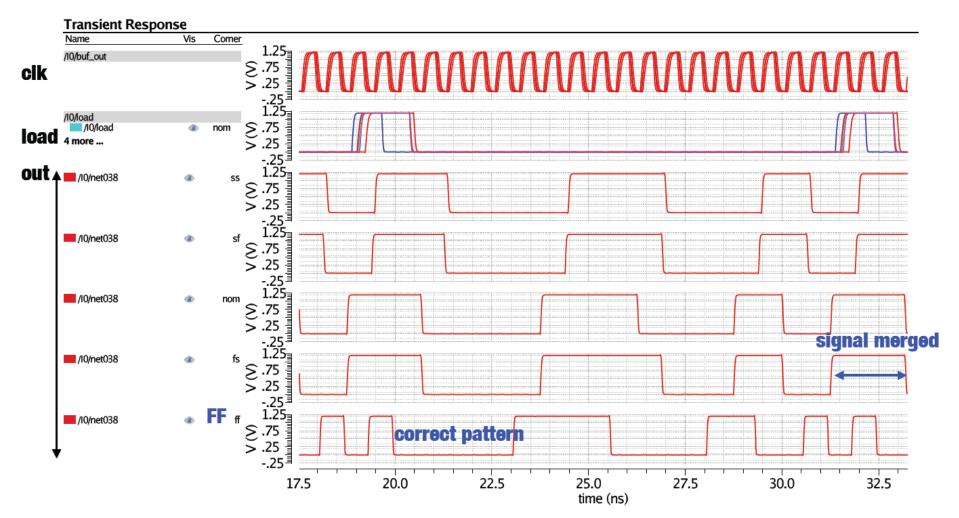

# Serializer Simulation with Modification (DHPT 1.1)

#### **Correct pattern can be obtained with all corners.**

- Origin of the bug: **understood**, **reproducible**

- Design modification: **identified**

- Re-design on schematic level: done

- Re-design on layout: **done** (homeopathic change)

- Simulation of extracted netlist (all corners): done

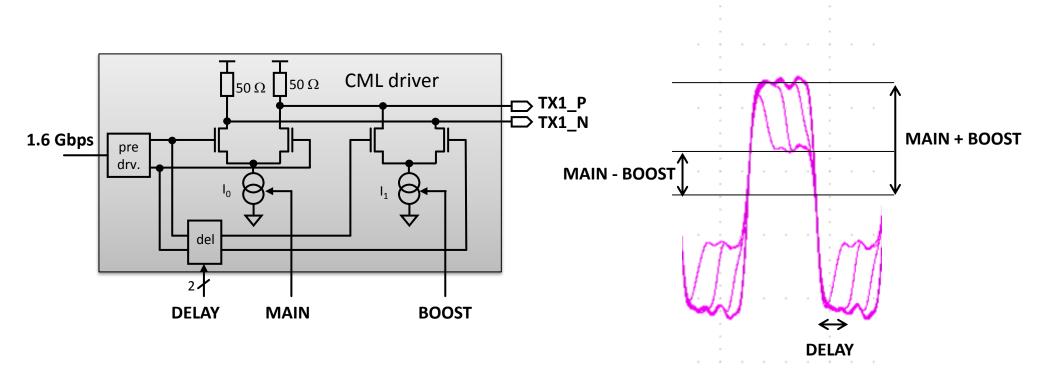

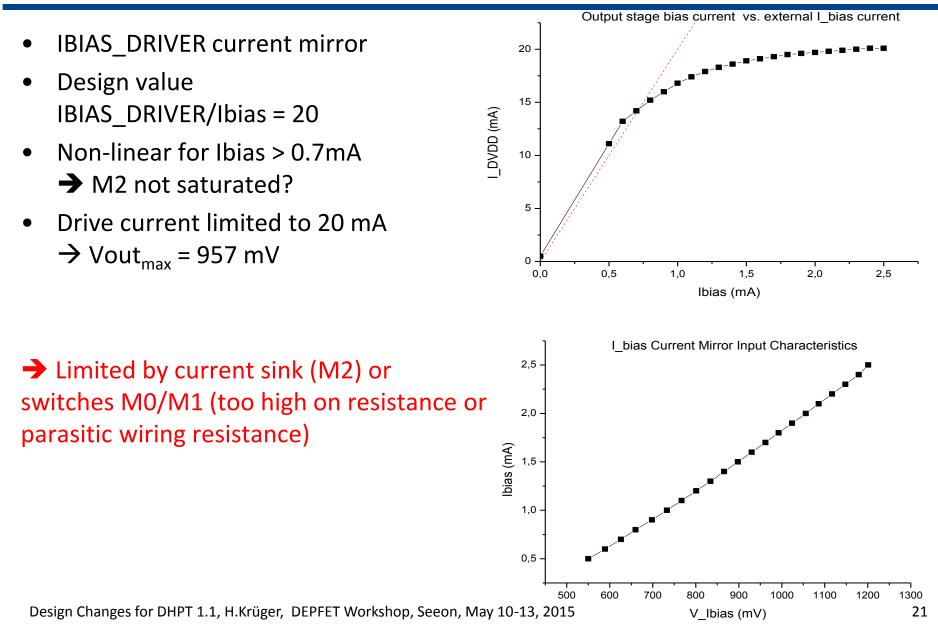

### **CML** Driver

universität**bonn**

- Works fine

- Try to enhance the performance (output swing) to have a bit more safety margin

#### T. Kishishita

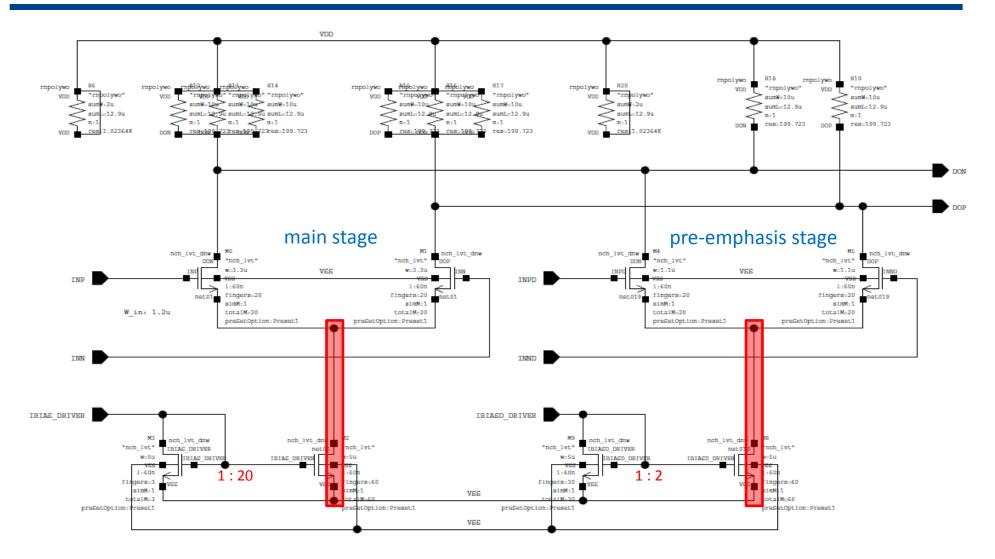

#### **Driver Schematic**

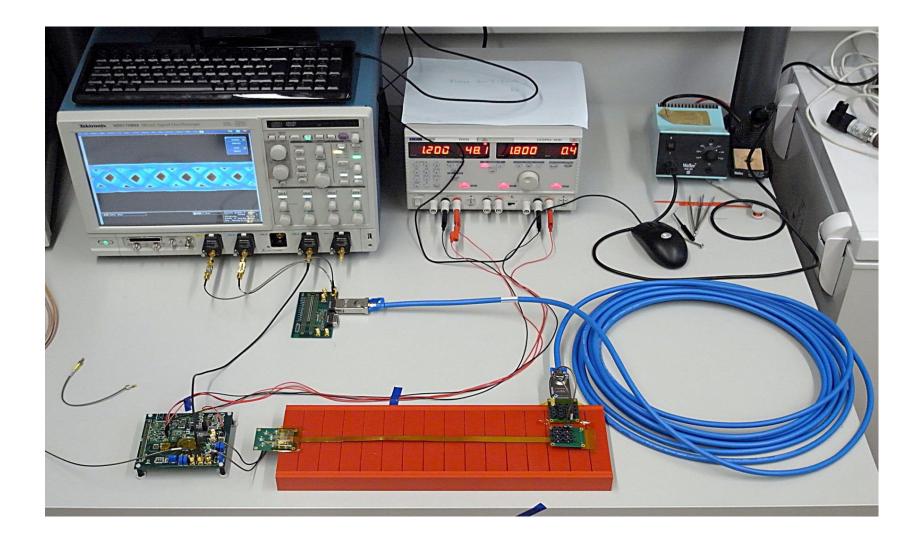

#### DHPT 0.1 – Test setup

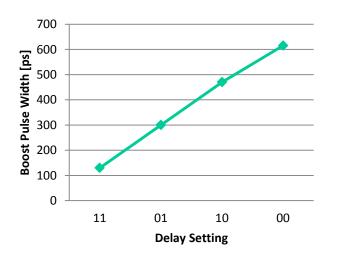

### **Delay Settings**

| Setting<br>SW[1:0] | Pulse Width<br>[ps] |  |  |

|--------------------|---------------------|--|--|

| 11                 | 130                 |  |  |

| 01                 | 300                 |  |  |

| 10                 | 470                 |  |  |

| 00                 | 615                 |  |  |

→ ~170 ps per delay buffer

800 MHz clock, different delay settings

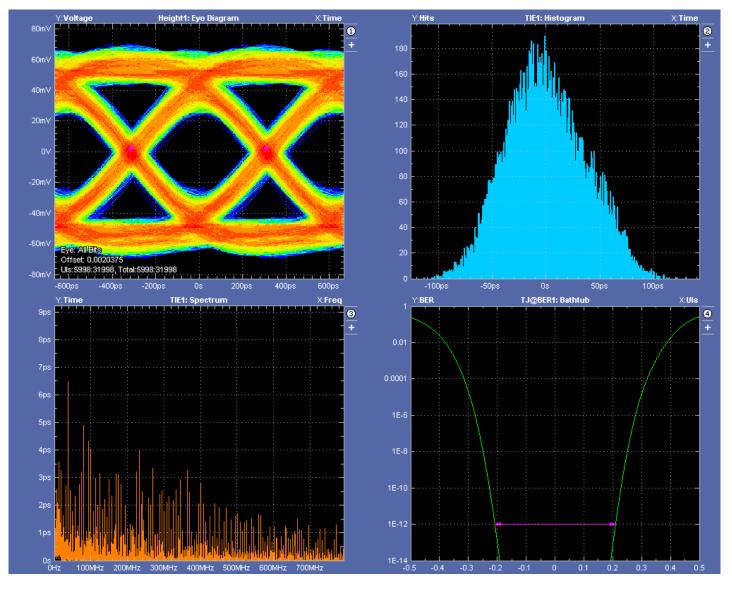

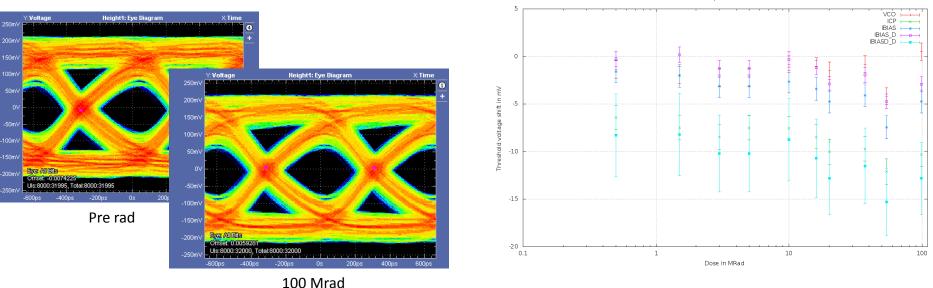

### **Signal Integrity Characterization**

- 1.6 Gbps LFSR-8

- 30 cm kapton cable

+ 20m AWG26

twisted pair cable

## **X-ray Irradiation**

-100

- TSMC 65nm TID tolerance:

- V<sub>THR</sub> shift (wide pMOS and nMOS only)

- PLL + Gbit link performance

- Up to 100 Mrad (60keV X-ray tube, Karlsruhe)

- Dose rates: ~300 kRad/h (initial)  $\rightarrow$  ~2Mrad/h (end)

- Annealing after each step: 80°C for 100 mir

#### No TID induced degradiation observed up to 100 Mrad

Voltage threshold shift vs absorbed Dose Shift with respect to Dose 0MRad

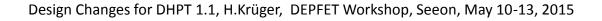

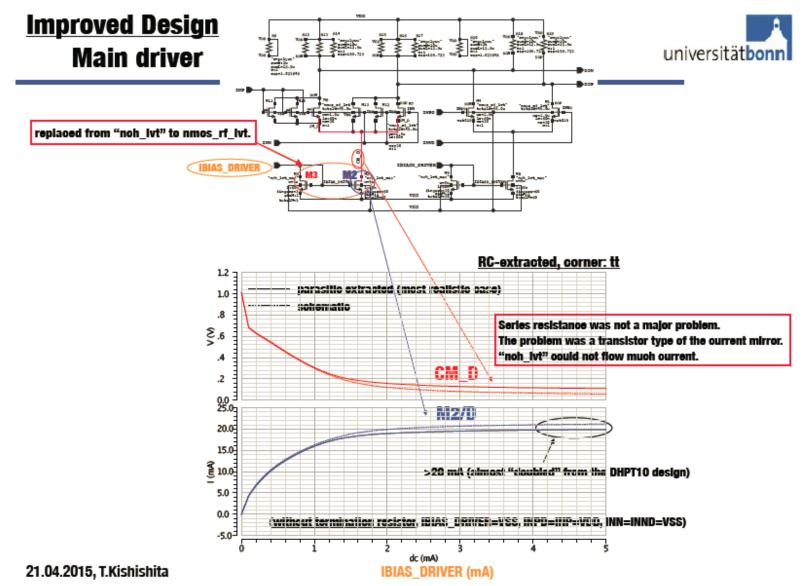

## **Main Output Current Mirror**

#### **DHPT 1.0 CML Driver**

#### **Improved CML Driver for DHPT 1.1**

Design Changes for DHPT 1.1, H.Krüger, DEPFET Workshop, Seeon, May 10-13, 2015

- Delay settings  $\rightarrow$  Ok

- minimum delay setting (SW[1:0]=11  $\rightarrow$  130 ps) shows best eye diagram for long cables

- − Possible optimization: make delay steps a bit smaller (170 ps  $\rightarrow$  120 ps, 7  $\rightarrow$  5 inverter per delay)

- Bias setting improvement

- Reduce parasitic resistance (wiring & vias)  $\rightarrow$  done (use of RF transistor layouts)

- Note: there is no substantial increase of output swing to be expected due to the 1.2V supply limit

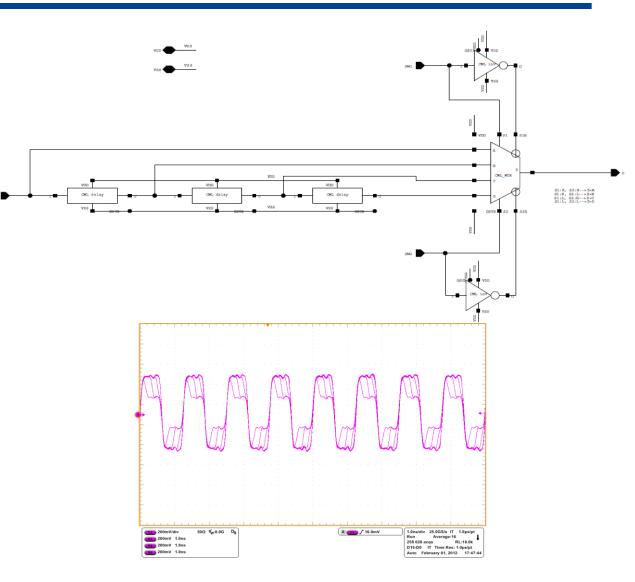

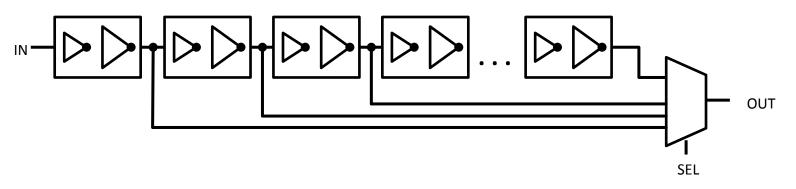

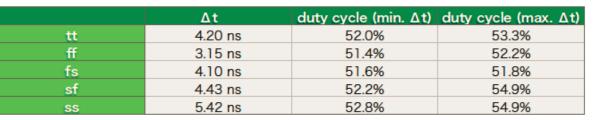

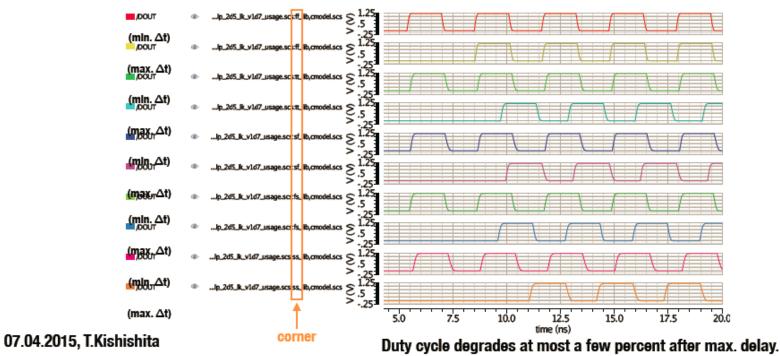

- Programmable delay lines made from std. cell delay elements (inverters)

- Inverter have usually unequal propagation delays for rising and falling edges (Asymmetry of PMOS-NMOS drive strength, process corners, W/L...)

- If all **inverters in the delay chain would be equal**, no duty cycle distortion would occur (differences in rising and falling edge delay would cancel out)

- However the std. cell delay elements consist of alternating no-equal sized inverters

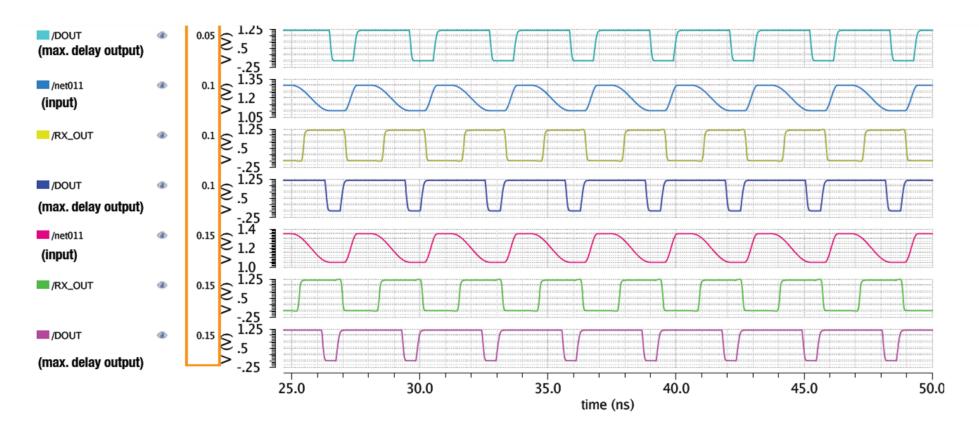

→ Duty cycle distortion increases with the number of delay elements used, i.e. the programmed delay time

#### **Data Synchronization Issues**

- Duty cycle distortion was overlooked during DHPT 1.0 sign-off

- See also measurements and scans done by Leo, Florian and Felix

• Custom delay elements made out of identical inverters

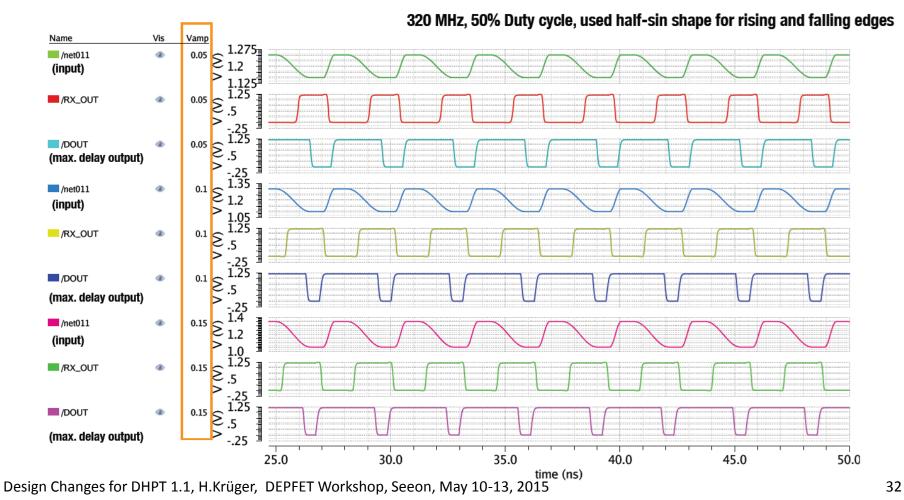

All corners covers 3.125 ns (← 320 MHz).

#### Max. delay time with extracted model

- Origin of the bug: **understood**, reproducible

- Design modification: **identified**

- Re-design on schematic level: done

- Re-design on layout level: work in progress

- Simulation of extracted layout (all corners): tbd

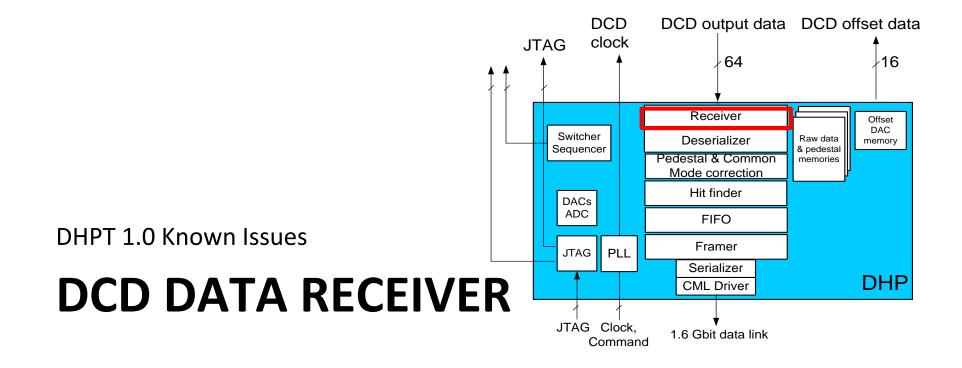

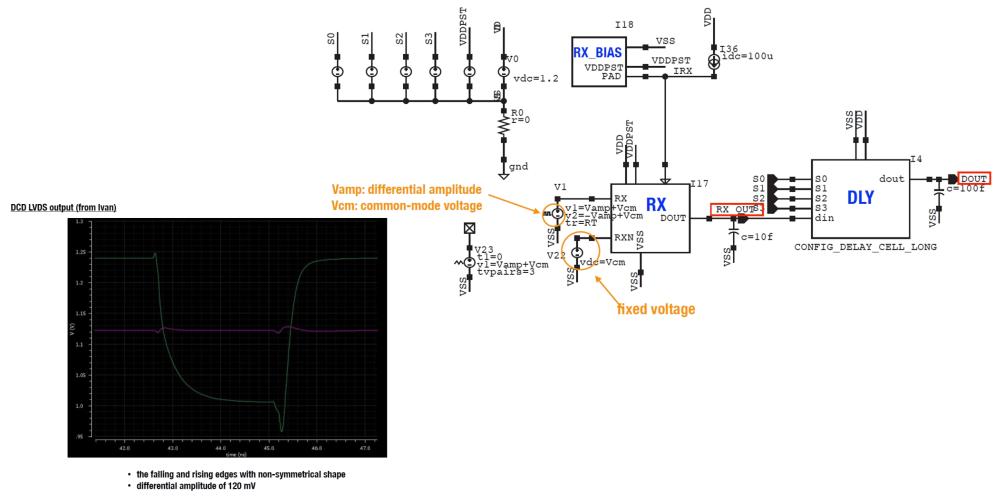

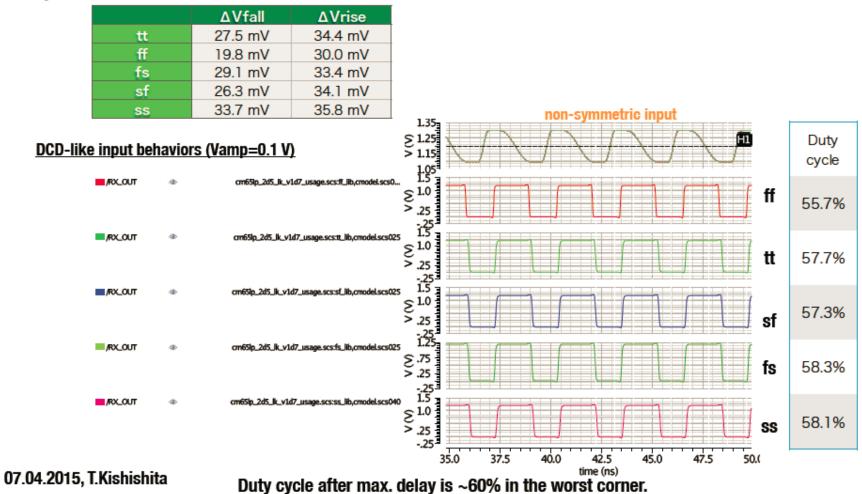

#### **DCD Data Receiver**

Single ended DCD data receivers based on LVDS receivers → low voltage single ended signaling (LVSE)

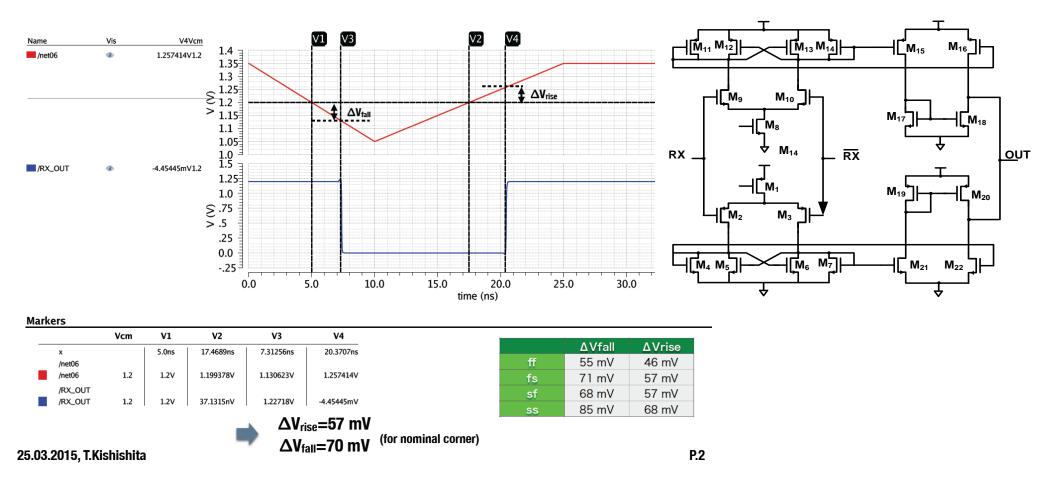

## **Duty cycle distortion**

- Asymmetric rise- and fall time of the input signal (+ effect of hysteresis)

- Delay elements (see later slides)

#### Dependence of the differential amplitude (Vamp, nominal corner)

## LVDS Receiver (DHPT 1.0)

• LVDS RX with build-in hysteresis

### **LVDS Receiver Design Modification**

#### FET sizes and layout modified to reduce hysteresis (~50% of the current DHPT1.0 design).

Hysteresis values with extracted model

Design Changes for DHPT 1.1, H.Krüger, DEPFET Workshop, Seeon, May 10-13, 2015

universität**bonn**

universität**bonn**

Enhancement: Reduced the input hysteresis to be less sensitive to duty cycle distortion due to asymmetric rise- and fall time of the input signal → done

#### ➔ Suggested improvements of the DCD output signal

- Symmetric rise- and fall times

- Higher signal amplitude

DHPT 1.0

# DATA PROCESSING FUNCTIONAL VERIFICATION

### **Data Processing**

- So far no issues seen

- Things to look into in more detail:

- Processing of high occupancy data

- Gated mode

- Power on configuration

- → Need more system tests to assess the need of design changes

→ If not absolutely needed we would like to avoid the process of re-synthesizing the design (lot of work!!!)

What is really needed (no "nice to have" features)?

- Include Chip ID (JTAG programmable) in data header (needed?)

- Modifications for Gated Mode ?

- What else?

- DHPT offsets  $\rightarrow$  DCD

- DCD/DHPT (data, offset and JTAG) communication after TID damage

- High occupancy data processing

- Gated mode

- Triggering

- Raw data transfer

- JTAG timing (next DCD should follow the industrial standard wrt clock edges)

- SEU x-section for realistic neutron energy spectrum (calculate from 24 GeV proton data or re-measure)

- Power-up configuration Ok?

- ...

## **Summary & Outlook**

universität**bonn**

- Bugs / Enhancements of the full custom blocks

- − Serializer bug  $\rightarrow$  fixed  $\checkmark$

- − CML driver enhancement -> done ✓

- Delay element issue  $\rightarrow$  fixed, layout work in progress ( $\checkmark$ )

- Data reciever robustness  $\rightarrow$  fixed, layout work in progress ( $\checkmark$ )

- Digital data processing enhancements

- Not foreseen (yet)

- Sytem test, system test, system tests!

- Final Design Review (including DCDB and Switcher): 15/16.7.2015

- DHPT 1.1 submission in August 2015 → chips available for tests around Dec. 2015

## BACKUP

Design Changes for DHPT 1.1, H.Krüger, DEPFET Workshop, Seeon, May 10-13, 2015

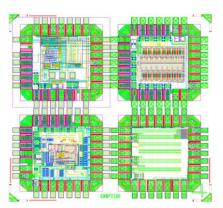

## **DHPT 1.1 Production**

- Submission:

- ~August 2015

- Two slots per month, 12 weeks turn-around

- Chips available by Dec 2015

- TSMC 65nm MPW submissions costs

- 12 mm<sup>2</sup>, one wafer (100 chips) included: 59 TUSD + 12 TUSD for bumping

- Extra 12" wafer (100 chips): 9 TUSD

- Two MPW runs per month, turn-around ~12 weeks

- DHPT 1.1 production

- MPW + 9 extra wafers (1000 chips)

- Extra wafers to be ordered after successful verification

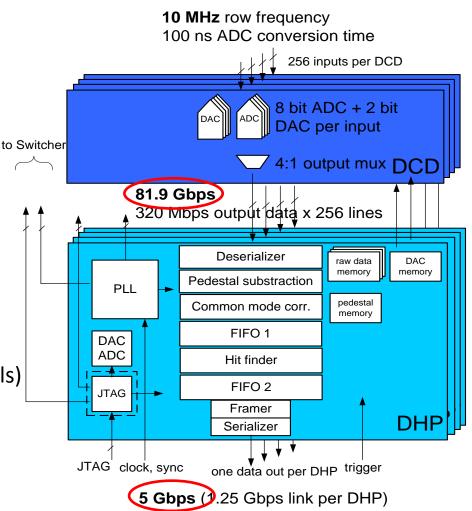

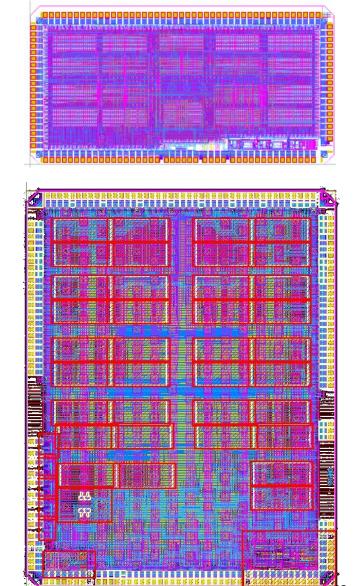

## **Data Handling Processor – Design History**

#### Started with IBM 90nm technology in 2010

- DHP 0.1

- Half size prototype, 2 x 4 mm<sup>2</sup>, C4 bumps

- Basic digital data processing

- PLL (1.6 GHz) + High speed serial link

- ➔ Successful verification

- DHP 0.2 (sub. mid of 2011)

- Full size chip, 3.2 x 4.3 mm<sup>2</sup>

- Full data processing, added switcher sequencer and bias generators

- Improvements in link performance (preemphasis), buffer size, and data format

- ➔ Successful tests & system operation (some issues with max. speed of CMOS clock output)

Forced to abandon 90nm IBM process → chosen 65nm TSMC, started with small prototype chips to verify full custom blocks and rad. hardness performance

- DHPT 0.1 (Oct. 2011)

- PLL (1.6 GHz)

- High speed TX (CML driver)

- Bias generators (U Barcelona)

- Memory SEU test structures

- DHPT 0.2 (June 2012)

- LVDS RX & TX

- Temperature sensor (U Barcelona)

**Data Handling Processor – Design History**

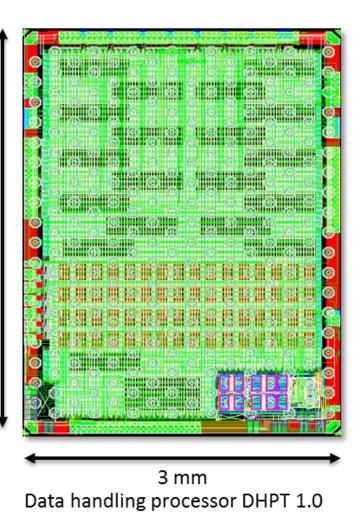

- DHPT 1.0 (Aug. 2013)

- Full size chip

- Includes all pre-verified full custom blocks

- Footprint & electrical compatible to DHP 0.2

- Improved memory & processing resources wrt. DHP 0.2

universität**bonn**

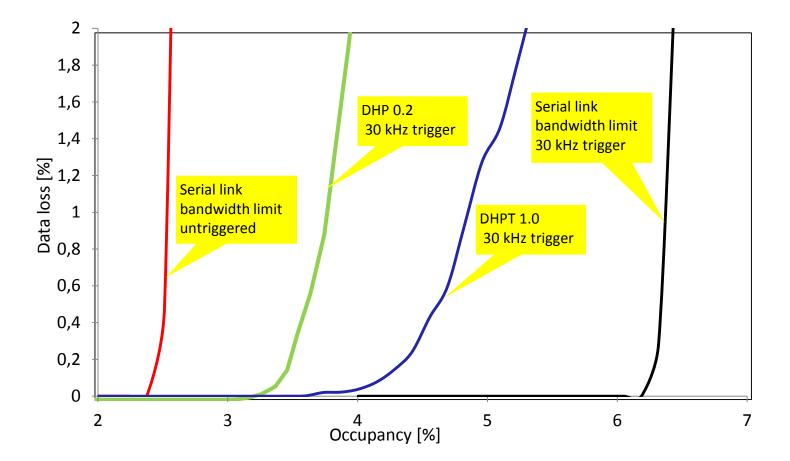

### **Expected DHPT 1.0 Data Losses**

- FIFO 1: 64 FIFOs in front of the hit finder  $\rightarrow$  256 words deep (DHP 0.2  $\rightarrow$  16)

- FIFO 2: between hit finder and serializer  $\rightarrow$  4096 word deep (DHP 0.2  $\rightarrow$  512)

universität**bonn**

#### DHPT 1.0

## **COMMAND TIMING**

Design Changes for DHPT 1.1, H.Krüger, DEPFET Workshop, Seeon, May 10-13, 2015

## **Notes on DHP Command Timing and Format**

- **One control word per row period** is send synchronized to the DHP clock GCK (76.35 MHz)

- The control word (8 bits) transmits four independent commands: <RST|TRG|VTO|FSYNC>

- RST: Reset, level sensitive, pulse width selects different reset modes

- TRG: Physics trigger, level sensitive, pulse width selects raw data frame size

- VTO: Veto (gated mode), level sensitive, selects veto sequence while on

- FSYNC: Frame sync, edge sensitive

- The state of every command is encoded in two bits (Manchester code)

- <10> = on

- <01> = off

- Two additional control words are accepted (broken Manchester code)

- <00 01 11 01> synchronization sequence, should be used as IDLE

- <11 10 00 FSYNC> CALTRG (mem\_dump): calibration data trigger, edge sensitive, allows simultaneous FSYNC command transmission

- The command latency in the DHP core is in the order of a few GCK cycles

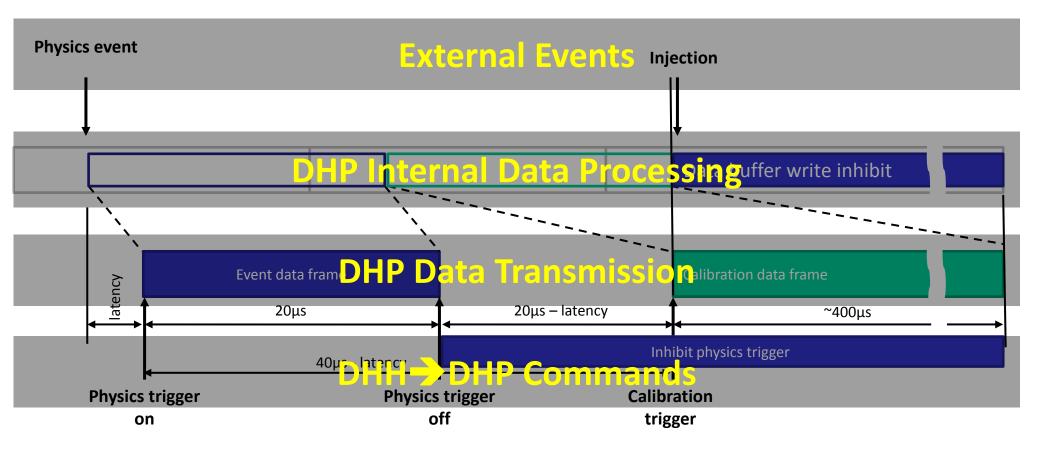

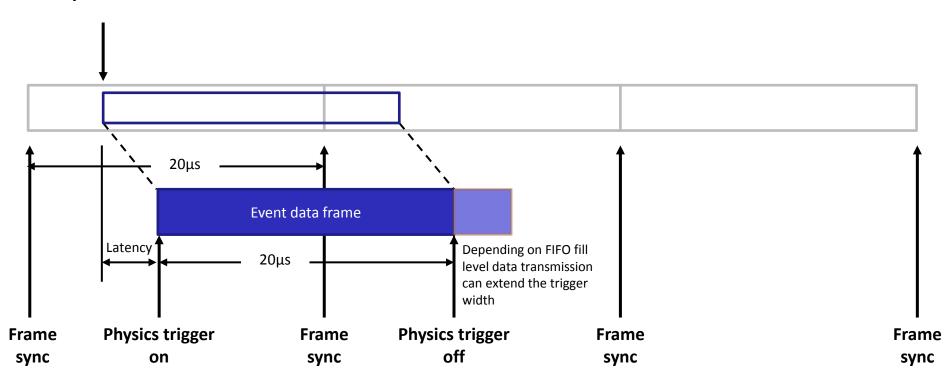

## DHP timing for triggered data taking

- The transmitted *Event data frame* starts with hits from [row<sub>m</sub>, raw data frame<sub>n</sub>] and ends with [row<sub>m-1</sub>, raw data frame<sub>n+1</sub>]

- The row index m is a function of the phase between *trigger* and *frame sync*

- The trigger command is level sensitive and its width selects the size of the raw data frame to be processed

- The default width is 1536 GCK cycles (8 GCK cycles/row · 192 rows/frame) Design Changes for DHPT 1.1, H.Krüger, DEPFET Workshop, Seeon, May 10-13, 2015

## DHP timing for calibration data taking

- The calibration trigger can be send any time within a frame period

- If the previous event data transmission is not yet finished (case B), the calibration data transmission will be put on hold until the FIFOs are flushed. In some cases remaining event data still might be send after the calibration data frame (**not recommended**).

- The transmitted *Calibration Data Frame* is re-sorted and always starts with [row<sub>0</sub>, raw data frame<sub>n+1</sub>] and ends with [row<sub>max</sub>, raw data frame<sub>n</sub>]

- Programmable row<sub>max</sub> and defines the raw data buffer size to transmit (default m= 191)

For better readability periodic *frame sync* commands are omitted in this and the following drawing s Design Changes for DHPT 1.1, H.Krüger, DEPFET Workshop, Seeon, May 10-13, 2015

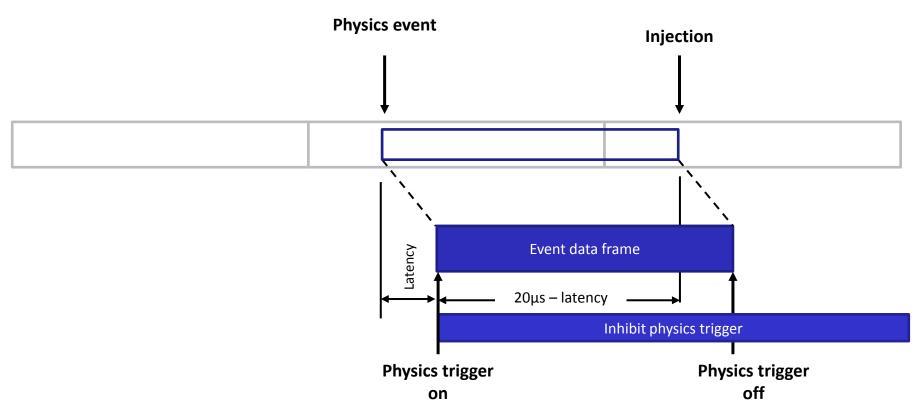

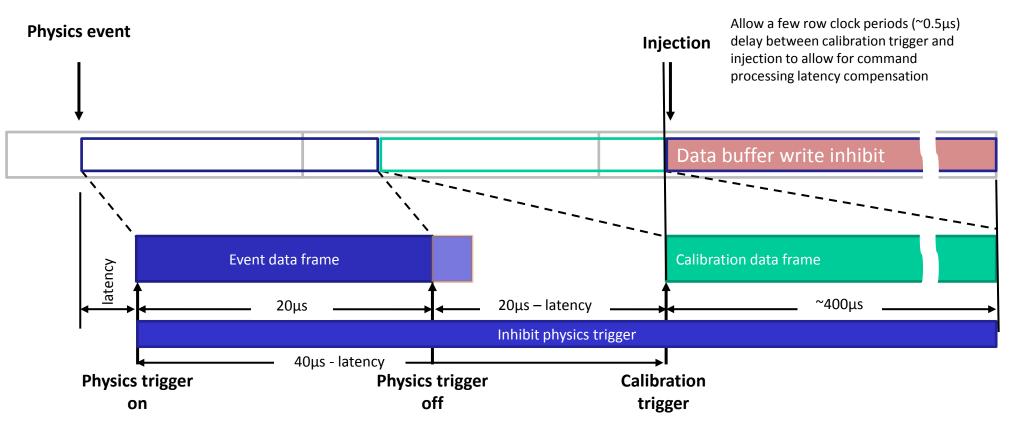

# DHP timing for injection sequence w/o calibration data taking

The suppression of physics triggers should start **20µs** – **latency** before the injection starts.

# DHP timing for injection sequence with calibration data taking

- The suppression of physics triggers should start **40µs latency** before the injection starts.

- Calibration trigger should only be send if the previous event data transmission has finished