# **DEPFET IB-Meeting**

# **Report of PL**

- Recommendations from BPAC

- General Schedule

- Preparations of Pilot Run: ASICs

- SMD Baseline and Fallback

- Preparation for BEAST Phase 2

- Milestones for the Coming 2 Years

- Status Common Fund

- Dates for next Meetings (B2GM, VXD Workshop)

- Proposal for Bylaw Changes (Election of TC)

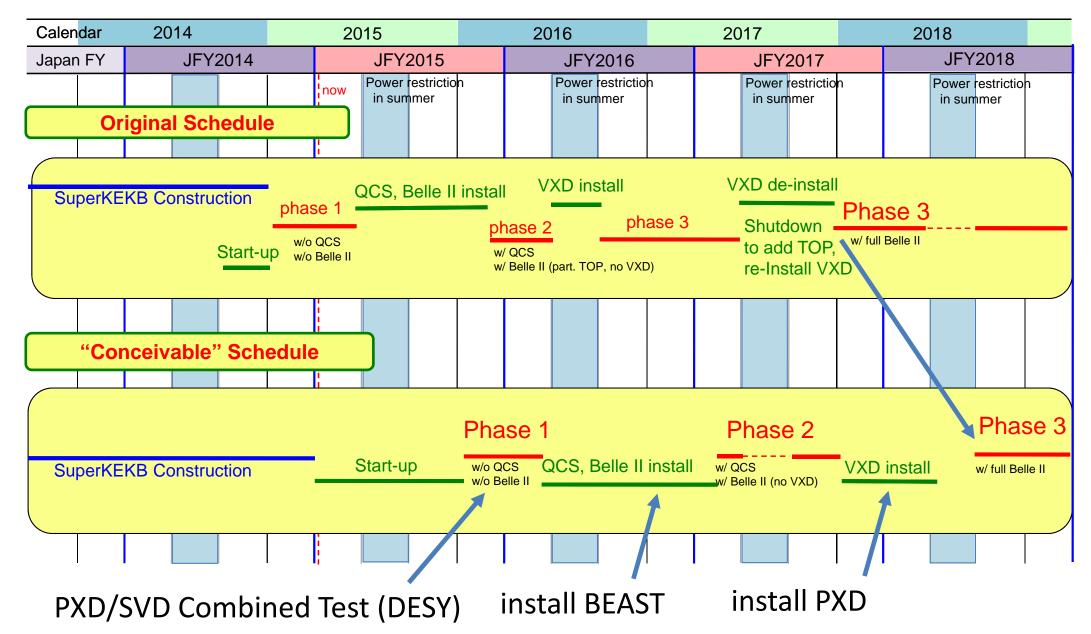

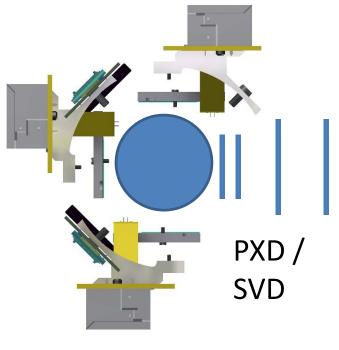

Some topics relevant for the PXD (schedule)

- Financial crisis of SuperKEKB operation hopefully settled: start of machine ("Phase 1") in Jan. 2016 seems possible

- BPAC Review: helpful presentations from PXD side on overall status: quite good "marks" received

#### Citation from the BPAC report:

The pixel detector project is on a good track. The team has successfully verified crucial steps in the production process, which gives strong confidence in the forthcoming detector production. However, the overall schedule is very tight. The committee thinks that the construction of a mockup for the cooling system must be completed according to plan so that crucial cooling tests of the components and the whole system can be started as soon as possible.

- .2 Concerns

- Although the introduction of a pilot run for production is a good tactical move and maximises confidence in proper operation of the detector, sensor production remains a critical step in the overall process.

- Balancing the availability of resources and ensuring that high priority issues discussed below get adequate, timely attention is a concern to the committee.

#### 5.1.3 Recommendations

- The joint test beam with the SVD remains a very important system test and the committee strongly encourages the collaboration to give it the priority.

- The thermal mockup of the VXD is critically important. There have been several schedule delays. The committee urges that the thermal mockup test commence as soon as possible.

- The detailed mock-up of the assembly of the two sub-detectors and their integration with the beam line elements is highly commendable. The committee recommends that the attention to detail be kept up and even increased, especially with regard to the cooling requirements.

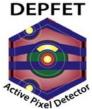

## **Status of ASICs**

- issues documented

(see Hans' list, DEPFET Twiki)

- will be used also for the pilot run production

- submission by Aug. 31

### Some concerns:

- bumping of SWB

- testing of DCD / SWB before flip-chipping

### Needed for final production:

- 1080 SWG (all sensors)

- 720 DCDpl

- 720 DHPT

## **Status of Kapton Cable**

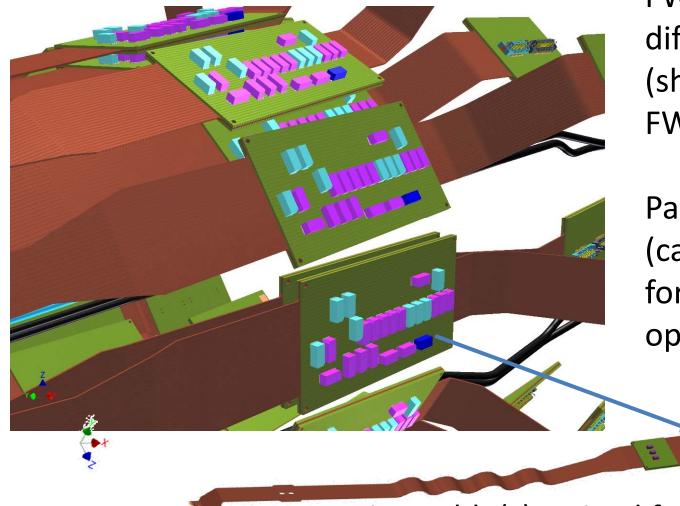

Final design of Kapton cable ("outer BWD"), including passive elements, is nearing completion (4 types: FWD, BWD, inner, outer)

FWD and BWD sides different geometry (shown here is the FWD side)

Passive elements (capacitors) necessary for Gated Mode operation

First cable(s) arrived from Taiyo: test in BN + M

C. Kiesling, DEPFET IB Meeting, Kloster Seeon, May 11, 2015

Yield estimate (metallization, DEPFET): = 0.8 x 0.6 ~ 0.50

- have a safety factor **1.6** for the rest of the production steps

incl. metallization

excluding pilot

|                                                                          | Class 0/1 | Class 2-5 | Sum                                        | PXD | Safety<br>factor |

|--------------------------------------------------------------------------|-----------|-----------|--------------------------------------------|-----|------------------|

| inner                                                                    | 38        | 22        | 60                                         | 16  | 1.6              |

| outer                                                                    | 74        | 46        | 120                                        | 24  | 2.0              |

| Sum                                                                      | 112       | 68        | 180                                        | 40  | 1.9              |

|                                                                          |           |           |                                            |     |                  |

| Pilot run with 3 "hot" wafers<br>10% of total wafers: 6 inner, 12 outer) |           |           | Taking into account<br>class 0 and 1 only, |     |                  |

| Item                                       | Where                    |  |

|--------------------------------------------|--------------------------|--|

| DEPFET Sensor (Phases I, II and III)       | Semiconductor Lab (HLL)  |  |

| Flip chipping of ASICs                     | IZM Berlin               |  |

| mount SMDs (classify, no immediate rework) | NTC / IFIC (Plan B: HLL) |  |

| Add Kapton cable, wire bonding             | MPI Munich               |  |

| Gluing of two modules (= "ladder")         | MPI / HLL                |  |

| Assembly of PXD half shells                | MPI Munich               |  |

| Commissioning PXD                          | MPI Munich               |  |

| Assembly of PXD and Beam pipe              | KEK clean room (B1)      |  |

| Completion of assembly with SVD (= "VXD")  | KEK clean room (B1)      |  |

| Commissioning of VXD                       | KEK clean room (B1)      |  |

| Installation of VXD into Belle II          | on SuperKEKB beam line   |  |

\_

Phase 2:

Belle II on beamline, fully installed **except VXD** Final Focus System (QCS) installed for the first time. Final beampipe and HM masks around IP First attempt to collide beams and achieve 1x10<sup>34</sup> /cm s

- Determine particle/photon fluxes for the individual background contributions (syn.rad., Touschek, rad. Bhabha, 2γ)

- Study injection bg and exercise gated mode operation of VXD

- Determine bg status safe for PXD/SVD, exercise H/W interlock, radiation & environmental monitoring (!)

- Install one sector (=6 ladders) of PXD and SVD in accel. plane

## **BEAST Phase 2: The "VXDP2"**

CALICE (ILC) scintillators and new Hamamatsu SiPM (225°, 315°)

> ATLAS IBL Pixels, cooled by SCB (90°, 180°, 270°)

### Possible plan: Test new devices at DESY before assembly

a ..... a ..... a ....

## **Construction of CO2 Unit (IBBelle)**

- Pilot Run with first "hot wafers" (test by summer of 2015) (bottlenecks: DCD / SWB tests, SMD mount procedure)

- DESY Thermal Test (includes PXD and SVD dummies) in 2015

- Build IBBelle by fall of 2015, complete commissioning by 3/2016

- Build 2 ladders (from Pilot Run) for DESY VXD Beam test (spring 2016), prepare Slow Control for VXD

- Final ASICs by spring 2016 (on pilot run sensors for BEAST 2)

- Build BEAST 2 sensor systems (FE-I4 and Scint/SiPM) by end 2016

Finish PXD module / ladder production by spring 2017

C. Kiesling, DEPFET IB Meeting, Kloster Seeon, May 11, 2015

CF is hosted at MPI, administered by Ms A. Fleischer (head of accounting department)

all account actions (contributions and spending) are entered in MPI's accounting system under PHYS 0397 (EXCEL tables are provided upon demand)

Contriubtions are voluntary, based on MoU

Project spending proposed by PL and endorsed by IB some examples:

contributions to IBBelle grounding (ITA), engineering manpower (AIM) ...

present balance: 187 kEur

### B2GM @KEK: June 22 -26, 2015

Satellite Meeting (BEAST 1 & 2): June 20-21, 2015

VXD (PXD + SVD) Workshop (follow-up of Pisa Meeting):

Proposal: Trieste, Sep. 9-11, 2015 (only option)

VXD Mechanics Meeting @ MPI: Sep 7-8, 2015 (Cable duct from dock to outside, pressure tests (300 bar) for non-CE certified parts of CO2 cooling chain (SCBs, cooling tubes etc.)

Some IB members expressed wish to (also) elect the TC

This would need a change of the DEPFET MoU Bylaws

Proposal by PL (to be discussed):

Old:

"The Technical coordinator (TC) is proposed by the PL and approved by PXD IB for 2 years"

New:

"Candidates for the Technical Coordinator (TC) are proposed by the PL and the PXD IB. The TC is elected by the PXD IB for a term of 2 years, renewable".