**DESY TB Summary**

F. Lütticke, C. Marinas, T. Obermann University of Bonn

B. Schwenker, U. Stolzenberg University of Göttingen

**DEPFET Collaboration**

#### **Outline**

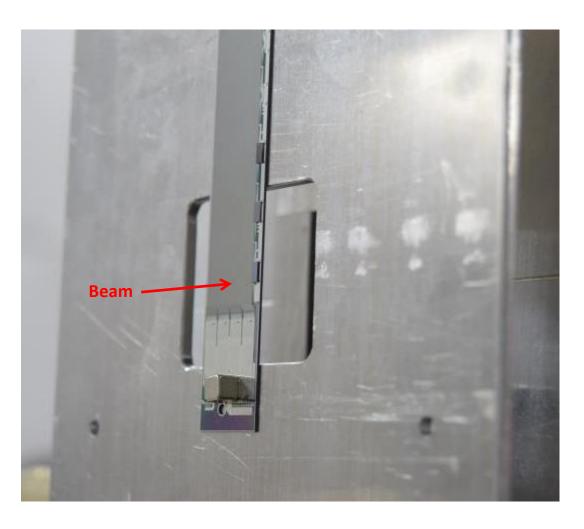

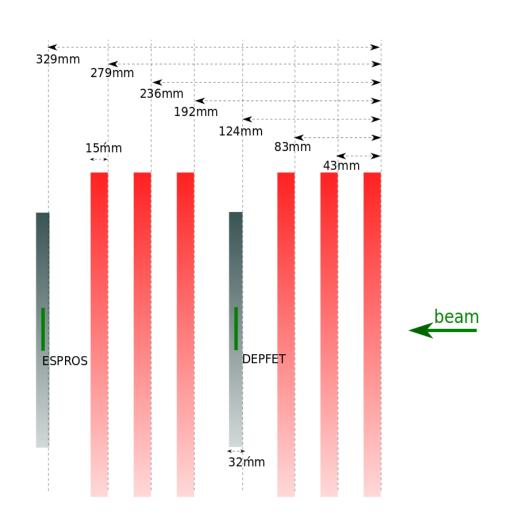

DESY Test Beam 23<sup>rd</sup> – 30<sup>th</sup> March 2015

Area T22

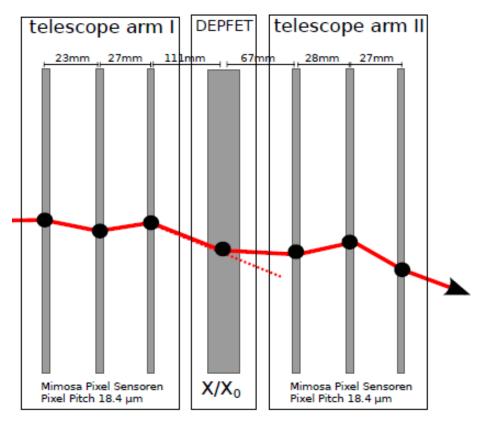

AIDA Telescope

2-6 GeV electrons

Parasitic users in Bonn-CMOS week

Program:

Material budget estimation Hybrid 6.0 studies

Online logbook and **preliminary** results:

https://docs.google.com/spreadsheets/d/1VUyBP6Bk7Jm9XEykCOhwjvcxhtF8ere X6gGF1fEiGs/edit?pli=1#gid=0

2

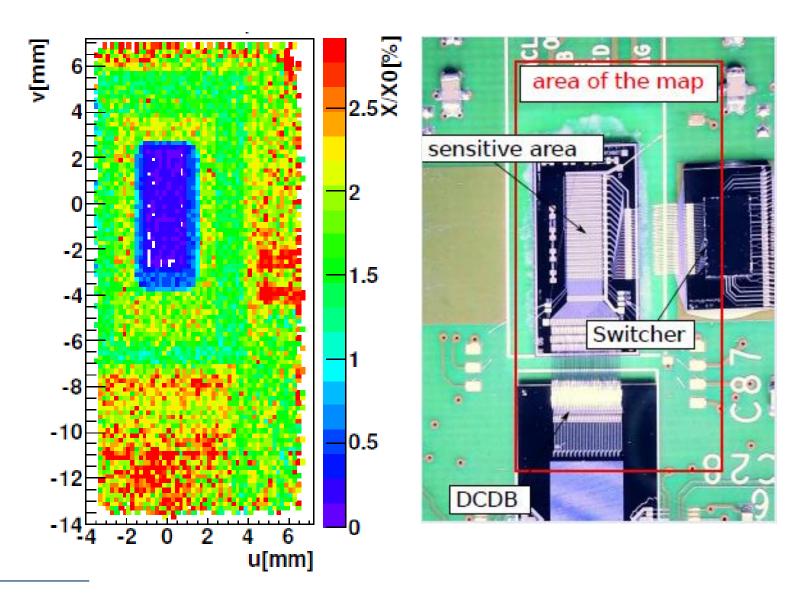

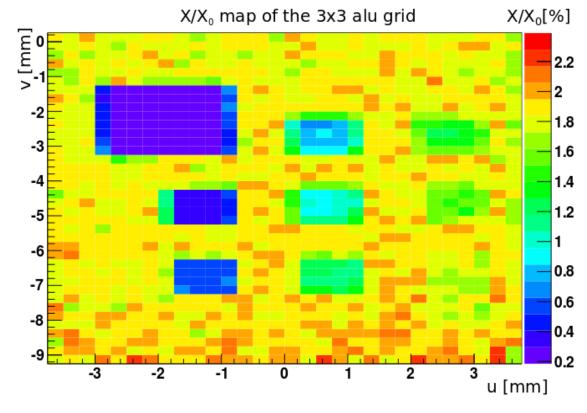

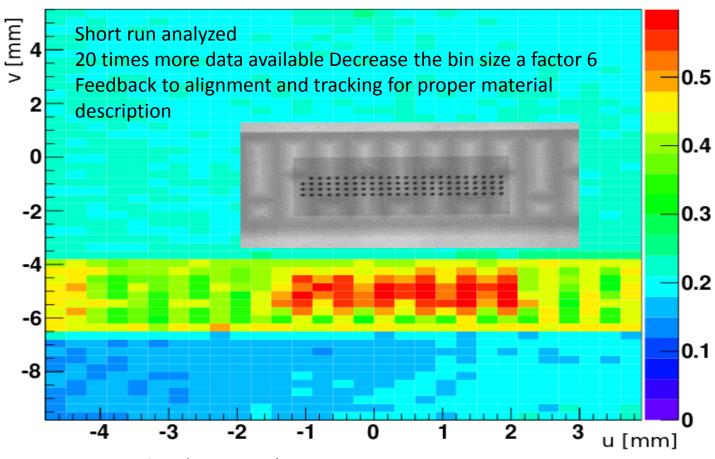

# X/X0 Map Using Tracks

Use tracks from the telescope to reconstruct angle distributions from multiple Coulomb scattering on a central plane (Highland's equation)

# X/X0 Map Using Tracks

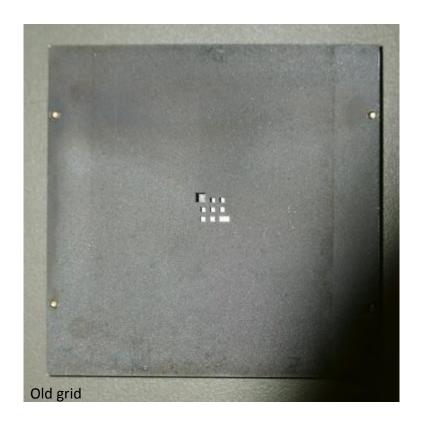

#### **Calibration Alu Grid**

New Alu grid 3x3 holes grid (each layer adds 0.2 mm of Aluminium) 9 holes, side length 1 mm and 2 mm

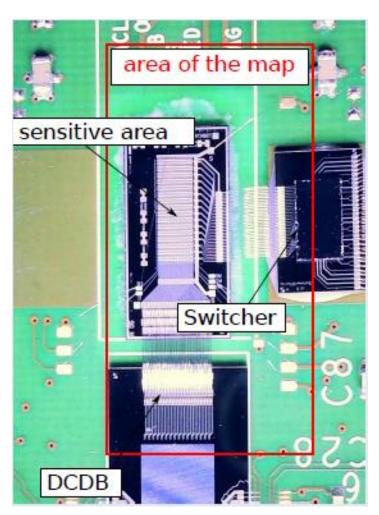

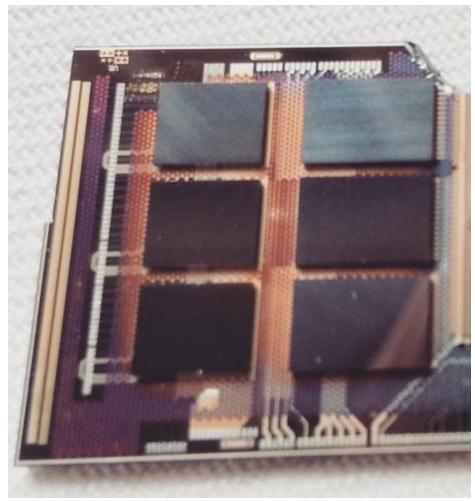

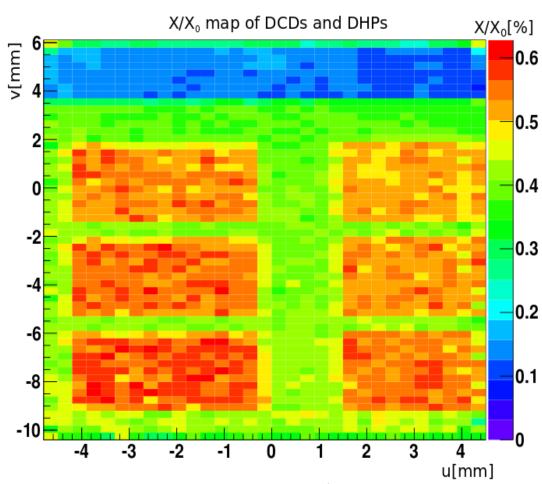

# **Material Budget ASICs**

Large PXD6 matrix Thick silicon in the end of ladder DCDBv2 and DHP0.2

→ Remember: In Belle II, these don't contribute to the material budget

Potential of our algorithm

Ability to resolve small structures

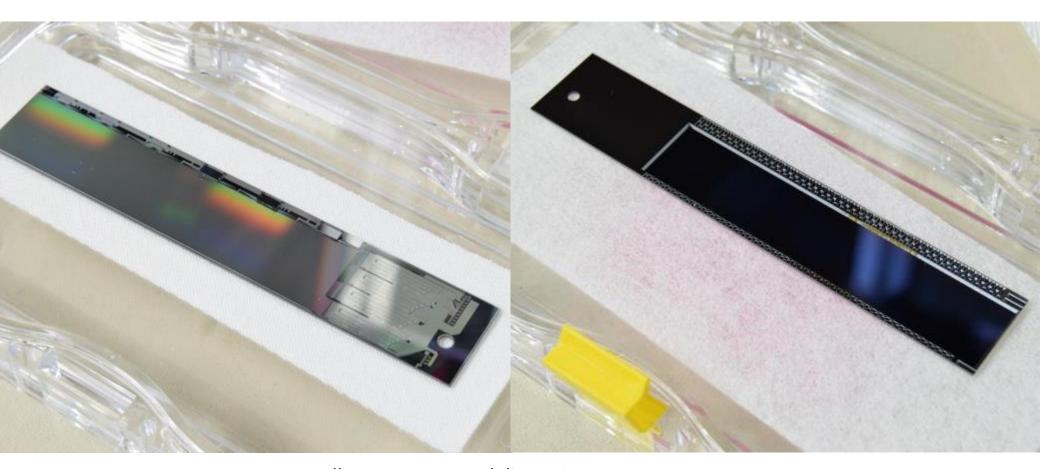

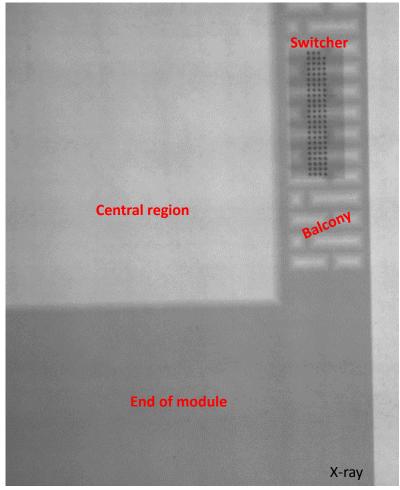

# **PXD9 Mechanical Sample**

Belle II geometry and dimensions 75  $\mu m$  thin + Alu 3 Switchers on the balcony

# **Set Up**

cmarinas@uni-bonn.de

# X/X0 Map Switcher

Thin 'sensitive' area Solder balls under the Switcher Even the grooves under the balcony are seen!

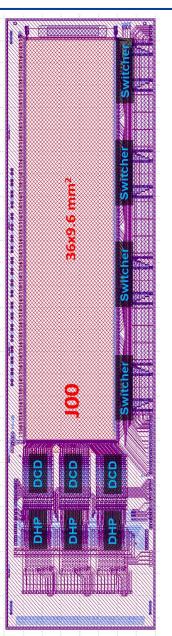

## Hybrid 6.0

PXD6 - J00 on Hybrid 6

Capacitive Coupled ClearGate

50x75 μm2 pitch

768 drain lines (256x3 DCD/DHP)

120 gate/clear lines (4 Switcher)

DCDBv2, DHP0.2, SwitcherB1.8G Speed: 250 MHz → Broken during power down

PXD6 - I00 on Hybrid 6

Capacitive Coupled ClearGate

50x100 μm2 pitch

768 drain lines (256x3 DCD/DHP), only DCD0, DHP0 assembled

120 gate/clear lines (4 Switcher)

DCDBv2, DHP0.2, SwitcherB1.8G Speed: 250 MHz

DHE and Power Supply

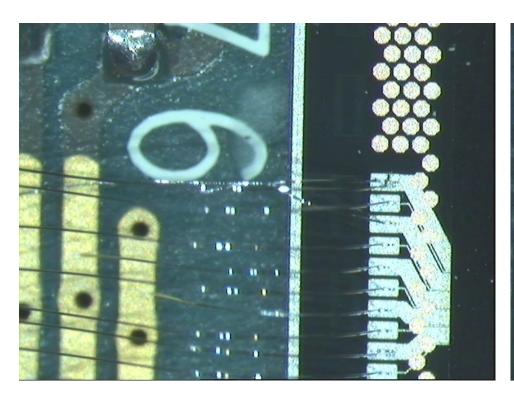

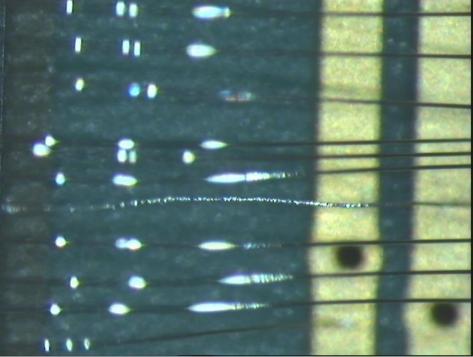

### **Melted Wirebonds**

Bug in the power down sequence → Fixed (some wire bonds melted)

cmarinas@uni-bonn.de 11

# Hybrid 6.0

12

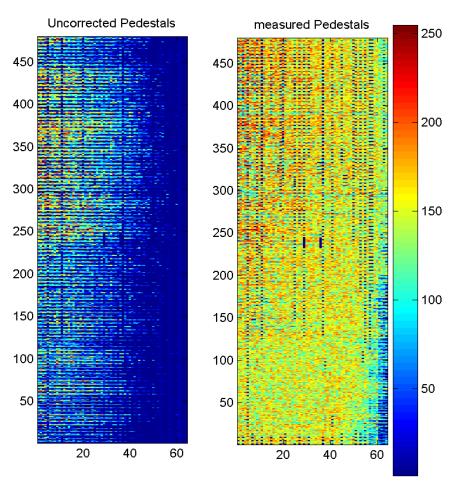

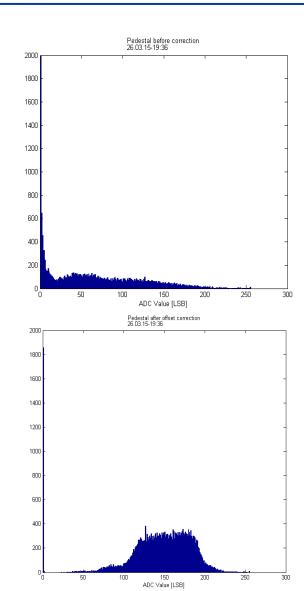

#### Pedestal compression 100

Power routing: the 3 DCDs show different pedestal distribution. Gradient over columns observed in J00

## PXD6-I00 on Hybrid 6

- Scan trigger delay settings

- Scan different areas of the sensor

- Scan different thresholds (4, 6 and 8)

- Scan main voltages

→ Final results in Seeon

cmarinas@uni-bonn.de 13

Thank you