## **PXD Electronics**

DEPFET

C. Marinas University of Bonn

**DEPFET Collaboration**

#### • Belle II PXD ASICs review II

https://indico.mpp.mpg.de/conferenceDisplay.py?confld=3736

#### • PXD ASICs Planner 2015

https://docs.google.com/spreadsheets/d/10VASA4uVWEmoNZSZnSXNDR2uCe2bCWhkqrn flKvhg\_g/edit#gid=2101922850

• DCD and Switchers Report

https://indico.mpp.mpg.de/getFile.py/access?resId=0&materialId=2&confId=3736

### **Structure of the Review**

#### Wednesday, 15 July 2015

| 10:00 - 10:20 | Introduction, Schedule, Overview 20'<br>Sprecher: Laci Andricek (MPG Halbleiterlabor)<br>Material: Sildes from Oct. 2014 review  |                      |                                                                  |  |

|---------------|----------------------------------------------------------------------------------------------------------------------------------|----------------------|------------------------------------------------------------------|--|

| 10:20 - 10:40 | DEPFET Drain Current Dispersion - What to expect a Sprecher: Rainer Richter (MPG HLL)                                            | 20'                  | Interface to the DEPFET                                          |  |

| 10:40 - 11:00 | DEPFET Drain Current Dispersion - impact on Dynam<br>Sprecher: Florian Luetticke (Uni Bonn)                                      | nic Range 20'        |                                                                  |  |

| 11:00 - 11:20 | Coffee Break                                                                                                                     |                      |                                                                  |  |

| 11:20 - 11:40 | Summary of the recent X-Ray irradiation campaign A<br>Sprecher: Benjamin Schwenker (University of Göttingen)<br>Material: Slides | 20'                  | System tests before and after irradiation                        |  |

| 11:40 - 12:00 | Gated Mode seen from the DCD/DHP and SWB pers<br>Sprecher: Christian Koffmane (MPI Halbleiterlabor)<br>Material: Slides          | pective 20'          | Gated mode status                                                |  |

| 12:00 - 13:00 | Lunch                                                                                                                            |                      |                                                                  |  |

| 13:00 - 14:00 | DCD-DHPT Interface & DHPT Re-design Status 1h0'                                                                                  | Г                    | DHPT-DCD interface                                               |  |

|               | Sprecher: Hans Krueger (Uni Bonn)<br>Material: Slides 🔮                                                                          |                      | Detailed talks by the designers                                  |  |

| 14:00 - 14:20 | Coffee Break                                                                                                                     |                      |                                                                  |  |

| 14:20 - 15:05 | DCD - Status and Plans 45'<br>Sprecher: Ivan Peric (KIT)                                                                         |                      | Status                                                           |  |

|               | Material: DCD/SWB related answers to last review (Ivan)                                                                          | <b>M</b>             | <ul> <li>Status</li> <li>Response to the prev. review</li> </ul> |  |

| 15:05 - 15:50 | SwitcherB - Status and Plans 45'                                                                                                 |                      | - Submissions plans                                              |  |

|               | Sprecher: Ivan Peric (KIT)                                                                                                       |                      |                                                                  |  |

| 15:50 - 16:35 | Closed Session 45' The                                                                                                           | ursday, 16 July 2015 |                                                                  |  |

09:00 - 12:00 Q/A, Discussions

#### cmarinas@uni-bonn.de

•

| Yield (%) |       |       |       |  |  |  |

|-----------|-------|-------|-------|--|--|--|

|           | W30   | W35   | W36   |  |  |  |

| IF        | 75.0  | 100.0 | 100.0 |  |  |  |

| OF1       | 100.0 | 100.0 | 100.0 |  |  |  |

| OF2       | 100.0 | 100.0 | 100.0 |  |  |  |

| OB1       | 99.8  | 99.4  | 0     |  |  |  |

| OB2       | 99.6  | 0     | 99.8  |  |  |  |

| IB        | 100.0 | 0     | 100.0 |  |  |  |

- W30-OB1, W30-OB1, W36-OB2 - W30-OF1, W30-OF2

- W30-IB and W35-IF

- W35-OF1 and W35-OB1

- Wafer level testing  $I_D/V_{th}$  Dispersion Metal system integrity

- Module level testing Assembly with prototype ASICs ↘ Electrical verification of periphery Assembly with new (final) ASICs ↘ Test of final ASICs/system in the beam

- ightarrow Assembly with prototype ASICs, kapton interconnection

- ightarrow Assembly with prototype ASICs, H7

- ightarrow L1 ladder for test beam and BEAST

- ightarrow L2 ladder for test beam and BEAST

## Schedule (as by July 2015)

| - PXD9 pilot run and beyond                              |             |

|----------------------------------------------------------|-------------|

| Sensors by                                               | July 2015   |

| All ASICs (prototypes) are pre-tested and available      |             |

| Assembly (FC+SMD)                                        | August 2015 |

| Tests to understand periphery performance:               | Sept - Nov. |

| Start phase II and III of sensor production (metal sys.) | Dec. 2015   |

|                                                          |             |

## Schedule (as by July 2015)

| - PXD9 pil                                               | ot run and  | beyond                               |                                  |               |  |

|----------------------------------------------------------|-------------|--------------------------------------|----------------------------------|---------------|--|

|                                                          | July 2015   |                                      |                                  |               |  |

| All ASICs (prototypes) are pre-tested and available      |             |                                      |                                  |               |  |

|                                                          | August 2015 |                                      |                                  |               |  |

| Tests to understand periphery performance:               |             |                                      |                                  | Sept - Nov.   |  |

| Start phase II and III of sensor production (metal sys.) |             |                                      | Dec. 2015                        |               |  |

| - ASIC submissions (including bumping)                   |             |                                      |                                  |               |  |

|                                                          | DHPT        | tape out end of August 2015          | $\rightarrow$ December 2015 f    | irst 100 dies |  |

|                                                          | DCD         | tape out end of August 2015          | $\rightarrow$ January 2016 first | t 100 dies    |  |

|                                                          | SWB         | tape out end of August 2015          | $\rightarrow$ January 2016 first | t 40+ dies    |  |

|                                                          | After tes   | st and verification of specs re-orde | er new wafers (within 6          | 5 months)     |  |

|                                                          |             |                                      |                                  |               |  |

| - ASIC testing                                           |             |                                      | Jan/Feb 2016                     |               |  |

|                                                          |             |                                      |                                  |               |  |

| <ul> <li>Assembly of test beam/Beast modules</li> </ul>  |             |                                      | March 2016                       |               |  |

|                                                          |             |                                      |                                  |               |  |

| - VXD combined test beam at DESY                         |             |                                      |                                  | April 2016    |  |

|                                                          | Summer 2010 |                                      |                                  |               |  |

| - Start PXD module production                            |             |                                      |                                  | Summer 2016   |  |

cmarinas@uni-bonn.de

• Serializer: timing bug

Mistake during extraction and simulation with all process corners (slow NMOS) Workaround for DHPT1.0: VDD = 1.6V for GCK=80 MHz Fixed for the DHPT1.1, with all corners simulated

- CML driver enhancement: reduce parasitic resistance Works fine but still output amplitude doubled by increasing pre-emphasis Signal integrity OK (kapton+ 20 m cable) No TID induced degradation up to 100 Mrad

- Delay elements issue: duty cycle distortion

Overlooked during DHPT1.0 sign off

Fixed by custom delay elements made by identical inverters in the chain

- Data receiver robustness: duty cycle distortion with non-symmetric input edges Corrected. See next slides.

• Radiation damage

SEU: Proton irradiation done. Calculations cross checked. TID: Data, offset and JTAG working

- Memory dump issue Only affects few per mil pedestal data frames Well localized fixed pattern

- Data processing So far, no issues seen (high occupancy tests, ...)

- $\rightarrow$  Further tests needed (esp. Gated Mode)

All the bugs understood, identified, reproducible. Re-design on schematic and layout levels done. Simulations of extracted layout (with corners) performed.

cmarinas@uni-bonn.de

- DHP: Ready for submission with minor changes

- The documentation of the problems and corrective actions was thorough and sufficient to assess readiness for submission. Further verification to be completed prior to tape-out

- DCD: Submission on hold until further tests

- Switcher: Submission on hold until further tests

General recommendations:

- 1. DHPT should be ready for late August submission

- 2. For the DCD, comparison with simulation of the test results and risk assessment

- 3. A deadline of 2-3 weeks to complete and distribute this DCD test summary was set

- 4. Submission of the Switcher possible after small layout changes

Belle II PXD Report: DCD and Switchers, August 2015

**DEPFET** Collaboration

- Top level specifications

- Chip history

- Summary of latest results

- Next version: DCDB4.1 and SwitcherB1.8-v2.1

- Submission plans

cmarinas@uni-bonn.de

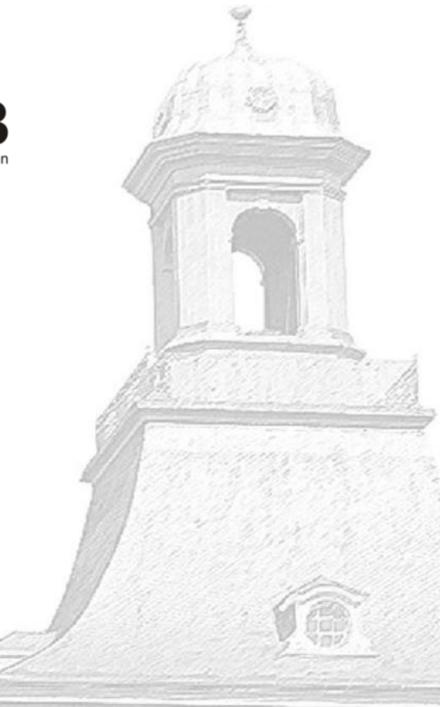

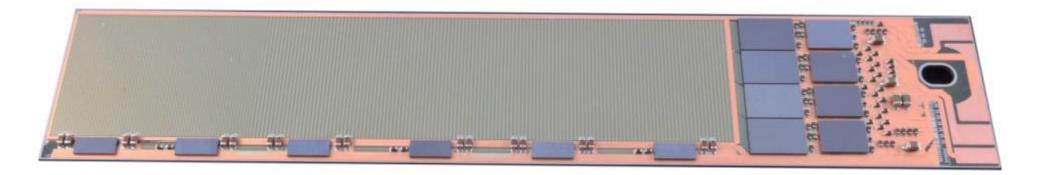

### **Test Systems**

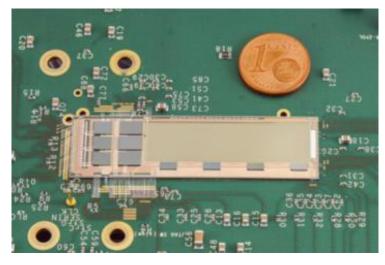

Hybrid4

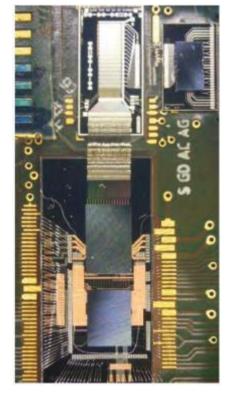

#### Hybrid6

#### Hybrid5

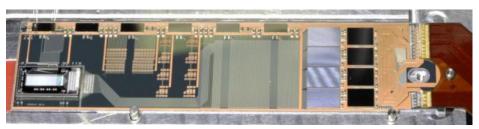

#### EMCM

## Hybrid 4.1

- 3 boards with DCDBPipeline assembled

- 1 board with PXD6 matrix

- VDDD=1.9 V to avoid bit errors

- The 256 channels were scanned at nominal speed 305 MHz

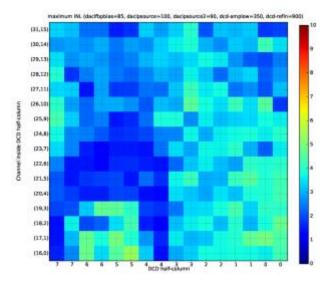

- Missing codes popping up depending on bias and DACs conditions but not position dependent

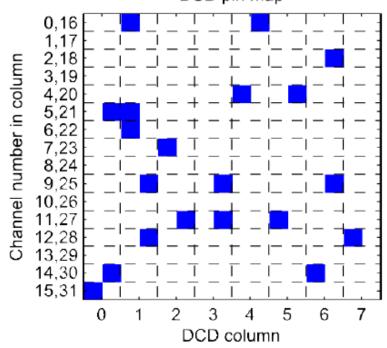

DCD pin map

### Hybrid 5.0

- 5 boards with DCDBPipeline assembled

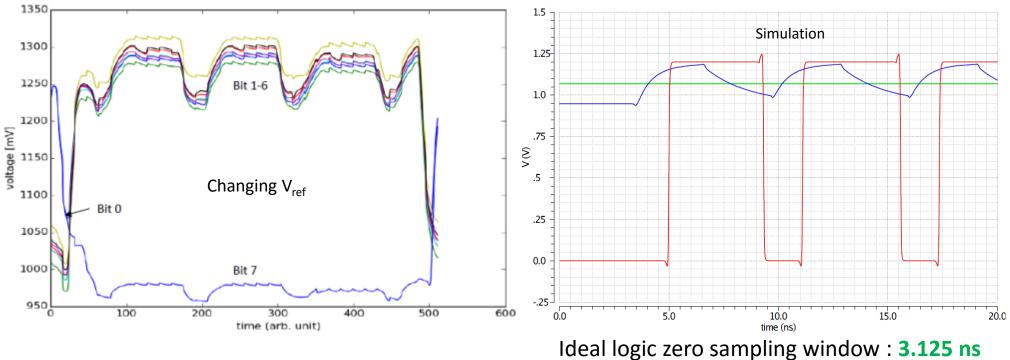

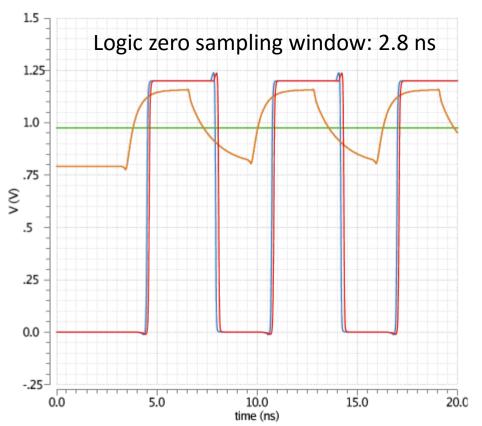

- Main investigations on DCD-DHP data transmission

- 64 data links tested using DCD test pattern

- Main issue revealed: Critically small sampling window!

Measured logic zero sampling window = 1 ns

### **EMCM**

- 6 EMCMs with DCDBPipeline and DHPT assembled

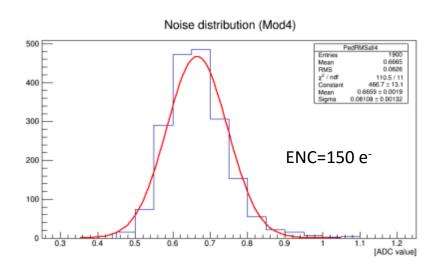

- Investigation on DCD ADC performance

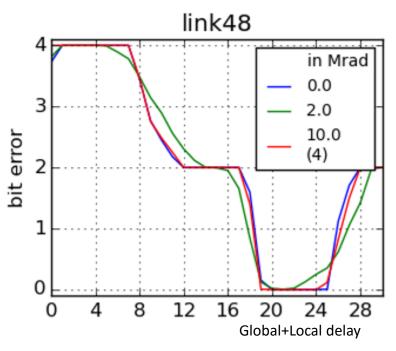

- DCD-DHP data transmission

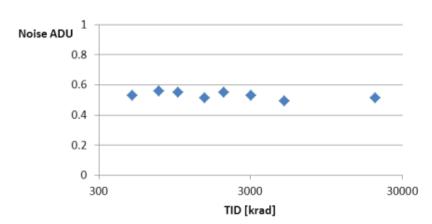

- X-ray irradiation

At 2 Mrad the delay tolerance shrinks, although we always found a region with no transmission errors

INL vs DCD position

- Digital transmission DCD-DHP: Reduce parasitic capacitance of DHP input pads Remove hysteresis on the receiver side Increase the DCD output strength

- Missing codes: Minimized by optimized DAC and bias settings Not relevant for the experiment

- Internal gain and pedestal correction: Adapt based on recent PXD9 static measurements

- Change sampling polarity according to standards: Sampling data at JTAG TCK raising edge Release data at falling edge

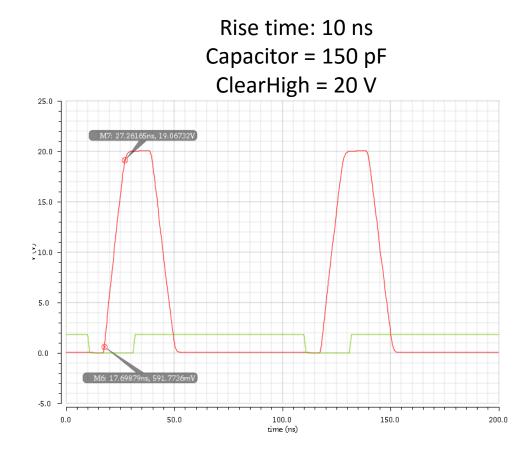

- Faster rise time: Larger switching transistors Increase decoupling capacitors

- Termination resistors always on

- Bump pads: Resize of pads on last metal layer

Based on the previous tests and simulations, the deficiencies are understood and minimal risk changes are proposed

### **□** Green light for submissions

- **DHP**: Submitted cw35. MPW. Turnaround time 56 days

- **Switcher**: Submitted cw35. MPW.

- **DCD**: To be submitted cw39. Engineering run with bumping. Cost shared KIT+DESY+HEI

### Schedule

#### - PXD9 pilot run and beyond

| Sensors by                                               | July 2015   |

|----------------------------------------------------------|-------------|

| All ASICs (prototypes) are pre-tested and available      |             |

| Assembly (FC+SMD)                                        | August 2015 |

| Tests for periphery performance with current ASICS:      | Sept - Nov. |

| Start phase II and III of sensor production (metal sys.) | Dec. 2015   |

#### - ASIC submissions (including bumping)

- DHPTtape out end of August 2015 $\rightarrow$  December 2015 first 100 diesDCDtape out end of September 2015 $\rightarrow$  January 2016 first 40+ diesSWBtape out end of August 2015 $\rightarrow$  January 2016 first 40+ diesAfter test and verification of specs re-order new wafers (within 6 months)

- ASIC testing

- Assembly of test beam/BEAST modules

- VXD combined test beam at DESY

Jan/Feb 2016

March 2016

April 2016 (tbd)

#### cmarinas@uni-bonn.de

# Thank you