# PXD9 Pilot Module Status Verification of the Metal Routing

PXD SeeVogh – November 10, 2015

Felix Müller, Christian Koffmane for the Testing Crew

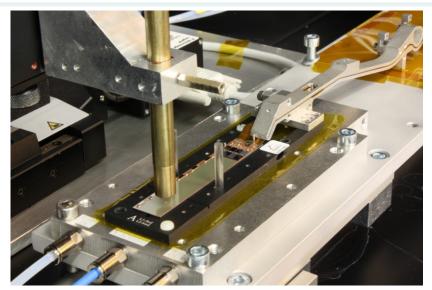

## PXD9 Pilot Module – Verification of the Metal Routing

Module operated @ 250MHz (128ns per row)

- power-up ASICs sanity check voltages + currents

- configure ASICs via JTAG

- boundary Scan: PASS (no faults in the digital I/Os)

- DHPT serial link parameters of the pre-emphasis

- DCD <-> DHPT communication timing adjustment

- sampling point scan

- optimize DCD analogue performance (IPSource/2, IFBPBias, RefIn)

- 2 outer backward modules are assembled with kapton

- 1 outer forward module is prepared for the assembly on Hybrid7

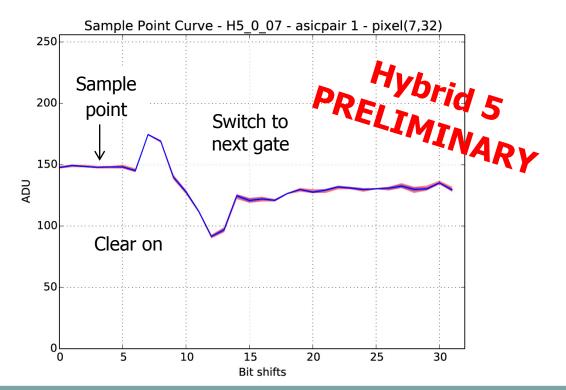

## Sampling Point Scan

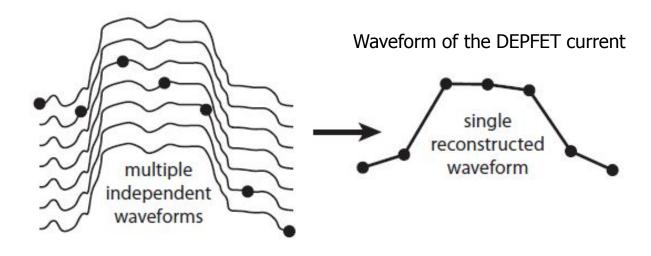

#### Time resolved measurements with DHPT and DCD

Applying a technique called sequential sampling a continuous time waveform of the DEPFET current can be measured

- From a periodic and stable input a single sample is taken

- The sample point is shifted by deltaT

- The single samples are assembled to form a combined waveform

- Averaging can be used to suppress electronic noise

## Sampling Point Scan

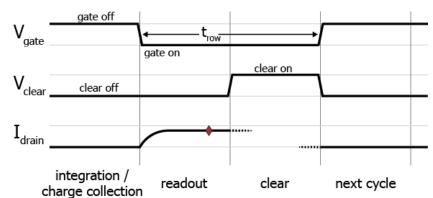

- Sampling the DEPFET current at the correct point of time is extremely important

- The scan is currently implemented with DHPT as controller for the timing

- Step size coarse = 4ns

- Step size fine = ~250ps

- Sampling point curve using Hybrid5 DHPT/DCDB4 + small PXD9 matrix @ 250MHz

- 1 bit shift = 4ns

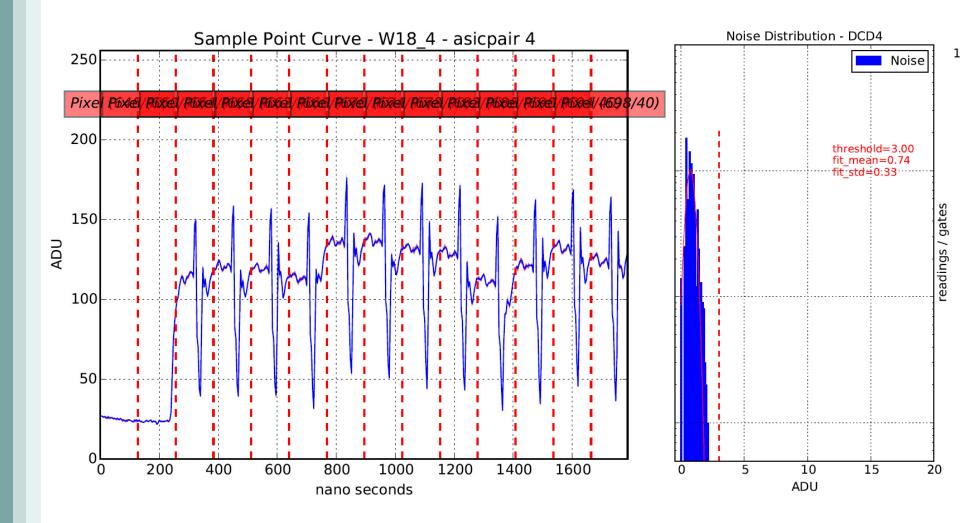

## EMCM W18-4: Sample Point Scan and Noise (small PXD9)

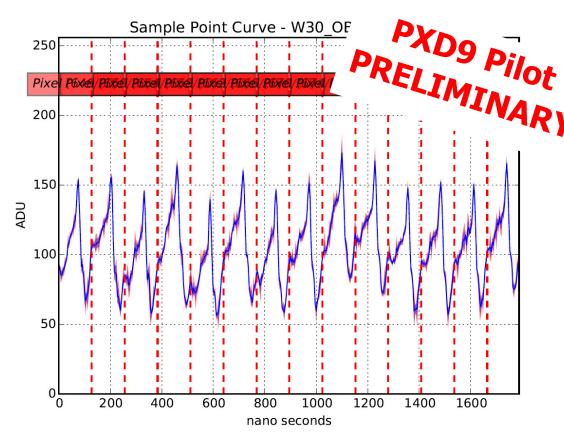

## Sampling Point Scan

- Same sequence as for EMCM applied

- No plateau for stable current sampling @ 128ns per row

- Timing of a subset of the rows changed to 384ns (32 out of 192)

- Work in progress: scan of the switcher Strobe-Clear signal with respect to Switcher-Clock and Strobe-Gate

- We need more time to understand the sampling point scans

- Measurements @ full speed are delayed

- Still we would like to keep the date for a expert F2F meeting @ HLL in cw. 48

128ns per row

# PXD9 Pilot Verification Plan

|                   | 2630. Oct               | 26. Nov | 9.13. Nov                              | 1620. Nov                                       | 2327. Nov                                                        | 30. Nov - 4.Dec. | Dec. 7th                       |

|-------------------|-------------------------|---------|----------------------------------------|-------------------------------------------------|------------------------------------------------------------------|------------------|--------------------------------|

| CW                | 44                      | 45      | 46                                     | 47                                              | 48                                                               | 49               | 50                             |

| HLL<br>(pxdtest2) | sampling point scan     |         |                                        | increase to nominal freq.                       | gated mode                                                       |                  |                                |

|                   | pedestal/noise all DCDs |         |                                        | DHPT serial link<br>-<br>IBERT/oscillosco<br>pe | •                                                                |                  |                                |

|                   |                         |         |                                        | DCD <-> DHPT (delay)                            | Cd109 spectrum                                                   |                  |                                |

|                   |                         |         |                                        | sampling point scan                             | Laser spot                                                       |                  | Go for PXD9                    |

|                   |                         |         |                                        | pedestal/noise<br>all DCD                       |                                                                  |                  | metallization or agreement     |

|                   |                         |         |                                        | zero suppressed<br>data                         | F2F Meeting @<br>HLL                                             |                  | on the<br>necessary<br>changes |

|                   |                         |         |                                        |                                                 |                                                                  |                  |                                |

|                   |                         |         |                                        |                                                 |                                                                  |                  |                                |

|                   |                         |         |                                        |                                                 |                                                                  |                  |                                |

| HLL<br>(pxdtest4) |                         |         | Preparation Gated<br>Mode Test<br>EMCM |                                                 | Hybrid 7 Testing<br>to verify OF/IB<br>balcony and EOS<br>layout |                  |                                |

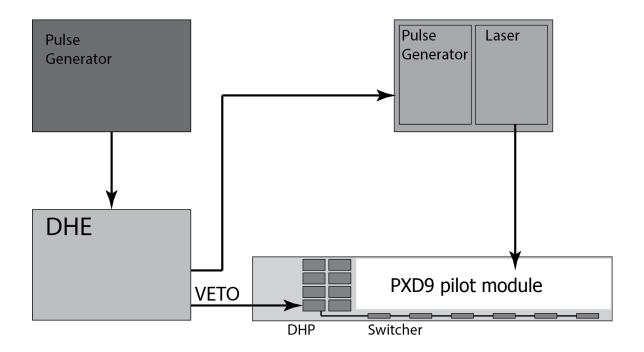

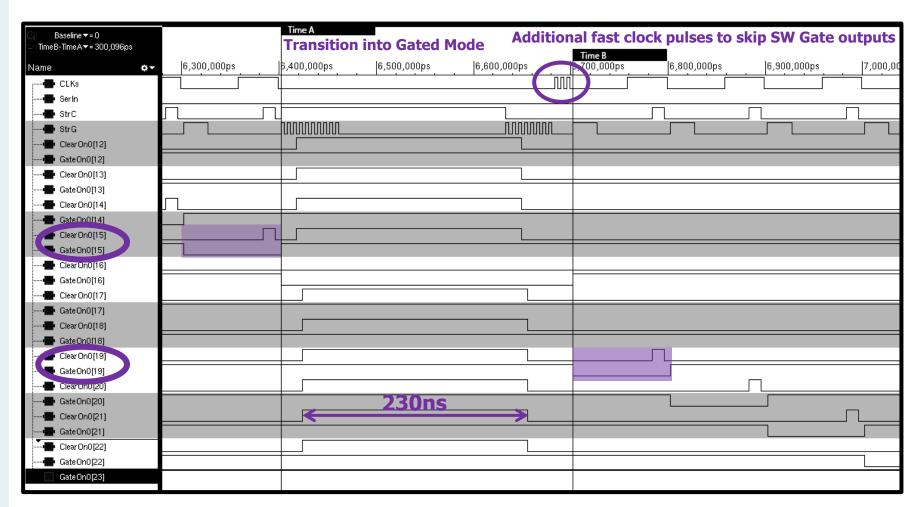

## Gated Mode Verification

- DHE receives VETO trigger from external pulse generator and forwards it to the DHPT

- the DHPT jumps from the current sequencer memory address to a dedicated address where the Gated Mode sequence is defined

- via the control lines (StrG, StrC, CLK) the Switcher is programmed into Gated Mode the timing can be chosen in steps of ~3.3ns

- separated in 4 groups of Switcher output channels all the Clear lines are switched to the ClearOn potential, the Gate line keep the GateOff potential

- the DHE generates a trigger for a laser to verify that the gating works

#### Gated Mode Verification

- DHE adapter board for external VETO trigger is available and tested

- dedicated firmware for the Gated Mode test in the lab also available and tested @ TUM

- system test with EMCM and small PXD9 matrix planned for next week @ HLL

Unfortunately I missed to take a photo ...

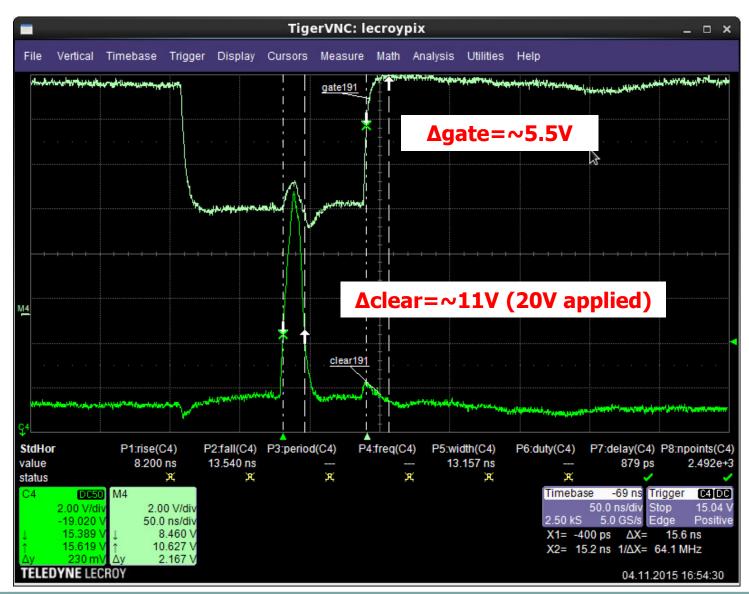

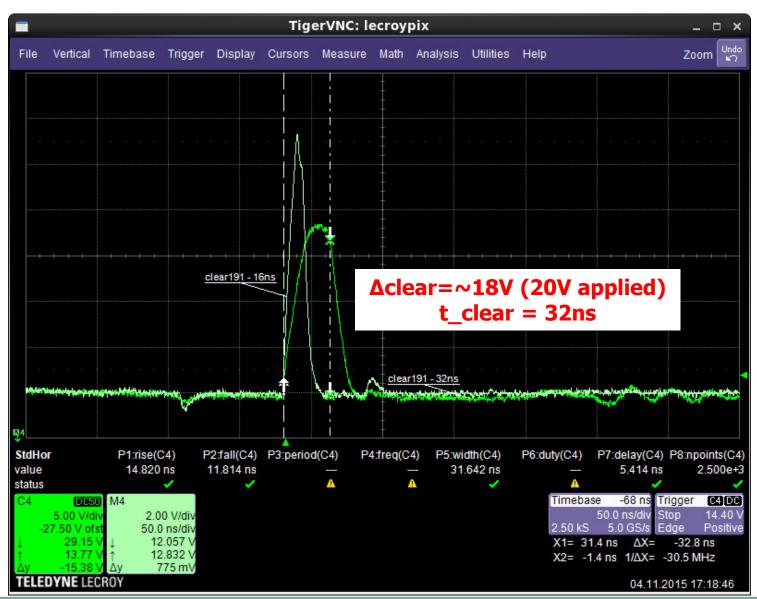

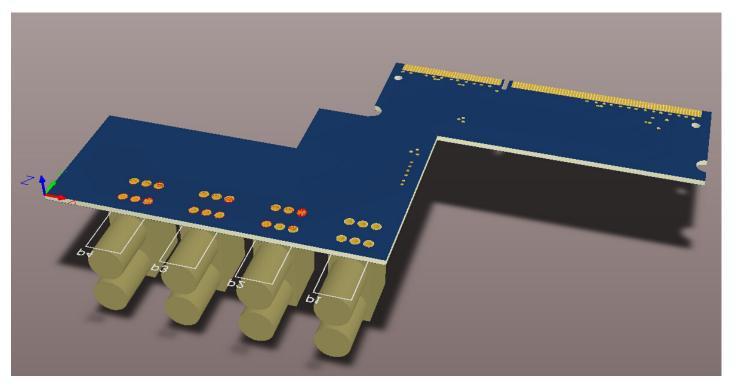

## Gated Mode Verification

- Verilog simulation to make sure that the Switcher sequence is correct

- Switcher behavior was verified on hybrid4 test board

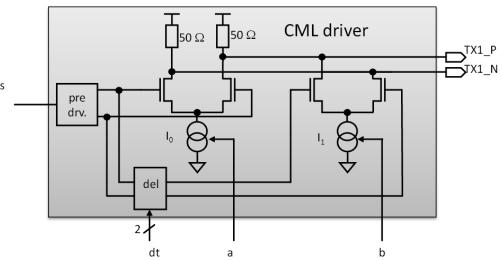

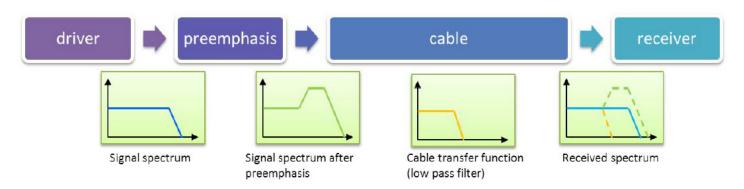

## DHPT serial link – parameters of the pre-emphasis

with this scan the parameters for the pre-emphasis are determined

|        | Register Name     | Register<br>Length |  |

|--------|-------------------|--------------------|--|

| а      | IDAC CML TX BIAS  | 256                |  |

| b      | IDAC CML TX BIASD | 256                |  |

| c (dt) | pll cml dly sel   | 4                  |  |

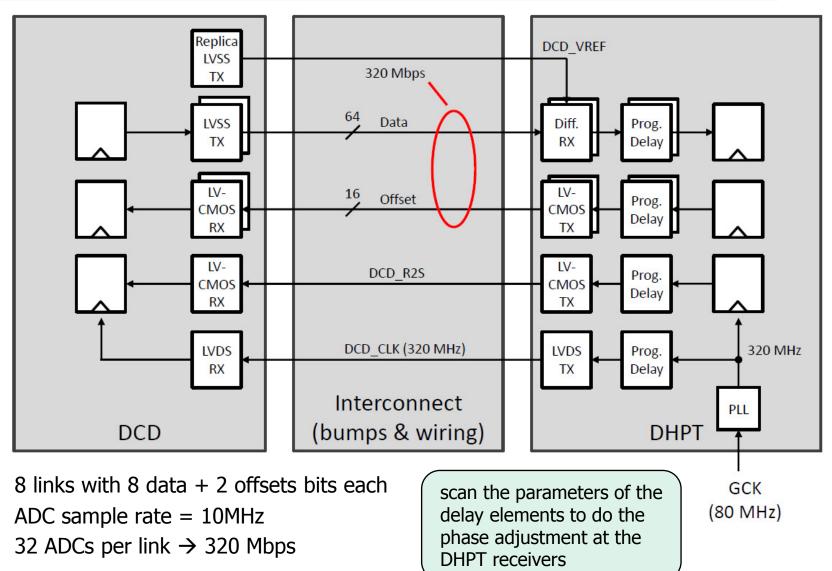

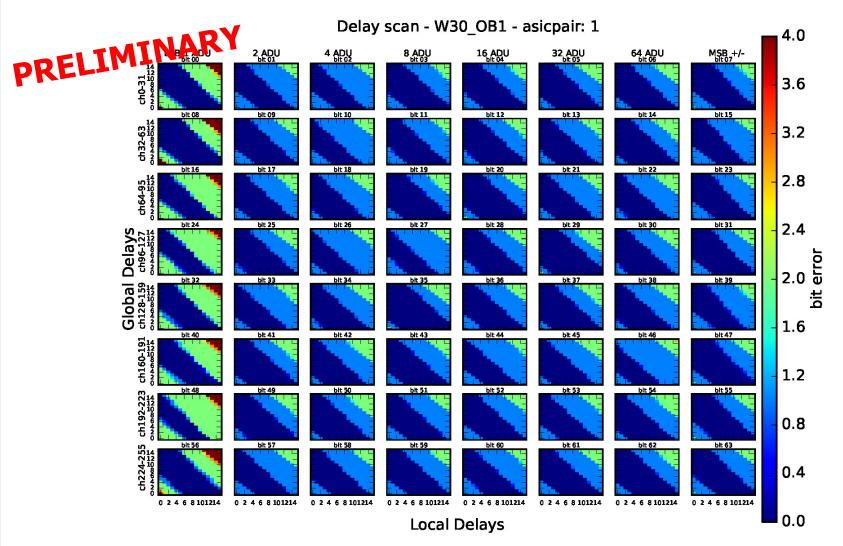

## DCD <-> DHPT communication – timing adjustment

## DCD <-> DHPT communication – timing adjustment

PXD9 – delay element scan @ 250Mpbs

Measure DEPFET response (Source, Laser spot, homogeneously illuminated)

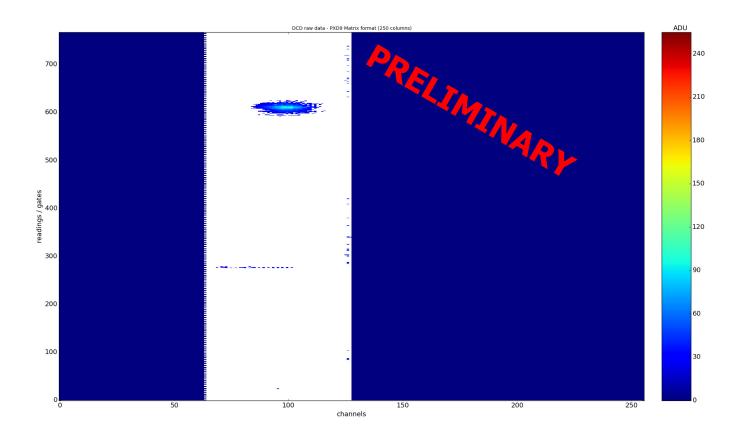

#### **PXD9 W30-OB1**

- Laser Spot in the area between SW5 and SW6

- Zero Suppressed read-out of DHPT2 only

## PXD9 Pilot Verification Plan @ BPAC

To verify the routing of the 3 metal layers of the PXD9 module the following measurements have to be done:

|                   | 2630. Oct                  | 26. Nov                       | 9.13. Nov                                                        | 1620. Nov  | 2327. Nov                          | 30. Nov - 4.Dec. | Dec. 7th                                                        |

|-------------------|----------------------------|-------------------------------|------------------------------------------------------------------|------------|------------------------------------|------------------|-----------------------------------------------------------------|

| CW                | 44                         | 45                            | 46                                                               | 47         | 48                                 | 49               | 50                                                              |

| HLL<br>(pxdtest2) | sampling point scan        | increase to nominal freq.     | zero suppressed<br>data                                          | gated mode | DEPFET Lab<br>F2F Meeting @<br>HLL |                  | Go for PXD9 metallization or agreement on the necessary changes |

|                   | pedestal/noise<br>all DCDs | DHPT serial link<br>IBERT     | pedestal<br>compression                                          |            |                                    |                  |                                                                 |

|                   |                            | DHPT serial link oscilloscope | Cd109 spectrum                                                   |            |                                    |                  |                                                                 |

|                   |                            | DCD <-> DHPT (delay)          | Laser spot                                                       |            |                                    |                  |                                                                 |

|                   |                            | sampling point scan           |                                                                  |            |                                    |                  |                                                                 |

|                   |                            | pedestal/noise<br>all DCDs    |                                                                  |            |                                    |                  |                                                                 |

|                   |                            |                               |                                                                  |            |                                    |                  |                                                                 |

|                   |                            |                               |                                                                  |            |                                    |                  |                                                                 |

| HLL<br>(pxdtest4) |                            |                               | Hybrid 7 Testing<br>to verify OF/IB<br>balcony and EOS<br>layout |            |                                    |                  |                                                                 |