## **Changes from DHPT 1.1 to DHPT 1.2**

DEPFET Workshop, Kloster Seeon Mai 11-14, 2016

### **Bugs fixed in DHPT 1.2**

#### **CML Driver**

- CML driver power routing

- Ground rail (VSS) had a too high wiring resistance (~30 Ohm), parasitic extraction did not spot this because of substrate model

- − Rerouting of power nets  $\rightarrow$  R<sub>VSS</sub> < 0.2 Ohm

- CML driver bias routing

- Removed ESD resistor in bias connection and reduced parasitic resistance → increase of bias current, less sensitivity to voltage supply

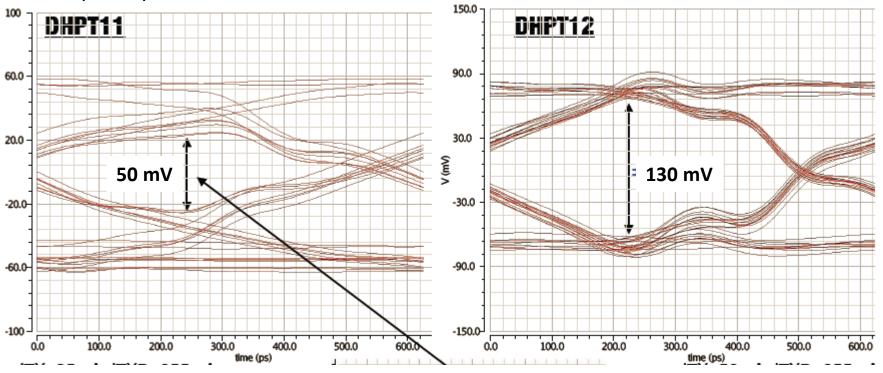

### **CML Driver Performance Improvements**

#### Simulation setup

- CML driver: fully extracted RC including bias and power routing, typical corner

- Cable model: Extracted S-parameters of kapton + 2m TWP + 12m TWP including the patch panels

### **Bugs fixed in DHPT 1.2**

#### Digital core

- Mem dump

- Data had some low probability to show corrupted values for the first few pixels when output was set to 800 MHz and clock compensation was on → fixed in HDL code

- Internal system clock phase

- The core clock started with an arbitrary phase after power-on → added controlled reset (delayed GCK) to the internal clock divider

- Gated mode sequence put out first word twice

- Fixed HDL code

### **Enhancements for DHPT 1.2**

#### **Digital core**

- JTAG USERID changed: allows recognition of DHPT version

- Gated mode: DATA\_IN for the switcher can be selected to be controlled from either the normal mode sequence of the gated mode sequence (was normal mode only)

- Added the DHPT ID in the memory dump frame header

- Memory dump start address configurable

- Bias register for LVDS receivers has fixed minimum value

### **Summary & Outlook**

- DHPT 1.2 changes

- Power routing if the CML driver fixed

- Re-synthesized the digital core (bug fixes and enhancements)

- DHPT 1.2 production

- Tape-out: April 27 (official deadline, production at TSMC starts ~ 2 weeks later)

- Expected delivery (100 bumped chips): beginning of July

- Functional test

- Functional test on probe station and hybrid 5

- If functional tests are passed, immediately start to deliver tested chips for module production

- Mass production/testing

- Decision for DHPT 1.2 as the production chip

- Then: Order of 9 additional wafers (1000 chips in total)

- Two new needle cards for probe station testing are available

- Estimated testing throughput: ~50 chips per week

# **BACKUP**

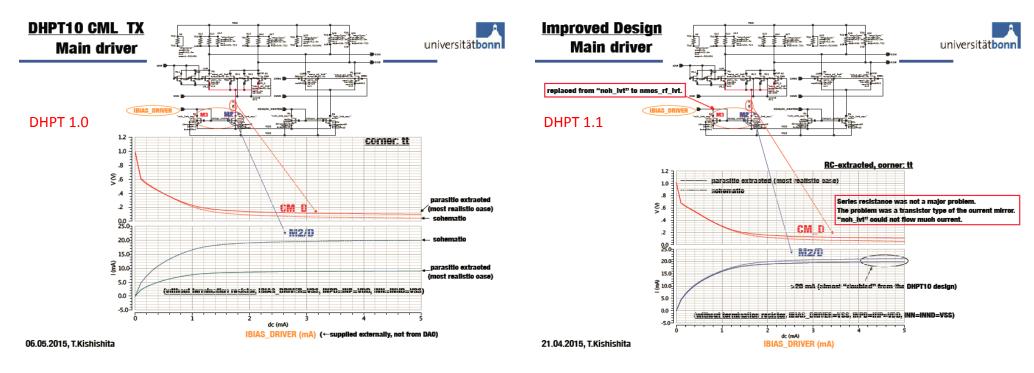

#### **DHPT CML Driver**

Changes from DHPT1.0 to DHPT1.1

- Layout extracted with all parasitic elements

- Current in the main stage expected to be ~20mA after improvement of the transistor layout

- However measurements on DHPT 1.1 indicated ~10mA only

### **DHPT CML Driver**

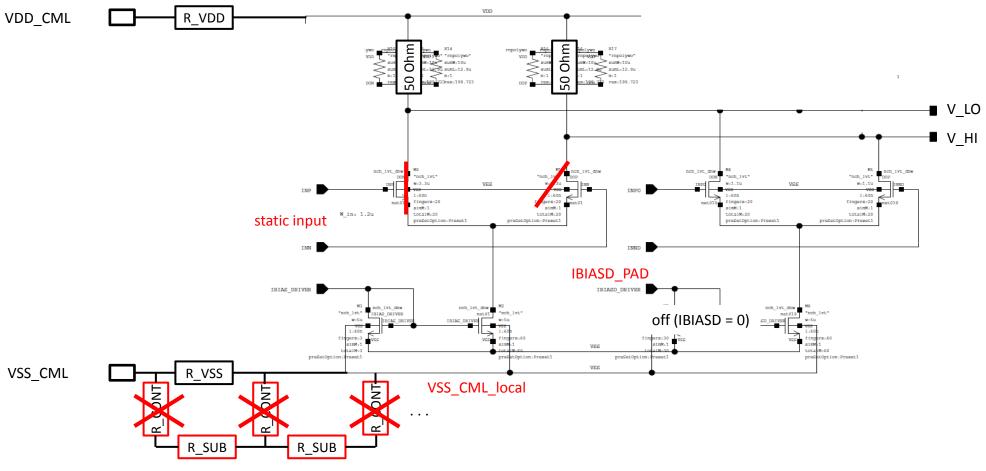

Possible explanation: layout extraction underestimated the parasitic resistances R\_VDD and R\_VSS on the power lines

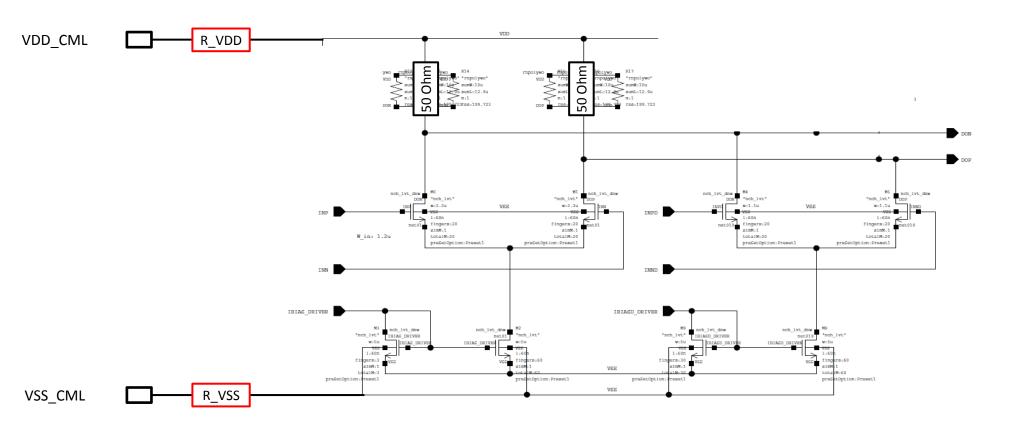

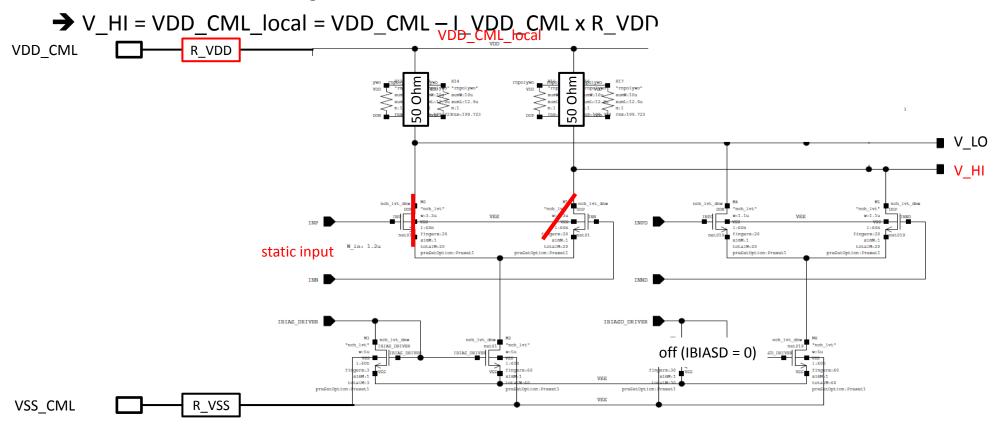

### Measurement of the Parasitic Resistance R\_VDD

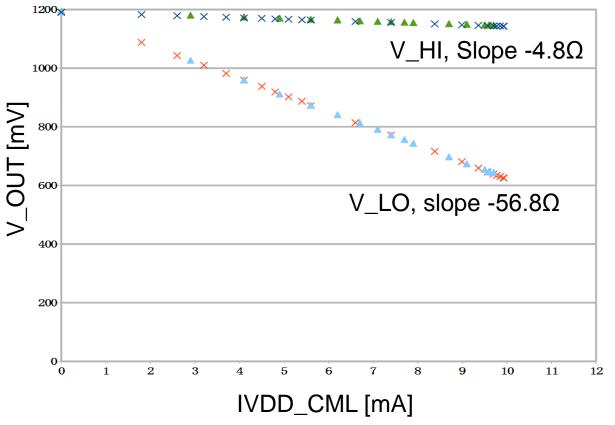

- Measure V\_HI as a function of I\_VDD\_CML by changing IBIAS

- no termination at driver output

- no data line switching

### Measurement of the Parasitic Resistance R\_VDD

- Measurements indicate a parasitic resistance of about 5 Ohm in the VDD\_CML line

- This is in agreement with the extraction of the parasitic elements of the layout, however this does not explain the loss of drive strength.

DHPT 1.0: ▲ ▲ DHPT 1.1: x x

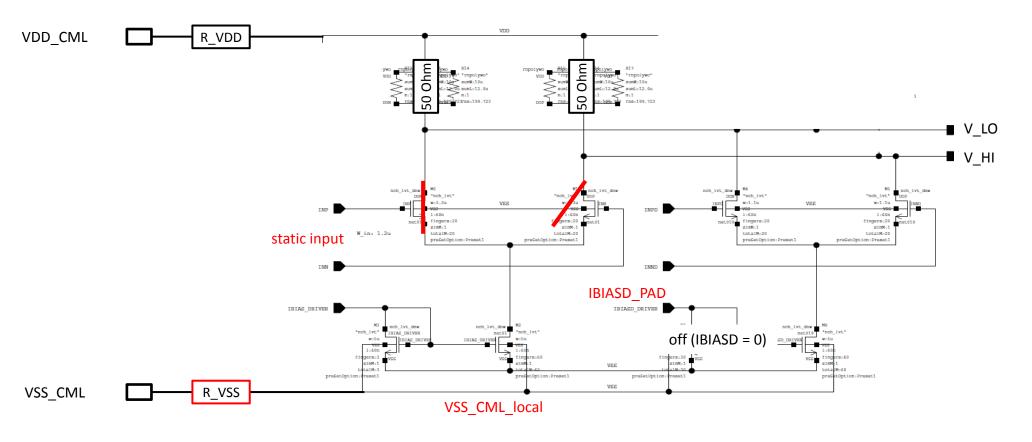

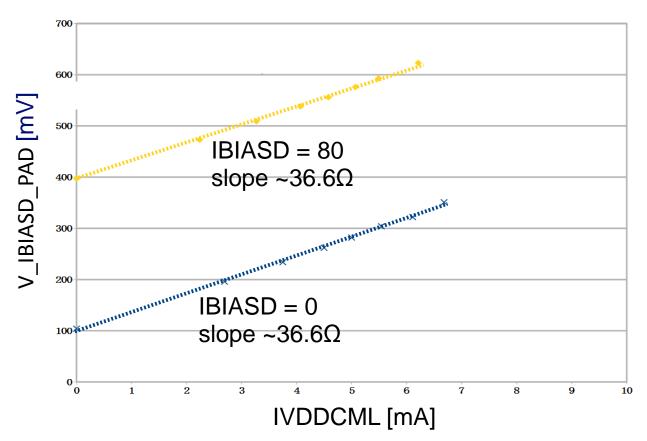

### Measurement of the Parasitic Resistance R\_VSS

- Measure V\_IBIASD\_PAD as a function of I\_VDD\_CML by changing IBIAS, no termination at driver output

- → V\_IBIASD\_PAD = VSS\_CML\_local + const = VSS\_CML + I\_VDD\_CML x R\_VSS

### Measurement of the Parasitic Resistance R\_VSS

- Measurements indicate a parasitic resistance of about 36 Ohm in the VSS\_CML line

- This is **not in agreement** with the simulation of the extracted layout which also shows ~5

Ohm parasitic resistance

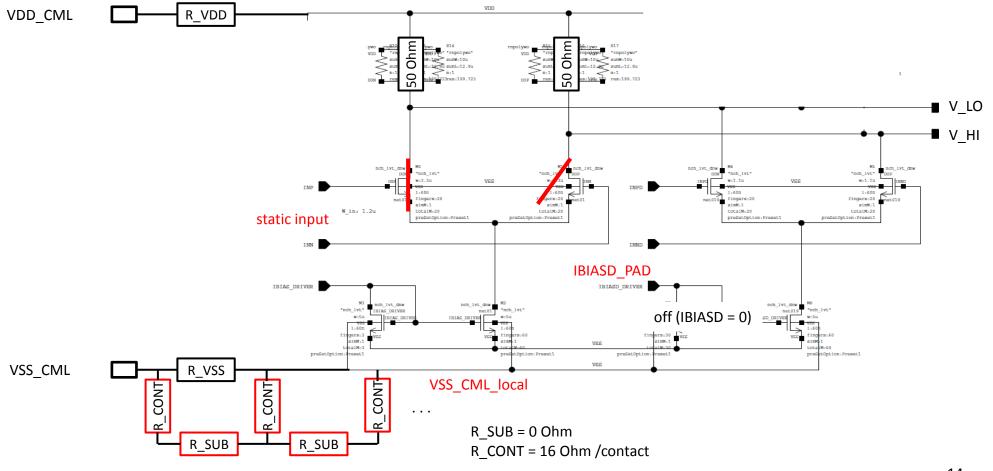

### Issue with the RC-extraction of the layout

- The extraction tool models the silicon substrate as a perfect conductor (R\_SUB = 0 Ohm) and VSS\_CML ins connected to the bulk with a lot of substrate contacts

- → Underestimation of the resistance in VSS\_CML

### **Proof of the Explanation**

- We removed the substrate contacts in the layout and extracted the parasitics again

- → R\_VSS\_CML ~ 30 Ohm

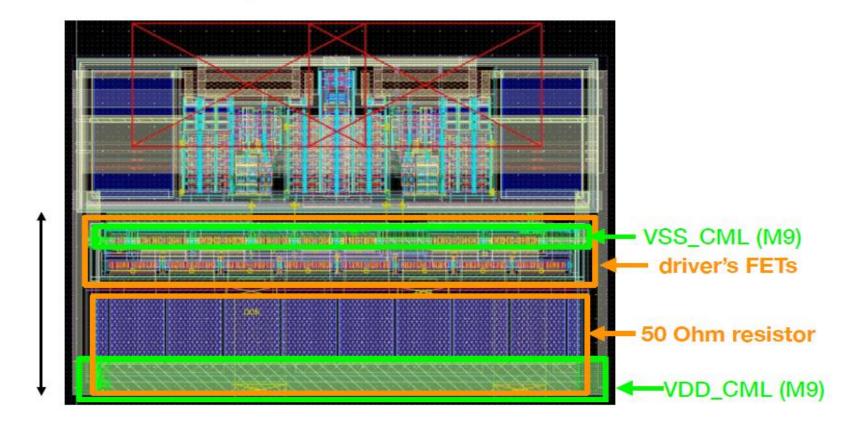

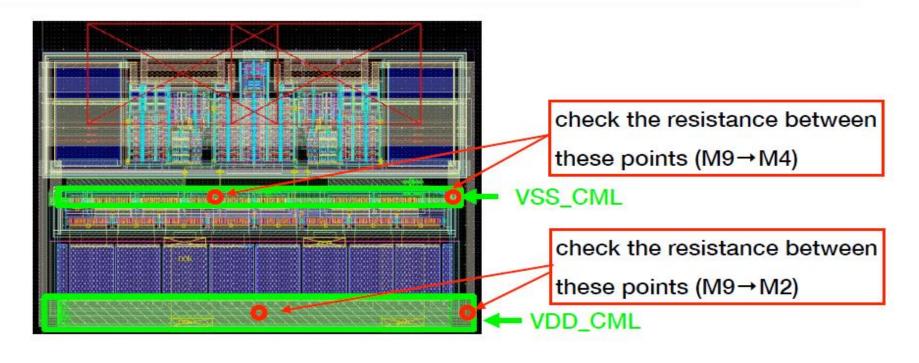

## CML\_TX Layout toward DHPT12

- vertical connection (M2→M9 for VDD\_CML and M4→M9 for VSS\_CML

- separate VSS and PSUB for Driver current mirror and switches

- avoid M1 connection between separate circuit blocks

most current flowing part

### **Serial-Resistance**

|         | Assura, typical        | Assura, worst          | Calibre, typical |

|---------|------------------------|------------------------|------------------|

| VDD_CML | $49.3 \text{ m}\Omega$ | $66.5 \text{ m}\Omega$ | 53.0 mΩ          |

| VSS_CML | 114.1 mΩ               | 151.4 mΩ               | 115.2 mΩ         |

ΔR<sub>serial</sub>: ~30% corner dependence, and ~10% between Assura and Calibre