# DCD4.1/DCD4.2 Review Analog Performance

Philipp Wieduwilt<sup>1</sup>, Harrison Schreeck<sup>1</sup>, Benjamin Schwenker<sup>1</sup> Botho Paschen<sup>2</sup>, Florian Luetticke<sup>2</sup>

> <sup>1</sup>Uni Göttingen <sup>2</sup>Uni Bonn

## DCD4.x

- JTAG sampling CLK edge compatible with industry standard

- option to increase DCD digital LVDS driver current from 1.3mA to 1.8mA (LVDS boost) → see talk by Harrison Schreeck

- option to increase DCD digital driver reference voltage by 30mV

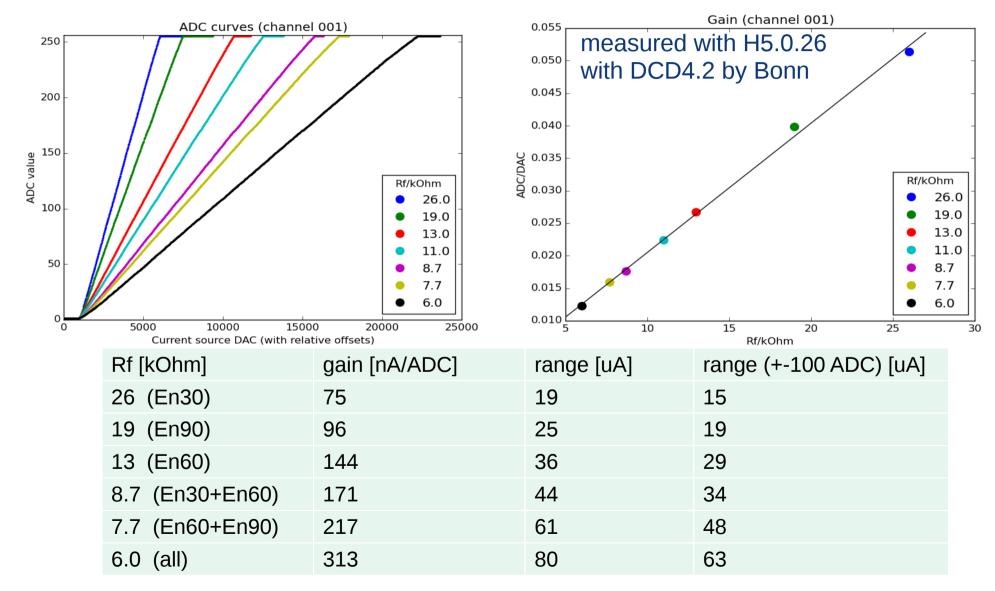

- changed **TIA gain settings**

- IPDAC current reduced by factor of 2 to improve offset correction granularity

- added **IPSourceMiddle** DAC to cope with upper/lower channels asymmetry

## DCD4.1

added two antenna diodes and dummy structures to improve transistor matching in the ADCs

## DCD4.2

- added diodes, dummy structures and increased transistor sizes to improve transistor matching

- more **complex digital test pattern** for improved delay optimization

- changed ID code

- test DCD4.1 and DCD4.2 functionality on Hybrid5 level

- confirm that stable operation is possible with both DCD designs

- check correct implementation of gains

- check that ADCs operation can be optimized within specifications

- INLpp < 8 ADU within +-100 ADC

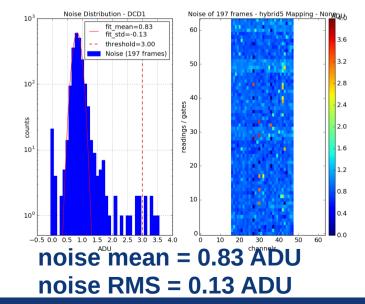

- noise < 1.0 ADU

- no long codes above 6 ADU

- no bit errors visible in ADC curves

- gains should be homogeneous among all DCD channels

- adjust with new IPSourceMiddle DAC

- DCD4.1

- H5.0.24: measured in Goe and Bonn

- equipped with switcher and matrix

- H5.0.13: measured in Goe and Bonn

- H5.0.12: not measured yet, located in Bonn

- DCD4.2

- H5.0.15: measured in Goe

- strange gain behaviour, large current offsets

- H5.0.14: measured in Goe

- equipped with switcher and matrix

- H5.0.26: measured in Bonn

all measured at GCK = 76 MHz LVDS boost on LVDS ref shift on

## **DCD4.x Gain Implementation**

TIA gain adjustable by combination of feedback resistors of 26k (En30), 13k (En60) and 19k (En90)

## **ADC Optimization Criteria**

check ADC curve for noise, INLpp, long codes, code range and bit errors

- long codes originate from transistor mismatches in the ADC comparators

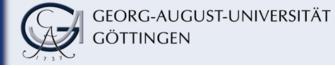

- still see very few long codes in DCD4.x, but all with DNL < 6, not harmful according to DCD4.x design manual

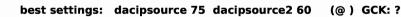

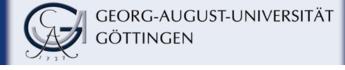

- narrow window for the optimal IPSource, IPSource2 values

- large enough to find stable setting

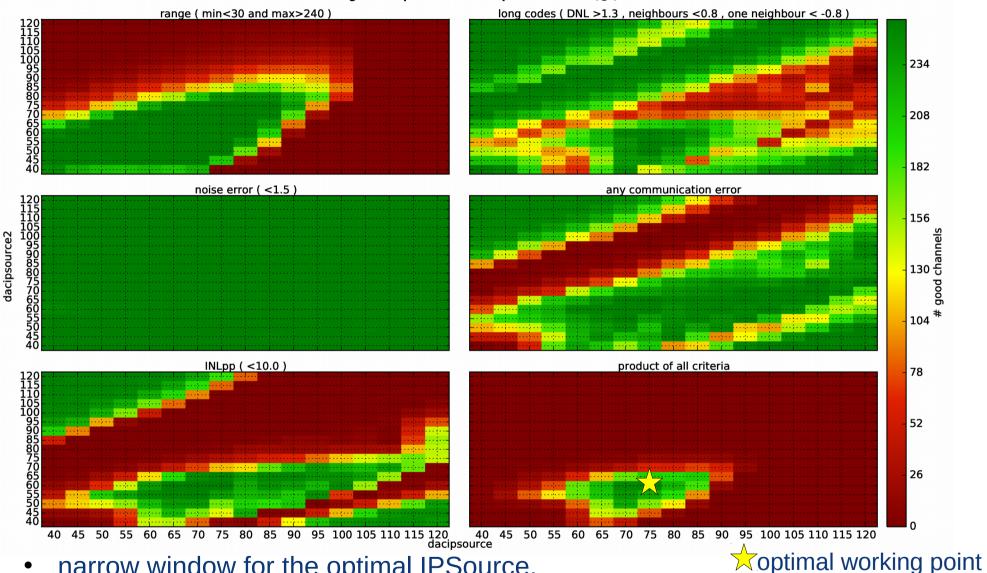

## H5.0.13 (DCD4.1) Optimization: **RefIn-AmpLow**

GEORG-AUGUST-UNIVERSITÄT GÖTTINGEN

dcd-refin

14/09/16

- RefIn very much constrained •

- scan with finer step size around 700-750 mV

- AmpLow with broad good region

234

208

182

156

130

104

78

52

26

good channels

#### GEORG-AUGUST-UNIVERSITÄT Göttingen

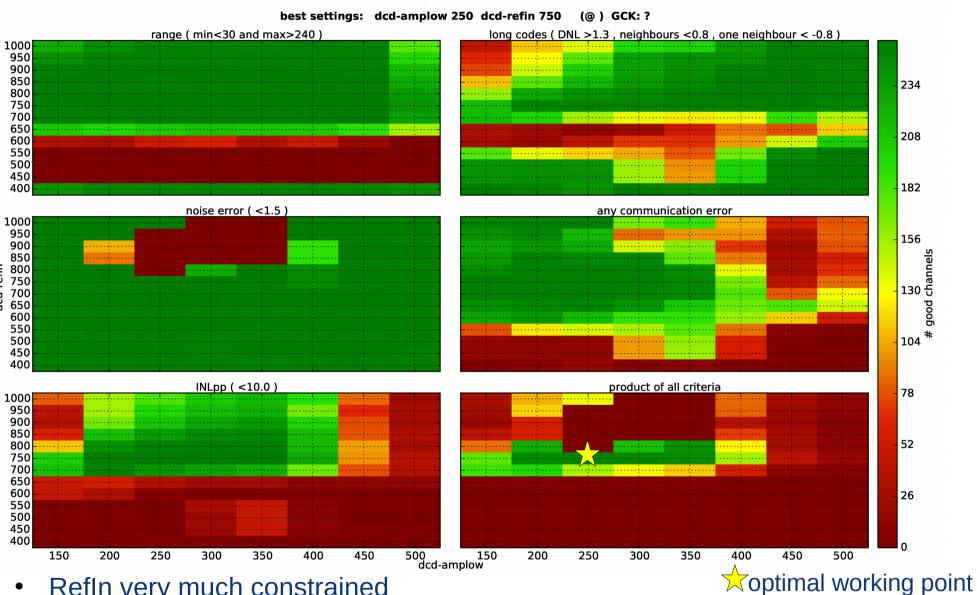

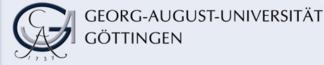

## H5.0.13 (DCD4.1) Optimization: IFBPBias

best settings: dacifbpbias 75 (@) GCK: ?

find an optimal IFBPBias value with a large number of good channels

- IPSourceMiddle improves top/bottom inhomogeneity

- need to add IPSourceMiddle to the standard optimization parameters

DCD pin-out map of the minimal code measured in the channels ADC curve

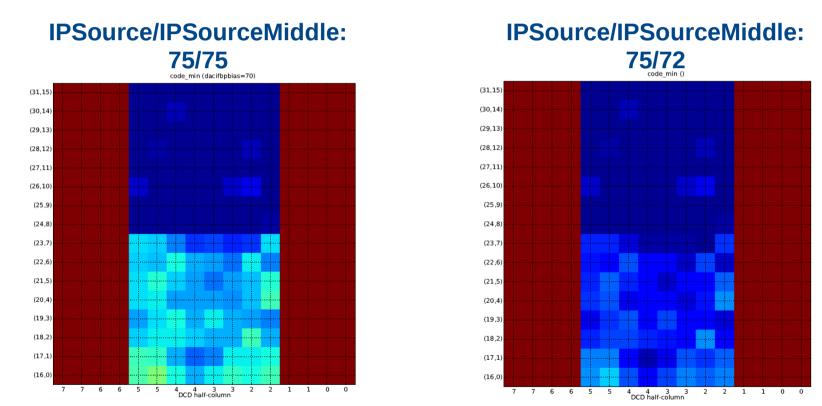

- found optimal working point for DCD4.1 on H5.0.13

- all channels are good, performance within specifications

- all channels have INLpp < 8 ADU

- all channels show noise < 0.55 ADU

- gain similar for all channels

## • optimal working points table

| Module              | IPSource | IPSource2 | IFBPBias | RefIn [mV] | AmpLow [mV] | gain/Clock         | comment                             |  |  |  |  |

|---------------------|----------|-----------|----------|------------|-------------|--------------------|-------------------------------------|--|--|--|--|

| H5.0.24<br>(DCD4.1) | 70       | 60        | 75       | 690        | 200         | En30,<br>76MHz     | DHE source                          |  |  |  |  |

| H5.0.13<br>(DCD4.1) | 70       | 60        | 75       | 690        | 200         | En30,<br>76MHz     | DHE source                          |  |  |  |  |

| H5.0.14<br>(DCD4.2) | 75       | 65        | 70       | 680        | 200         | En30,<br>76MHz     | DHE source,<br>same for gate source |  |  |  |  |

| H5.0.15<br>(DCD4.2) | 70       | 55        | 60       | 700        | 200         | En30,<br>76MHz     | strange gain<br>behaviour           |  |  |  |  |

| H5.0.26<br>(DCD4.2) | 70       | 60        | 70       | 650        | 200         | ?                  |                                     |  |  |  |  |

| DCDpp               |          |           |          |            |             |                    |                                     |  |  |  |  |

| H5.0.06<br>(DCDpp)  | 100      | 80        | 90       | 850        | 350         | HighGain,<br>62MHz | with matrix                         |  |  |  |  |

| H5.0.07<br>(DCDpp)  | 90       | 70        | 85       | 950        | 400         | HighGain,<br>62MHz | without matrix                      |  |  |  |  |

• all DCD4.1 and DCD4.2 have very similar optimal working points

**improved optimization procedure** correct setting of VNSubIn, fine RefIn stepping

### channel statistics table

| Module              | scanned | good | range err. | bit err. | comp. err. | INL err. | quality (good/all) |  |  |  |  |

|---------------------|---------|------|------------|----------|------------|----------|--------------------|--|--|--|--|

| H5.0.24<br>(DCD4.1) | 256     | 249  | 1          | 0        | 2          | 4        | 0.97               |  |  |  |  |

| H5.0.13<br>(DCD4.1) | 256     | 256  | 0          | 0        | 0          | 0        | 1.00               |  |  |  |  |

| H5.0.14<br>(DCD4.2) | 256     | 256  | 0          | 0        | 0          | 0        | 1.00               |  |  |  |  |

| H5.0.15<br>(DCD4.2) | 256     | 252  | 0          | 0        | 0          | 0        | 1.00               |  |  |  |  |

| H5.0.26<br>(DCD4.2) | 256     | 247  | 0          | 9        | 0          | 0        | 0.96               |  |  |  |  |

| DCDpp               |         |      |            |          |            |          |                    |  |  |  |  |

| H5.0.06<br>(DCDpp)  | 256     | 249  | 2          | 5        | 0          | ?        | 0.97               |  |  |  |  |

| H5.0.07<br>(DCDpp)  | 43      | 39   | 0          | 4        | 0          | ?        | 0.88               |  |  |  |  |

• all DCD4.1 and DCD4.2 perform well at optimal working point

**improved optimization procedure** correct setting of VNSubIn, fine RefIn stepping

# Source Measurements with DCD4.2, PXD9-6 Matrix and SWB18v2.1

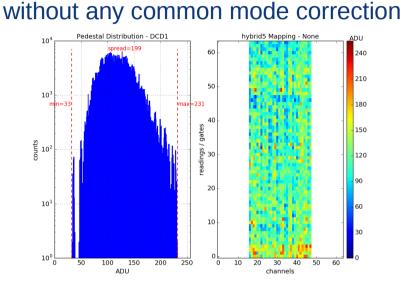

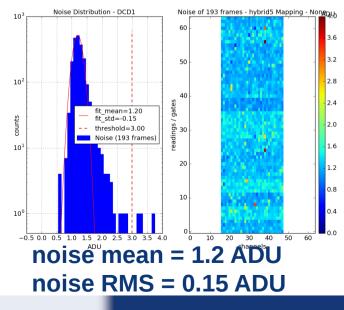

## **Analog Common Mode Correction**

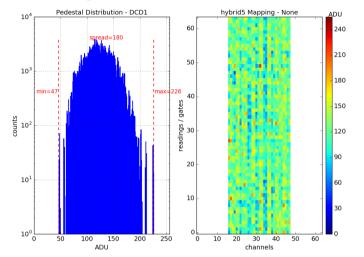

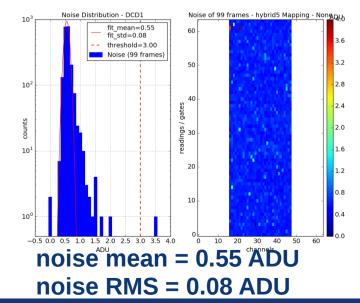

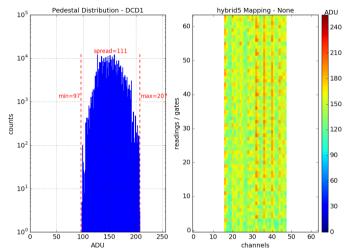

• pedestals and noise measured on H5.0.14 with DCD4.2

ACMC on

#### min-max pedestal = 199 ADU

#### with analog common mode correction

#### min-max pedestal = 180 ADU

#### 14/09/16

10<sup>th</sup> VXD Belle II Workshop, Santander

## **2bit DAC Offset Correction**

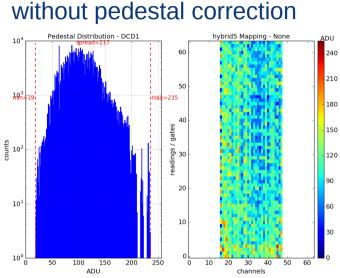

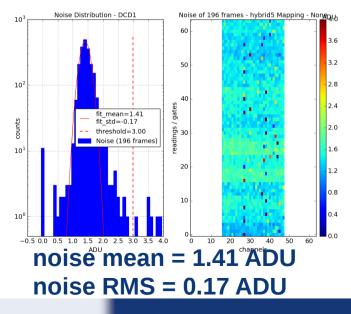

• pedestals and noise measured on H5.0.24 with DCD4.1

#### min-max pedestal = 217 ADU

### 2bit DAC corr.

### with 2bit DAC offset correction

### min-max pedestal = 111 ADU

#### 14/09/16

10<sup>th</sup> VXD Belle II Workshop, Santander

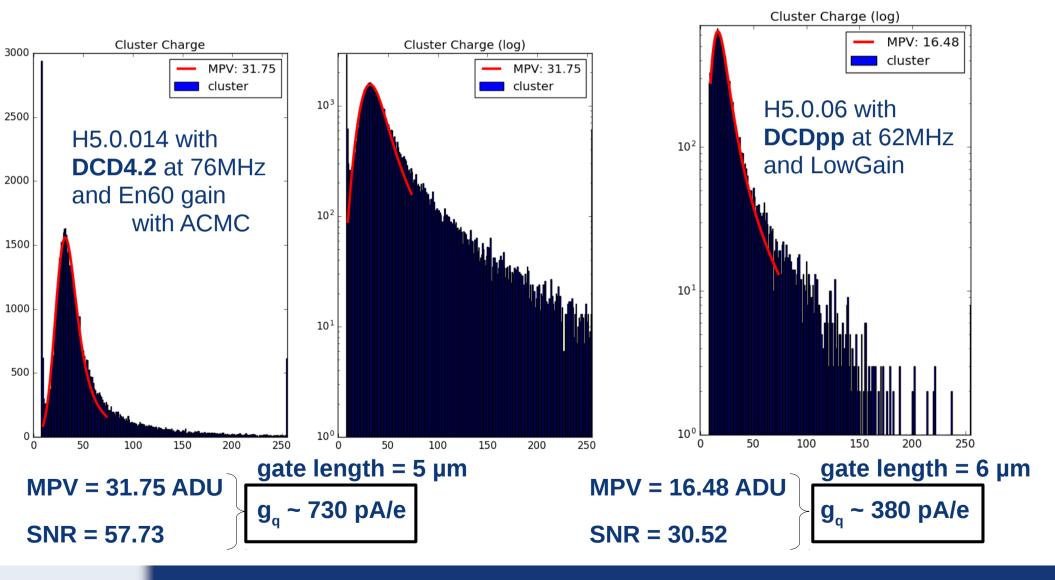

- Sr90 spectrum measured with H5.0.14 with DCD4.2 at gain En60

- compare to DCDpp measurement

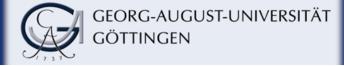

- Sr90 spectrum measured with H5.0.24 with DCD4.1 at gain En60

- done with ACMC and 2bit DAC offset at full speed (GCK 76MHz)!

# Conclusion

- DCD4.x gain implementation confirmed

- all Hybrid5 boards with DCD4.1 and DCD4.2 could be optimized

- after optimization both DCD4.x performance within specifications

- ACMC and 2bit DAC offset functional on both DCD4.x

- Sr90 source spectrum measured with a SNR of 57

- up to now both DCD4.1 and DCD4.2 seem to be fully functional

- both new DCD designs seem to be applicable for the final modules

- ToDo:

source measurements with ACMC, 2-bit DAC offset and gated mode

# BACKUP

- on DCDpp

- with ACMC on and matrix on, need to adjust IPAddOut to shift pedestal distribution in dynamic range

- when matrix blocked: need to increase IPAddIn

- why does IPAddIn have an effect at all? should be compensated by ACMC just as VNSubIn

- on DCD4.2

- when ACMC turned on, no need to adjust IPAddOut/In

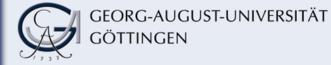

## H5.0.24 (DCD4.1) Bad Channels

#### long codes (DNL > 10)

- ADC curves show very large DAC offsets

- several μA offset before ADC curve starts

- VNSubIn/Out and IPAddIn/Out all 0

- for gain EN30 and extended DHE current source DAC range

- could perform ADC optimization, optimal working point with good performance

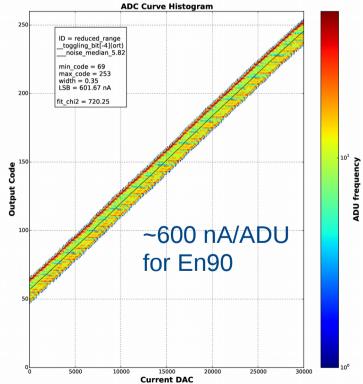

- for lower gains (En60, En90)

- ADC curves slopes extremely small

in the order of 600-1200 nA/ADU

and noise of > 6 ADU

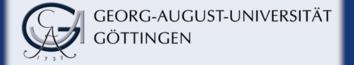

## **Gate-On vs DHE Current Source**

#### **DHE Source**

channel112\_dacifbpbias-070\_\_\_INLpp\_12.13\_\_\_INLpp\_middle\_12.13

#### **Gate-On Source**

channel112\_dacifbpbias-070

• same optimal working points are found with Gate-On source measurements

## **Gate-On vs DHE Current Source**

### **DHE Source**

#### **Gate-On Source**

• similar for RefIn-AmpLow and IFBPBias sweeps

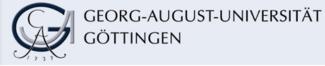

## **INLpp and Gain Spread**

$\rightarrow$  requiring a gain spread <= 5 %, INLpp values up to 7-8 are still ok

check ADC curve for noise, INLpp, long codes, code range and bit errors

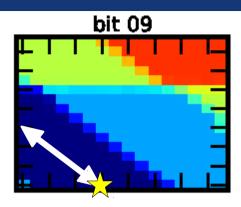

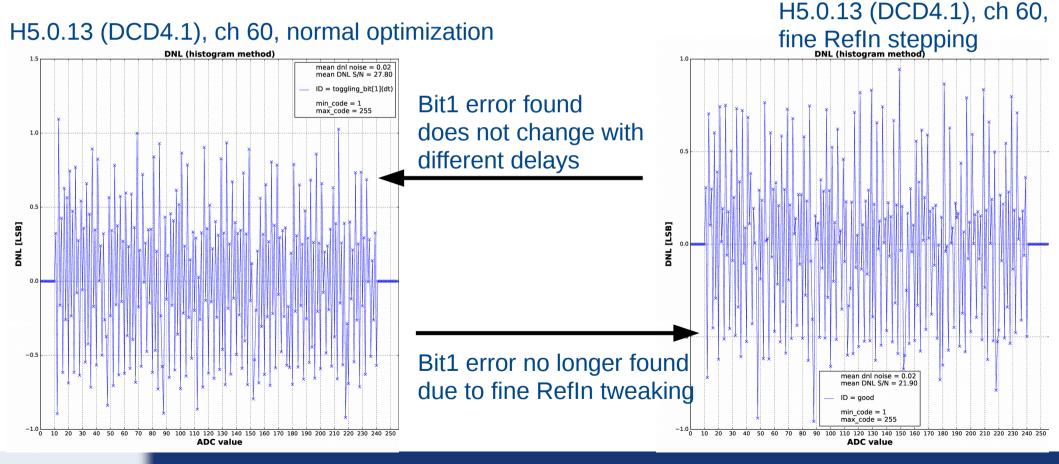

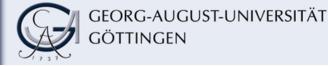

### Bit1 error recognized in DNL topology

# Bit6 error recognized via ADC curve outliers

- confirmed by simulation

- distinct from long code topologies

## **Fine RefIn Tweaking**

- Bit1 error topologies

- do not change with different delay optimization

- small change with RefIn voltage

- performed a fine RefIn stepping optimization