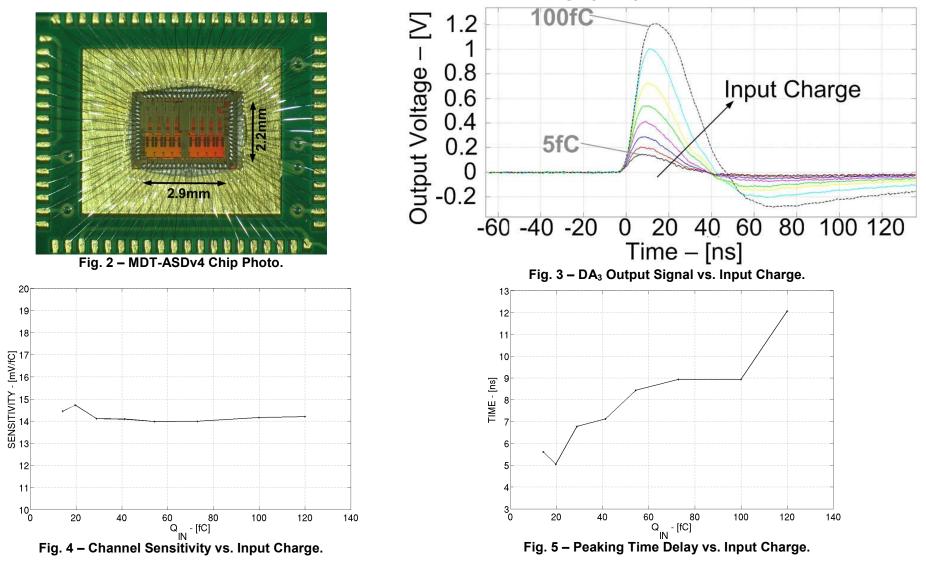

# ATLAS MDT ASD\_V4

Design

May 29<sup>th</sup>, 2017

Federica Resta Marcello De Matteis

andrea.baschirotto@sparklingic.com

- Channel Block Scheme  $\leftarrow \leftarrow \leftarrow$

- Charge Sensitive Preamplifier

- Differential Amplifiers

- Wilkinson ADC

- Measurements Summary

- Conclusion

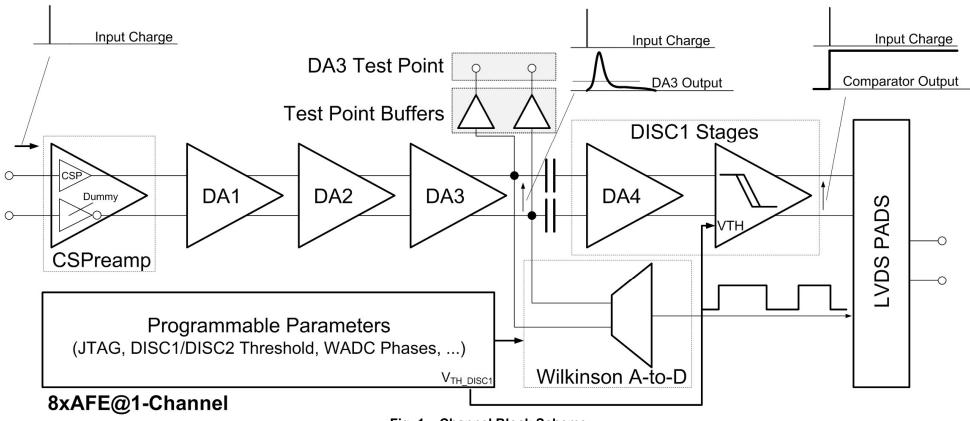

## ASDv4 Channel Block Scheme

Fig. 1 – Channel Block Scheme.

#### **Channel Critical Design Points (1/2)**

- <u>CMOS Technological Node</u>

- o **130nm**

- 3.3V Supply Voltage

- $\,\circ\,$  V\_{TH} Reduction

- 0.45V vs 0.75V

- $_{\odot}\,$  Sligth Reduction of intrinsic MOS gain

- Smaller Signal

- $_{\odot}\,$  Substrate influenced by rail-to-rail digital signals

- $\circ$  Smaller Area

- <u>Detector Parasitic Capacitance</u>

- 60pF

#### Required a <u>CAREFUL</u> CSPreamp Design

### **Channel Critical Design Points (1/2)**

- <u>CSPreamp</u>

- INPUT and KEY BLOCK

- Charge to Voltage Conversion

- $_{\odot}\,$  Essential Matlab Model for performance optimization

- Noise

- Sensitivity

- Peaking Time Delay

- Parasitic Capacitance at CSPremp Output

- $_{\odot}\,$  To guarantee a good conversion speed

- Channel Block Scheme

- Charge Sensitive Preamplifier  $\leftarrow \leftarrow \leftarrow$

- Differential Amplifiers

- Wilkinson ADC

- Measurements Summary

- Conclusion

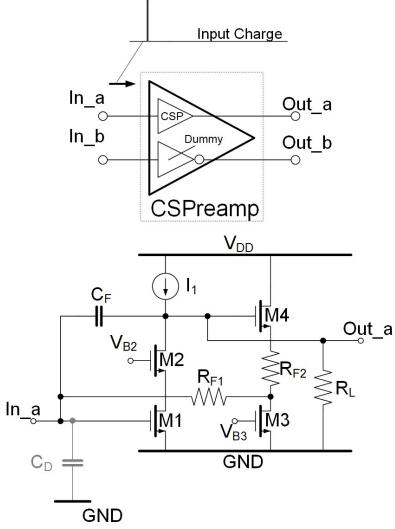

## ASDv4 Charge Sensitive Preamplifier

- Pseudo-Differential Structure

- 2 identical Charge Sensitive Amplifiers

- CSPreamp

- CSPreamp Dummy

- Feedback Components:

- $\begin{array}{c} \circ \ C_{F} \\ \circ \ R_{F} = R_{F1} + R_{F2} \end{array}$

## ASDv4 Charge Sensitive Preamplifier

$$T(s) \cong -R_F \cdot \frac{1 - s \frac{C_F}{g_{m1}}}{\left(1 + s C_F R_F \cdot \left(1 + \frac{C_D}{C_F} \left(1 + \frac{R_L}{R_F}\right) \frac{1}{1 + g_{m1} R_L}\right)\right) \cdot \left(1 + s \frac{C_D}{g_{m1}}\right)}$$

- With

- $\circ$  Detector Capacitance (C<sub>D</sub>)

- $\circ$  Feedback Capacitance (C<sub>F</sub>)

- Feedback Resistor (R<sub>F</sub>=R<sub>F1</sub>+R<sub>F2</sub>)

- $_{\odot}$  Load Resistor (R<sub>L</sub>)

- DC Loop Gain (g<sub>m1</sub>·R<sub>L</sub>≈400)

- C<sub>D</sub>/C<sub>F</sub>≈88

## ASDv4 Charge Sensitive Preamplifier

$$T(s) \cong -R_F \cdot \frac{1 - s \frac{C_F}{g_{m_1}}}{\left(1 + s C_F R_F \cdot \left(1 + \frac{C_D}{C_F} \left(1 + \frac{R_L}{R_F}\right) \frac{1}{1 + g_{m_1} R_L}\right)\right) \cdot \left(1 + s \frac{C_D}{g_{m_1}}\right)}$$

• Choosing

$$\circ R_L = R_F$$

$$\circ g_{m_1} >> 1/R_F$$

- High Frequency Zero (≈5GHz)

- CSPreamp Transfer Function can be approximated to:

$$T(s) \cong -R_F \cdot \frac{1}{\left(1 + sC_F R_F \cdot \left(1 + 2 \cdot \frac{C_D}{C_F} \cdot \frac{1}{1 + g_{m1} R_L}\right)\right) \cdot \left(1 + s \frac{C_D}{g_{m1}}\right)}$$

## ASDv4 CSPreamp Dominant Pole

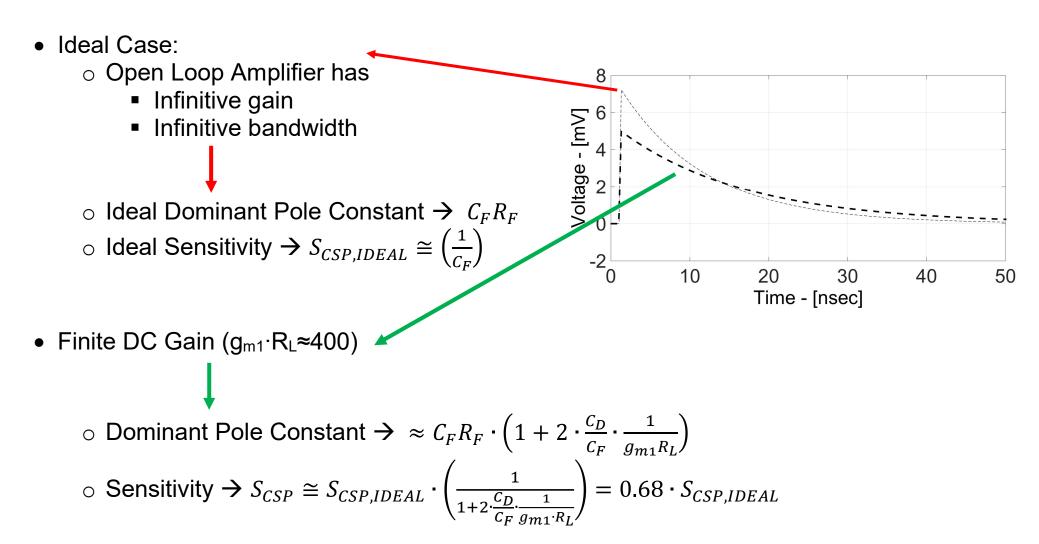

# ASDv4 CSPreamp Second Pole Effect

Ideal Case: Open Loop Amplifier has 8 IDEAL Infinitive gain \_With C<sub>D</sub> (and Two poles) Infinitive bandwidth With  $C_{D}$  (and One pole) ○ Ideal Dominant Pole Constant  $\rightarrow C_F R_F$ ○ Ideal Sensitivity →  $S_{CSP,IDEAL} \cong \left(\frac{1}{C_{r}}\right)$ -2<sub>0</sub> 10 20 30 40 50 Time - [nsec] Finite DC Gain (g<sub>m1</sub>·R<sub>L</sub>≈400) ○ Dominant Pole Constant  $\rightarrow \approx C_F R_F \cdot \left(1 + 2 \cdot \frac{C_D}{C_F} \cdot \frac{1}{g_{m1}R_L}\right)$ ○ Second Pole Constant →  $\approx \frac{g_{m1}}{C_D}$ ○ Sensitivity →  $S_{CSP} \cong S_{CSP,IDEAL} \cdot \left(\frac{1}{1+2 \cdot \frac{C_D}{C_E} \cdot \frac{1}{a_{m1} \cdot B_L}}\right) = 0.68 \cdot S_{CSP,IDEAL}$

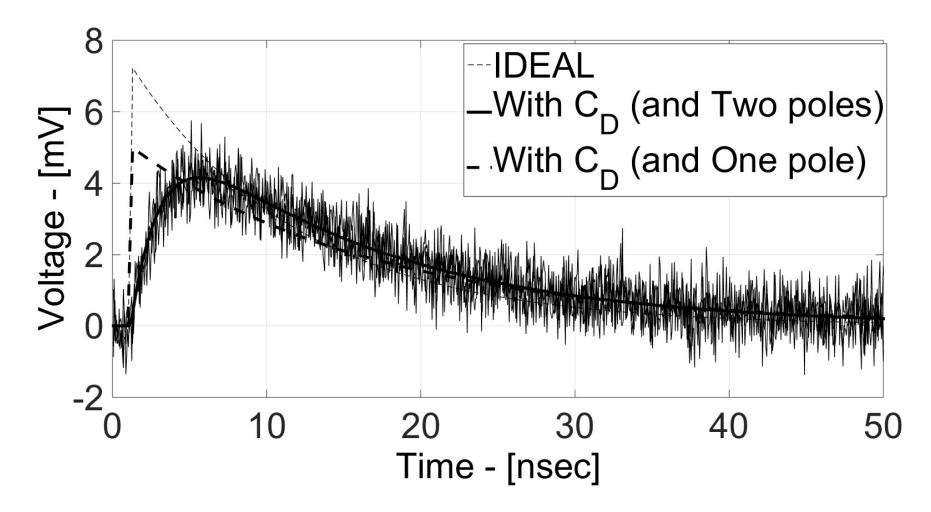

## ASDv4 CSPreamp Transient Noise Model

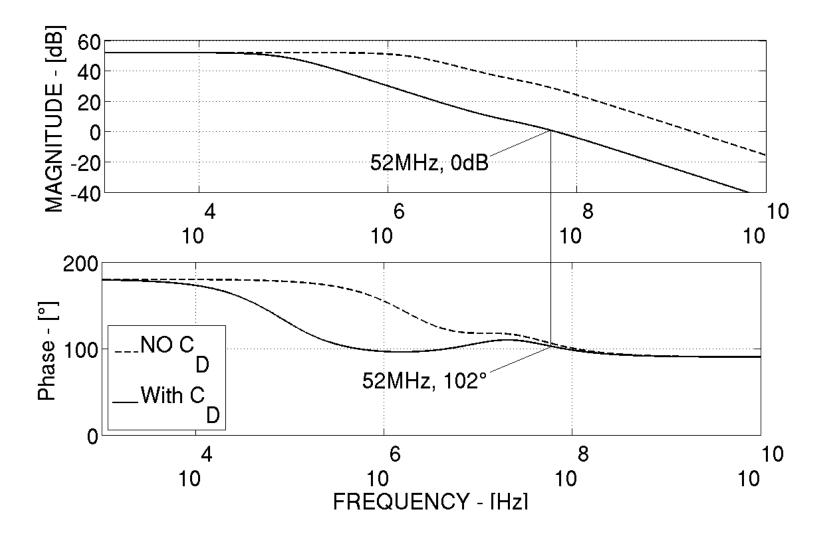

## ASDv4 CSPreamp Loop Gain

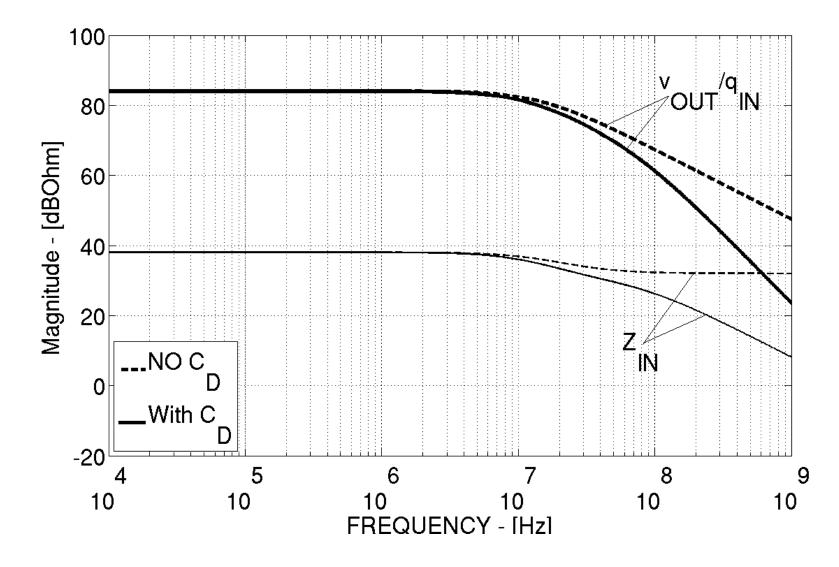

# ASDv4 CSPreamp Frequency Responses

### **CSPreamp Design Parameters Summary**

| Parameter                   | Min             | Nominal         | Max             |

|-----------------------------|-----------------|-----------------|-----------------|

| Current<br>Consumption      | 1.8mA           | 2.1mA           | 2.6mA           |

| Supply-Voltage              | 3.3V            | 3.3V            | 3.3V            |

| Peaking Time<br>Delay (PTD) | 8ns             | 7ns             | 6.2ns           |

| DC-Gain                     | $78 dB\Omega$   | 82dBΩ           | $85 dB\Omega$   |

| -3dB Bandwidth              | 9MHz            | 11MHz           | 13.2MHz         |

| Loop-Gain PM                | 90°             | 102°            | 103°            |

| Output Noise                | $0.63 mV_{RMS}$ | $0.55 mV_{RMS}$ | $0.47 mV_{RMS}$ |

| In-Band IRN PSD             | 5.8nV/√Hz       | 5nV/√Hz         | 4nV/√Hz         |

- Channel Block Scheme

- Charge Sensitive Preamplifier

- Differential Amplifiers  $\leftarrow \leftarrow \leftarrow$

- Wilkinson ADC

- Measurements Summary

- Conclusion

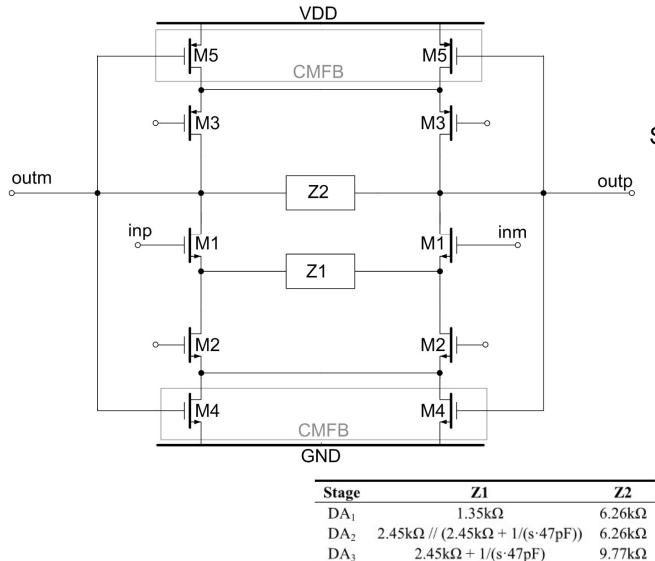

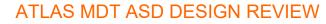

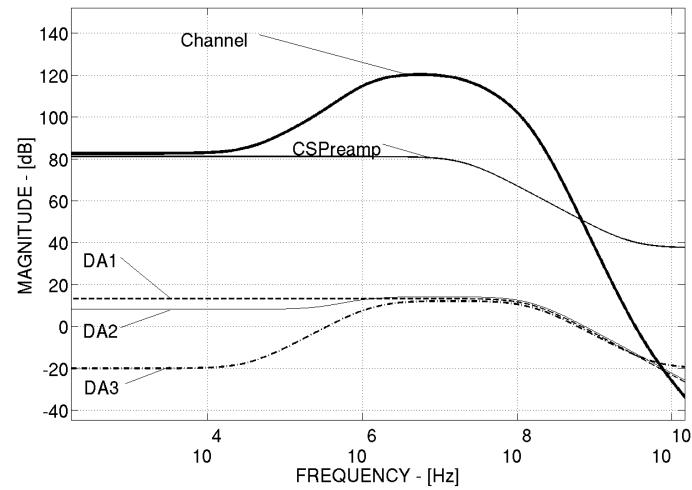

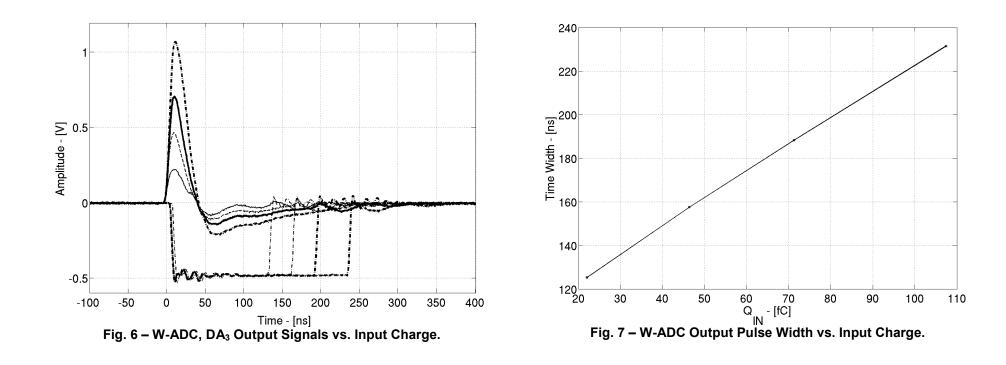

#### **Differential Amplifiers**

Smaller CMFB MOS:

- Reduce CSPreamp Parasitic Capacitance Load

- Manage Peaking Time Delay

sparkling I

## ASDv4 Differential Amplifiers

- 5MHz center frequency

- 30kHz high-pass frequency

- +6dB/octave slope

- Channel Block Scheme

- Charge Sensitive Preamplifier

- Differential Amplifiers

- Wilkinson ADC  $\leftarrow \leftarrow \leftarrow$

- Measurements Summary

- Conclusion

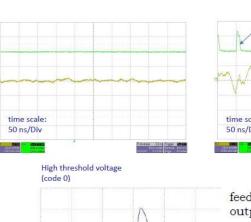

## ASDv4 **Wilkinson ADC**

- Channel Block Scheme

- Charge Sensitive Preamplifier

- Differential Amplifiers

- Wilkinson ADC

- Measurements Summary ← ← ←

- Conclusion

**Measurements Summary (1/2)**

## ASDv4 Measurements Summary (2/2)

- Channel Block Scheme

- Charge Sensitive Preamplifier

- Differential Amplifiers

- Wilkinson ADC

- Measurements Summary

- Conclusion  $\leftarrow \leftarrow \leftarrow$

#### Conclusion

- MDT-ASDv4

- $_{\odot}\,$  Management of 60pF-C\_D

- $\,\circ\,$  Accurate q\_IN-to-V conversion

- $\circ$  Maximum Peaking Time Delay → 12ns

- Linear V-to-T conversion

- $\circ$  Area of 6.38mm<sup>2</sup>

| Total Current Consumption                | 162mA   |  |

|------------------------------------------|---------|--|

| Channel <sup>1</sup> Current Consumption | 18.7mA* |  |

| Channel <sup>2</sup> Current Consumption | 12.56mA |  |

| Total Power Consumption                  | 535mW   |  |

| @3.3V of Supply Voltage                  | 555000  |  |

| Channel <sup>1</sup> Power Consumption   | 61.9mW  |  |

| @3.3V of Supply Voltage                  |         |  |

| Channel <sup>2</sup> Power Consumption   | 41.44mW |  |

| @3.3V of Supply Voltage                  |         |  |

| * 32.7% LVDS                             |         |  |

| 21% CSP                                  |         |  |

| 20.2% Wilkinson A                        | DC      |  |

| 16% DAi <sub>i=1,2,3,4</sub> ch          | ain     |  |

| 6.5% DISC1                               |         |  |

| BLOCK                                     | PIN NAME                    | DESCRIPTION                       | ТҮРЕ        | #  | I/O<br>INTERFACE                                                |

|-------------------------------------------|-----------------------------|-----------------------------------|-------------|----|-----------------------------------------------------------------|

|                                           | SCLK                        | Clock Line                        | Digital In  | 1  | Vpulse Generator                                                |

| JTAG<br>Serial<br>Interface<br>6 PADs     | SIN                         | Load Control Line                 | Digital In  | 1  | Vbit Generator                                                  |

|                                           | SDOWN                       | Down Control Line                 | Digital In  | 1  | Vpulse Generator                                                |

|                                           | SHIFT                       | Shift Control Line                | Digital In  | 1  | Vpulse Generator                                                |

|                                           | SLOAD                       | Data Line                         | Digital In  | 1  | Vpulse Generator                                                |

|                                           | SOUT                        | Data Line                         | Digital Out | 1  | noConn Istance                                                  |

| MDT-ASD<br>V4 Channel<br>32 PADs          | <ina0:ina7></ina0:ina7>     | Positive Channel<br>Input         | Analog In   | 8  | 1 nF Cap or Current Gen<br>erator in parallel with<br>60 pF Cap |

|                                           | <inb0:inb7></inb0:inb7>     | Negative Channel<br>Input         | Analog In   | 8  | 470 pF Cap                                                      |

|                                           | <outa0:outa7></outa0:outa7> | Positive Channel<br>Output        | Analog Out  | 8  | Input 'A' LVDS Termina<br>tion                                  |

|                                           | <outb0:outb7></outb0:outb7> | Negative Channel<br>Output        | Analog Out  | 8  | Input 'B' LVDS Termina<br>tion                                  |

| Channel#7<br>Buffer<br>2 PADs             | anaa                        | DA <sub>30a</sub><br>of Channel#7 | Analog Out  | 1  | 1 pF Cap                                                        |

|                                           | anab                        | DA <sub>3ob</sub><br>of Channel#7 | Analog Out  | 1  | 1 pF Cap                                                        |

| Current<br>Channels<br>Generator<br>1 PAD | IBIAS_10µA                  | Current<br>Generator              | Analog In   | 1  | Current Generator o<br>10 μA±5%                                 |

| Supplies<br>29 PADs                       | <vdd1:vddq></vdd1:vddq>     | Supply Voltage                    | Analog In   | 10 | DC-Voltage Generator o<br>3.3 V± 5 %                            |

|                                           | <sub1:subq></sub1:subq>     | Ground Voltage                    | Analog In   | 7  | DC-Voltage Generator o<br>0 V                                   |

|                                           | <gnd1:gndq></gnd1:gndq>     | Ground Voltage                    | Analog In   | 12 | DC-Voltage Generator o<br>0 V                                   |

Fig. 8 – MDT-ASDv4 Pin Table (70 Pins).

<sup>1</sup> Including CSP+DA1+DA2+DA3+DA4+DISC1+WILKINSON ADC+MUX+LVDS <sup>2</sup> Including CSP+DA1+DA2+DA3+DA4+DISC1+WILKINSON ADC

5/26/17

#### **Conclusion – Measurements Issues**

- 1. Substrate Noise

- 2. Channel Mismatch

#### 3. Smaller Deadtime Range

- $\succ$  No input signal, programmable board connected to set different threshold voltage values

- Baseline noise impact, which should have only influenced the comparison result at the output of DISC1, now seems to also affect the previous stages the amplifier chain, and the corresponding effect can be observed at the analog buffer's output

- > Possible backward coupling from DISC1 to the analog chain is one reasonable explanation

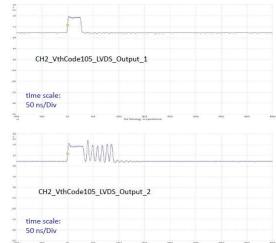

Low threshold voltage (code 105)

feedback of discr. output to input of preamp (~35 mV)

show the LVDS output of a CH2 in ToT mode, HystCode=0, VthCode=105 (-43mV), it may cause oscillations. There is a kind of "stable oscillating" threshold. After reaching this threshold. the output starts to oscillate (here around code 107-108). Interesting thing is that to stop oscillation the threshold has to be pulled back very far, far

more from a level when it start to

happen.

25.07.2015

5/26/17