W37\_OF1

Harrison Schreeck, Philipp Wieduwilt

2<sup>nd</sup> Institute Of Physics, Georg-August-Universität Göttingen

02/08/17

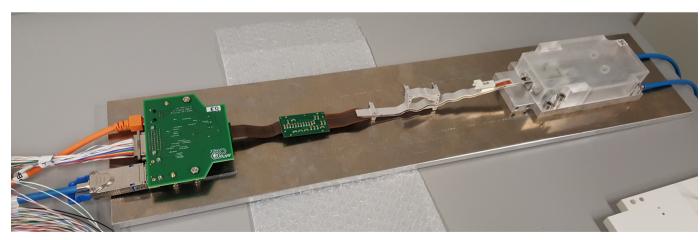

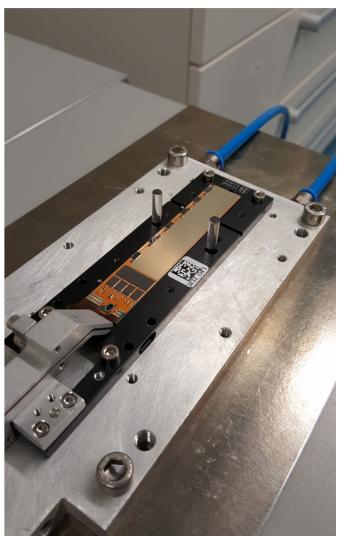

# Module Setup

- clamp attached

- inner and outer cover in place

- cooling with chiller at 20°C

- no vacuum

## Module Setup

- configDB entry generated from templates

- file 'W37\_OF1\_Goettingen'

- first power up and configuration manually

- full JTAG chain functional

- currents at expected levels

- all HS links up

- now using the automatic power up sequence

- most recent commit: 513 (includes offsets)

#### Module Parameters

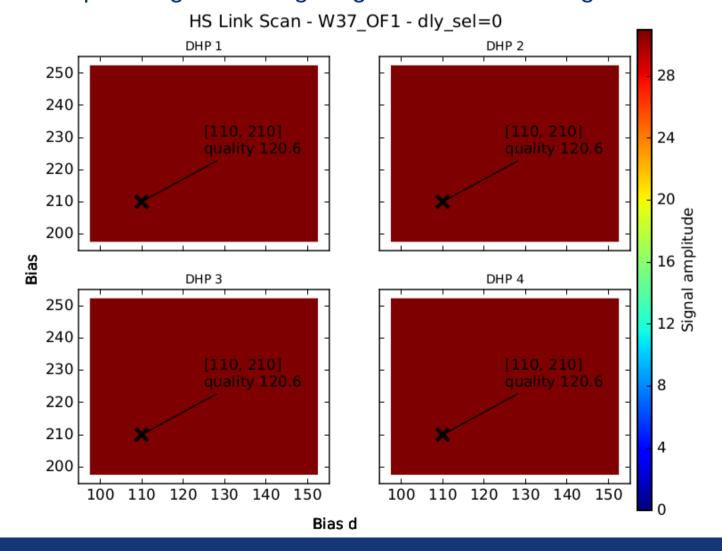

- HS Links:

- Bias = 210

- Biasd = 110

- Delay = 0

- DCD:

- Amplow = 275 mV

- Refln = 725 mV

- Ipsource = 70

- Ipsource\_middle = 67

- lpsource2 = 70

- IFBPBias = 70

- Gain = En90

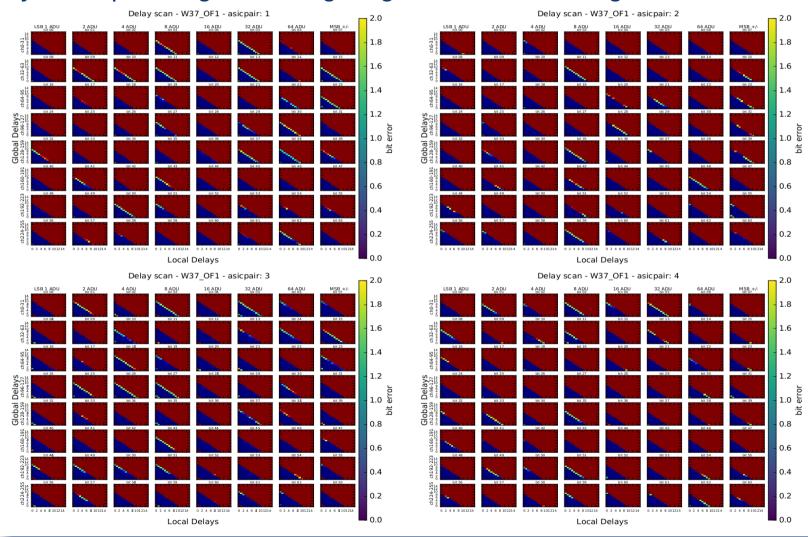

- DCD data delays:

- Global = 0

- Local = 4.5

- DCD offset delays:

- offset frame sync dly = 0

- offset des dly = 8

- offset dcd dlys = [3,4]

- Voltages:

- Clear-On = 19 V

- Clear-Off = 5 V

- Gate-Off = 5 V

- Source = 6 V

- CCG = 0 V

- Guard = -5 V

- Bulk = 10 V

- HV = -70 V

- Drift = -5 V

- Gate-On = [-1.5V, -1.7V]

## Module Temperatures

- measured via DHP temperature diode

- all covers, with clamp, chiller @ 18°C

- only DHPs powered

- 25-30

- DHPs and DCD powered, but DCD analog OFF

- 30-35

- --> for both W37 OF1 and EMCM

- DHPs and DCDs powered and DCD analog ON

- 50-58

- all powered (DCDs analog ON and matrix)

- 55-60

- calibration?

- even with only DHPs powered: 5-10 spread between DHP temperatures

# **HS Link Optimization**

- Scan: https://elog.belle2.org/elog/PXD-Mass-Testing/170

- Analysis: https://elog.belle2.org/elog/PXD-Mass-Testing/171

# **Delay Optimization**

- Scan: https://elog.belle2.org/elog/PXD-Mass-Testing/147

- Analysis: https://elog.belle2.org/elog/PXD-Mass-Testing/148

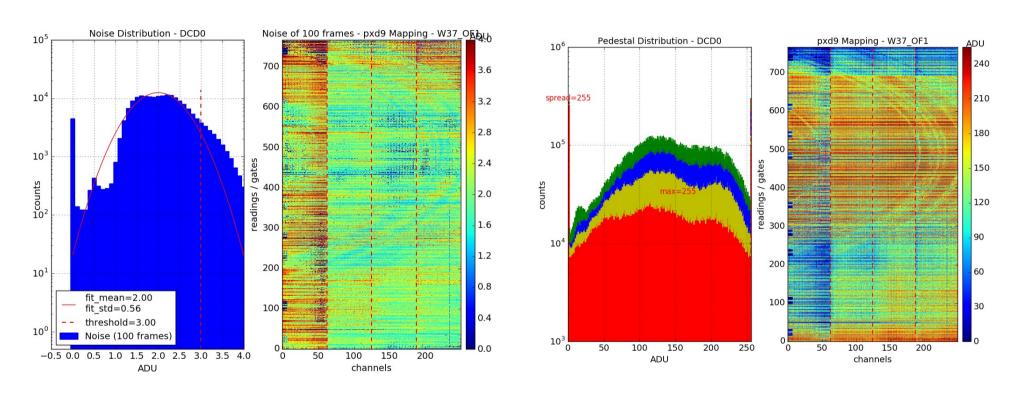

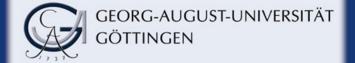

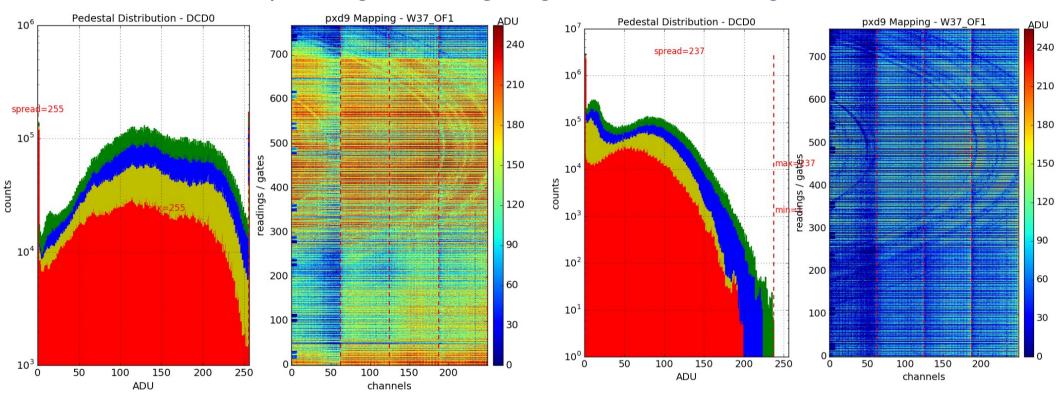

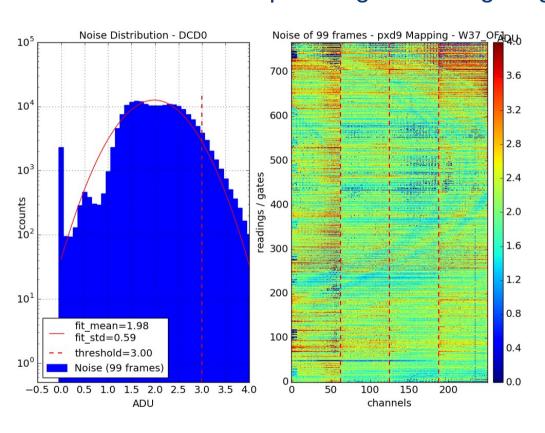

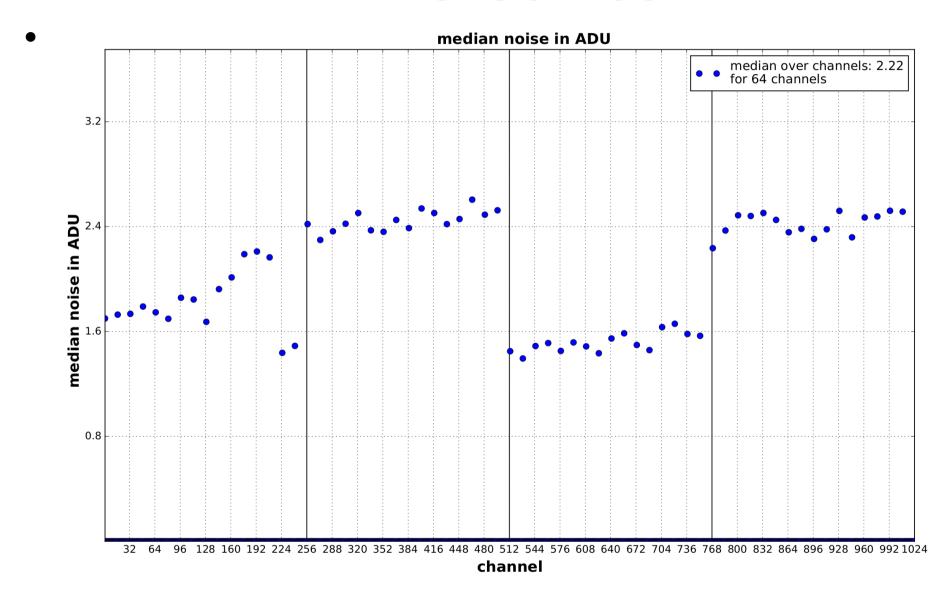

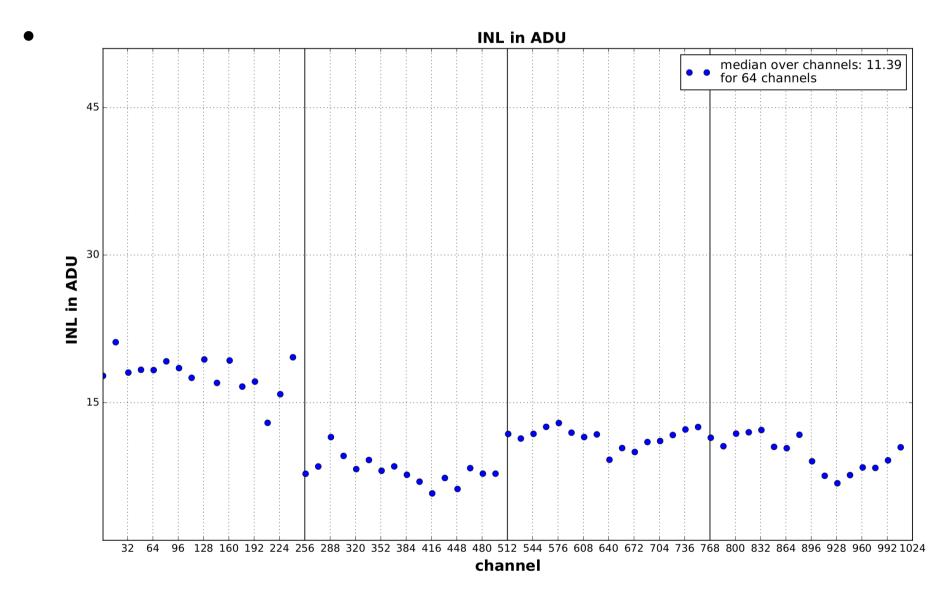

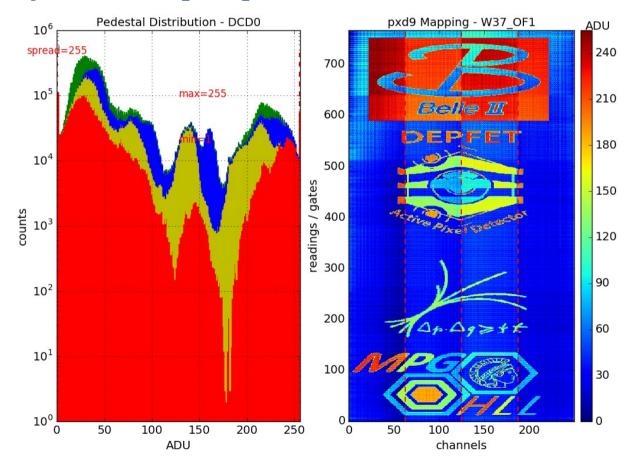

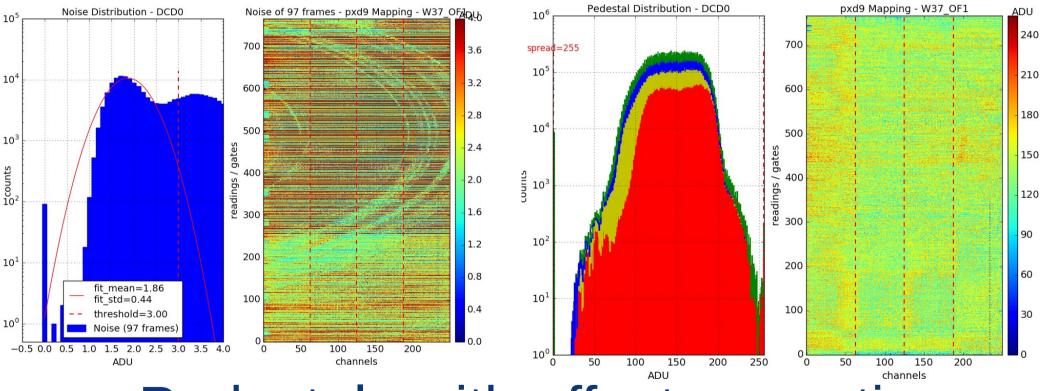

#### Pedestal and Noise

Pedestals with optimized VNSubIn (22 - 22 - 24 - 24) and GateOn voltages (-1500mV, -1600mV, -1700mV)

#### **ACMC**

- ACMC off: https://elog.belle2.org/elog/PXD-Mass-Testing/229

- ACMC on: https://elog.belle2.org/elog/PXD-Mass-Testing/228

**ACMC** off

ACMC on

#### **ACMC**

- ACMC off: https://elog.belle2.org/elog/PXD-Mass-Testing/229

- ACMC on: https://elog.belle2.org/elog/PXD-Mass-Testing/228

**ACMC** off

ACMC on

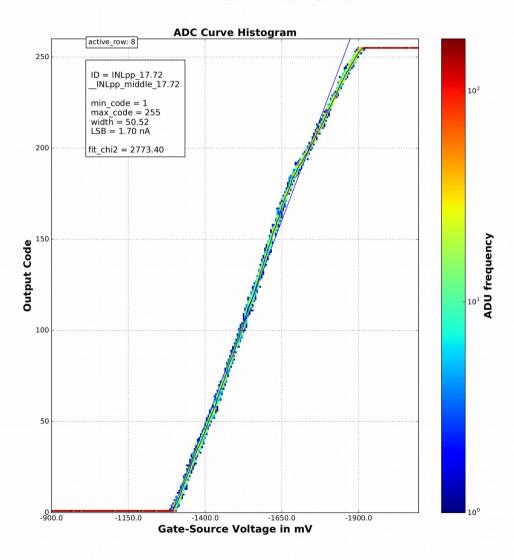

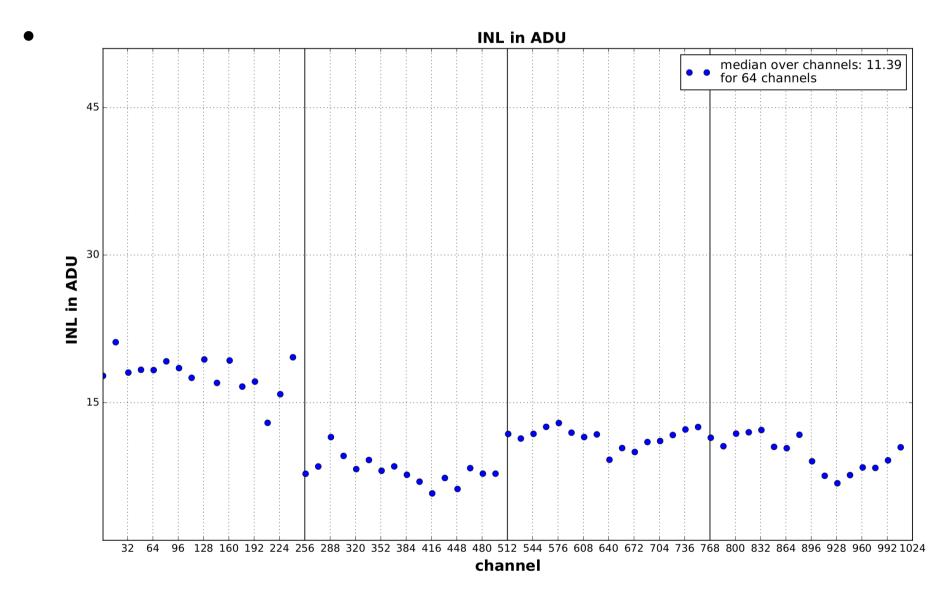

channel0000\_INLpp\_17.72\_INLpp\_middle\_17.72

- Only gate source measurements possible

- ADC curves quite noisy

- high INL

- measurement very time consuming (~10 minutes for 64 channels)

## Offset Delays

- Matrix blocked (2000 mV) and delay optimization performed

- Local delays set to [3,4]

#### Offset Calibration

- Scan: https://elog.belle2.org/elog/PXD-Mass-Testing/288

- Analysis: https://elog.belle2.org/elog/PXD-Mass-Testing/289

# Pedestals with offset correction enabled

# Summary

- DHPT HS Links

- stable links found

delays optimized

- ADCs optimization using small parameter space

- only allchannel scan performed

- 2bit offset (delay and current source optimization)

- optimization succesfully performed

- DCD analog common mode correction

- functionality confirmed

- Source measurement different regions

- not yet performed

- Gated mode: simplified test using manual switch for the VETO and standard

DHH firmware

- not yet performed