# DHP Test Chip Design Status

Norbert Wermes for Tomasz Hemperek

#### **Functionalities**

- Record 4x1024 rows of raw data (4 frames). plus 1x pedestal?

- Trigger ID 8bit (may be obsolete), Frame ID 8bit

- Latency for up to 1024 rows before trigger

- Configuration through JTAG protocol standard (IEEE)

- Boundary scan test included through JTAG

- Temperature measurement

- Single bit error protected memories + triple redundant registers

- High speed CML output using Aurora protocol

- 5 operating modes

- DO NOTHING

- TEST

- STORE DATA TO MEM

- NORMAL AQUISITION (data, pedestals, subtration, clustering)

- SEND MEM

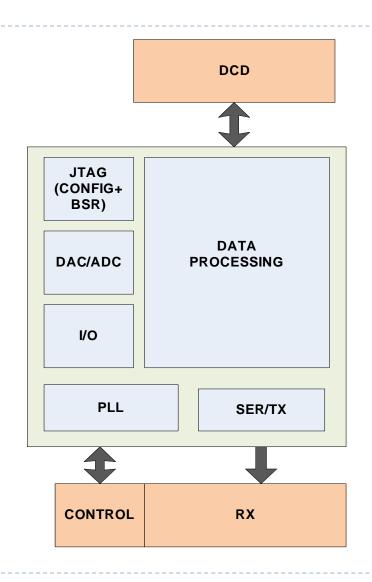

### DHP Concept

- Main clock 100MHz (from erxtern, DHH)

- DCD clock 400MHz

- Output clock 0.4-1GHz

## Status/Plans

#### people

Tomasz Hemperek (full time: memories, SER-Tx, processing) (Hans Krüger)

Andre Kruth (I/O blocks and ... perhaps PLL)

Barcelona friends ... next talk (DAC/ADC, biasing circuit)

- <u>Testchip</u> for the main blocks planned

- 90 nm IBM technology / 9 metals

- submission date: 26/10/2009 (next one is 22/02/2010)

- − ~30 k\$

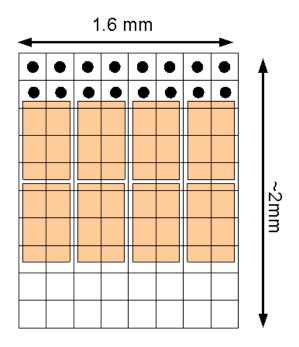

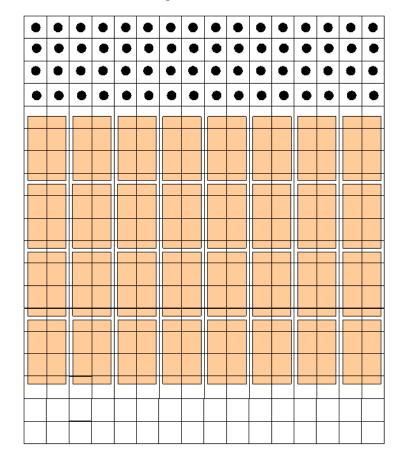

### Floor Plan

- Test Chip

- ¼ of the memory

- 1/4 of I/Os

- wire bonding ok

Final chip ? wire bonding?

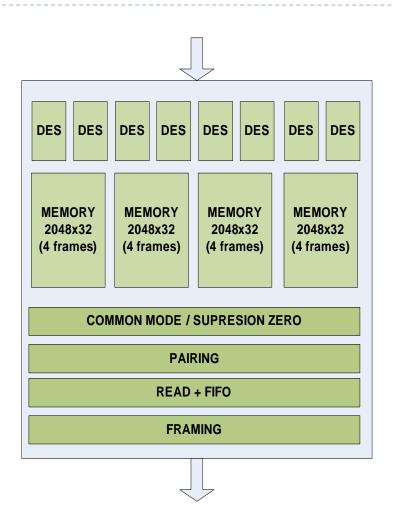

### Processing

- 2 deserializers/inputs share one memory

- buffering for max. 1 frame

- pedestal correction

- · common mode correction

- hit pairing

- readout

- output framing

## Summary

... with some luck we have a sizeable testchip at the beginning of 2010 from which we can plan the full chip (not a big step) ... most important: irradiation tests