# Vertex Ladder Engineering: from the STAR experience to an ILC design

A Vertex Detector for the ILC, Workshop at Ringberg Castle Ringberg, May 28-31, 2006

**Devis Contarato**

Lawrence Berkeley National Laboratory

M. Battaglia, B. Hooberman (UC Berkeley & LBNL) L. Greiner, H. Matis, H. Wieman (LBNL)

## **Outline**

- Introduction: the STAR Heavy Flavor Tracker

- Test facilities at LBNL

- STAR HFT prototype ladder testing

- Back-thinning studies

- Outlook: towards a ladder design for the ILC

# The upgrade of the STAR vertex detector

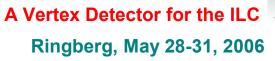

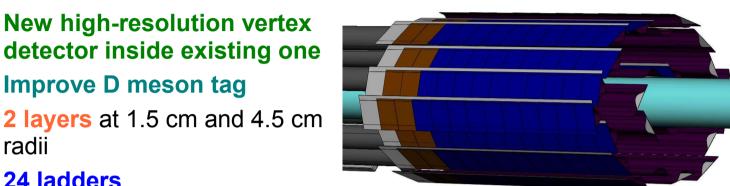

## View of the STAR Heavy Flavor Tracker

- Improve D meson tag

- 2 layers at 1.5 cm and 4.5 cm radii

- 24 ladders

- -2 cm  $\times$  20 cm each

- ~100 Mpixels, 30×30 µm<sup>2</sup>

- 4 ms readout time

- Rad-hard to 2 kRad/yr

- **Project approved:** funding for 2 years R&D followed by construction

- LBNL leadership of project

**Devis Contarato** VXD Ladder Engineering: from STAR to ILC

## **STAR/ILC VXD comparison**

|                            | <b>STAR</b>                | ILC                        |

|----------------------------|----------------------------|----------------------------|

| Performance drivers        | Low p <sub>T</sub> D       | b/c/τ tagging              |

| <b>Position resolution</b> | ~10 µm                     | 2-4 µm                     |

| <b>Radiation length</b>    | 0.3% X <sub>₀</sub> /layer | 0.1% X <sub>0</sub> /layer |

| Number of layers           | 2                          | 5-6                        |

| Ladders/layer              | 6+18                       | ?                          |

| <b>Operational T</b>       | 40°C                       | -10°C 20°C                 |

| Cooling                    | Air flow                   | ?                          |

| VTX mount                  | Side mount                 | Two sides                  |

**Devis Contarato**

VXD Ladder Engineering: from STAR to ILC

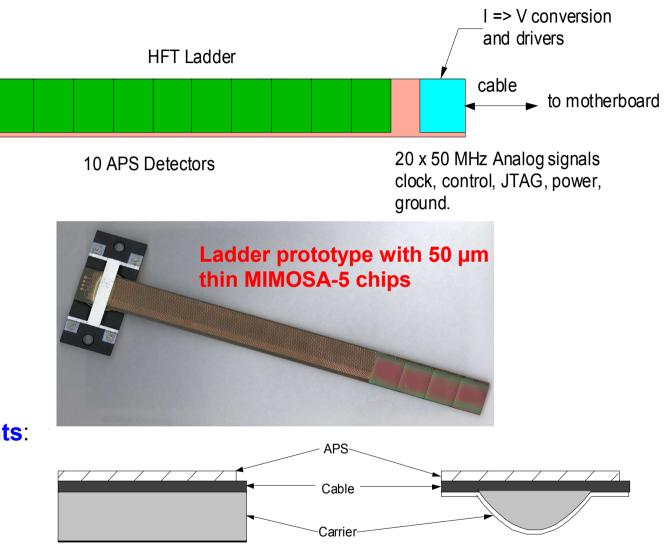

# **Prototype STAR HFT Ladder**

## 10 CMOS sensors

- At the end of the ladder:

- > 20 I → V converters and drivers

- Additional clock, control and JTAG connections

- Power and ground

- Analog signals and clock/control transferred to motherboard via fine twisted pair cable

- 3 basic ladder constituents:

- 1. APS sensor

- 2. Cable

- 3. Mechanical Carrier

## End view of 2 prototype designs

**Devis Contarato**

VXD Ladder Engineering: from STAR to ILC

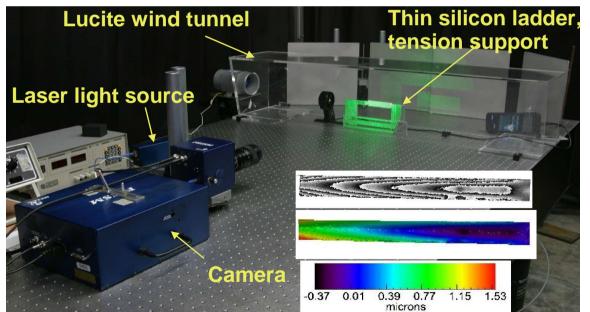

## **Test facilities at LBNL**

• Environmental chamber (down to -70°C) for characterization of temperature cycling and humidity effects on prototype ladders

• High resolution IR camera for studying temperature gradient of prototype ladders, e.g. to study heat dissipation under power cycling

• Facility for studies of cooling and mechanical stability with nitrogen and air flow, equipped with a laser holography system for real time measurement of distortions in prototype structures with sub-µm resolution

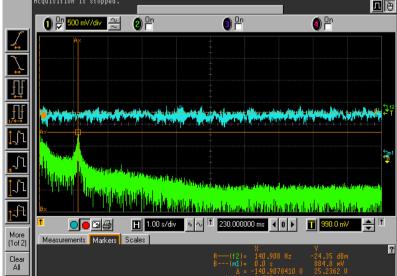

Capacitive probe system for sub-µm resolution measurement of reference positions. Bandpass of 1 KHz, above typical resonant frequencies of ladders

→ study displacements and vibrations induced by air cooling or other forces

• **Composite lab material** for fabrication of light structures

Devis Contarato VXD Ladder Engineering: from STAR to ILC

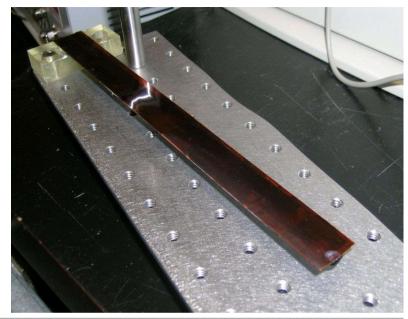

## **Test of STAR HFT Ladder Prototype**

# 2 carrier candidatesTop layer = 50 μm CFCOuter shell = 100 μm CFCMiddle layer = 3.2 mm RVCFill = RVCBottom layer = 50 μm CFCFill = RVC

X<sub>0</sub> =0.11 %

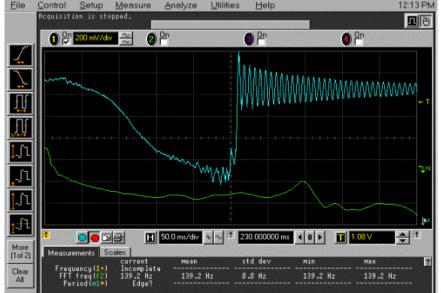

- Displacement as a function of time measured using capacitive probe at unsupported end of prototype ladder (carrier+kapton+50 µm silicon)

- Fundamental resonance frequency measured from FFT of oscillations:

- Measured = 139 Hz

- Calculated = 135 Hz

### A Vertex Detector for the ILC

**Ringberg, May 28-31, 2006**

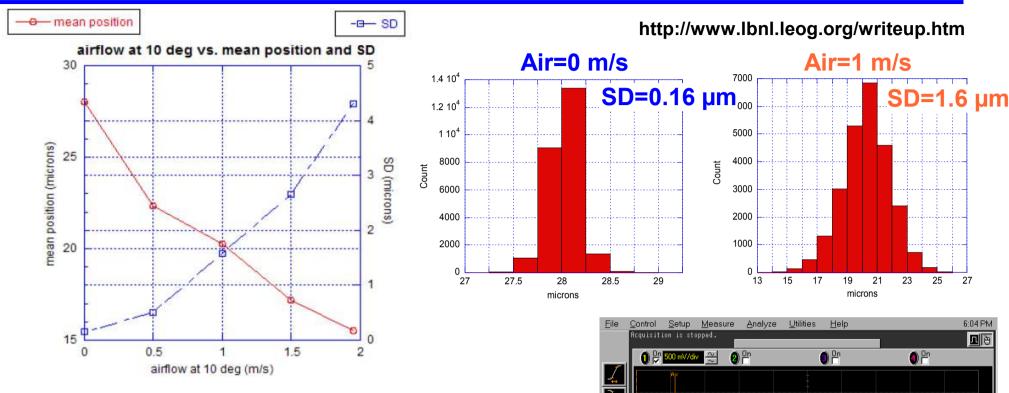

# **Vibration from air cooling**

• Airflow at 10° onto prototype ladder measured at unsupported end gives measured location distribution with SD~1.6  $\mu m$  at 1.0 m/s of airflow

• As the airflow increases, the free end of the ladder moves away from the capacitive probe, and the magnitude of the induced vibrations increases

# **Test of prototype Si flatness**

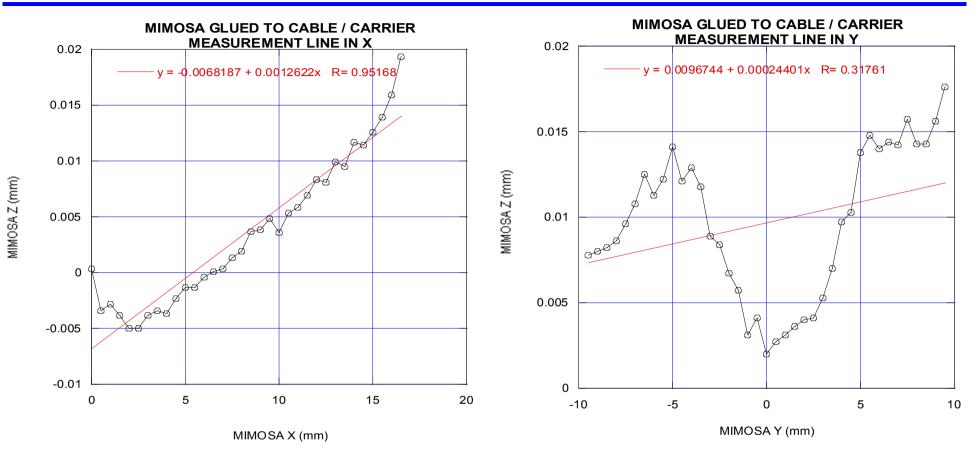

- Measurements performed at optical measuring machines at LBNL inspection and metrology shop

- 50 µm thin MIMOSA-5 sensors glued to cable and to support carrier

- $\bullet$  Variations within 20  $\mu m$  in both directions on sensor surface

- Individual pixel position can be located to the required accuracy by a parameterized location function

BERKELEY LAB

**Devis Contarato**

VXD Ladder Engineering: from STAR to ILC

## **Air cooling tests**

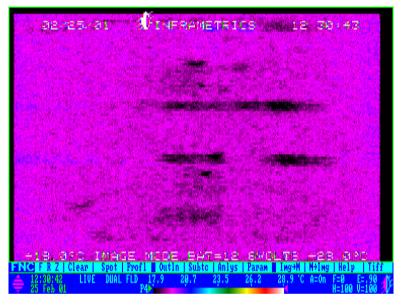

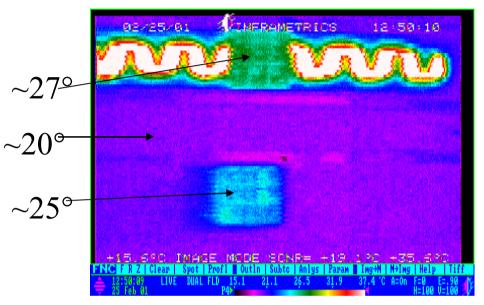

Airflow = 0 Heaters = off

Emissivity of Si and Kapton is uniform

• IR thermal imaging of Si and Kapton

Airflow = 0.8 m/s Heaters = on

Si temperature rises ~5-7°C above ambient Good uniformity in temperature over sensor

- Upper test piece: 2 layers of 2 cm x 2 cm x 50  $\mu$ m thick Si glued to Pt heater serpentine strip at 100 mW/cm<sup>2</sup>

- Lower test piece: 2 layers of 2 cm x 2 cm x 50 µm thick Si with resistor heating at 164 mW along the upper edge and 90 mW distributed over the rest of the piece

http://www.lbnl.leog.org/ir\_prelim\_writeup.htm

## **STAR HFT Ladder Prototype Cable**

- ~100 traces (2 LVDS pairs/sensor, clock, power, ground, control signals)

- 4 layer design, 25  $\mu m$  kapton, 20  $\mu m$  Al conductor

- Impedance controlled signal/clock pairs with power and ground geometrically arranged as shielding

X<sub>0</sub> =0.090 %

(for Al conductor)

| <u>Component</u>           | % radiation length | <u>Si equivalent (µm)</u> |

|----------------------------|--------------------|---------------------------|

| MIMOSA detector            | 0.0534             | 50                        |

| Adhesive                   | 0.0143             | 13.39                     |

| Cable assembly             | 0.090              | 83.92                     |

| Adhesive                   | 0.0143             | 13.39                     |

| Carbon fiber / RVC carrier | 0.11               | 103                       |

| <u>Total</u>               | <u>0.282</u>       | <u>263.7</u>              |

Devis Contarato VXD Ladder Engineering: from STAR to ILC

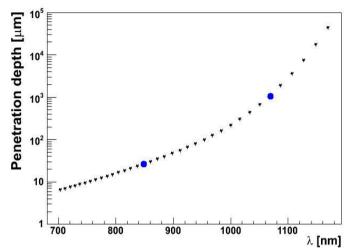

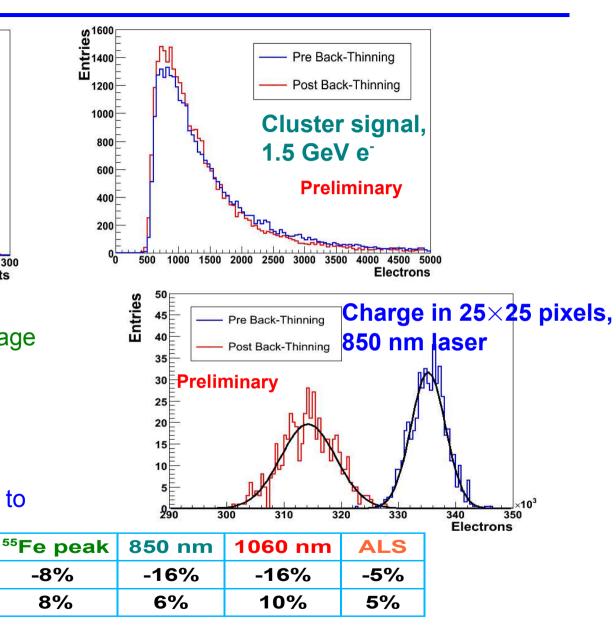

# **Back-thinning studies**

• Tests performed on diced MIMOSA-5 chips from IPHC/IReS (Strasbourg)

• AMS 0.6  $\mu$ m, 14  $\mu$ m epilayer, 1 Mpixels on reticle-size area of 1.7 $\times$ 1.9 cm<sup>2</sup>,

- 17 µm pixel pitch

- Chips initially mounted to PCB with reversible glue and fully tested with 1.5 GeV e<sup>-</sup> beam and lasers of different wavelengths → probe signal from different silicon depths and estimate substrate contribution

- Chips removed by heating to 120°C

- Back-thinning to 25-50 µm performed by Aptek (San Jose, CA), www.aptekindustries.com

- Proprietary hot wax formula for wafer mounting to stainless grinding plates

- Wet grind process + polishing

- In-situ thickness measurement

- Re-mounting and re-characterization

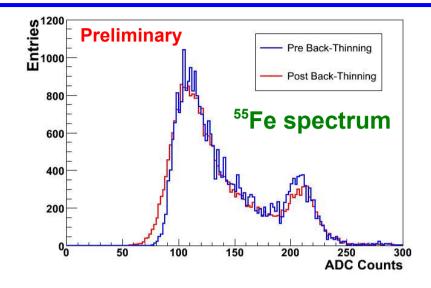

# Back-thinning to 50 µm: latest results

- Negligible variation of charge-to-voltage conversion gain

- No charge losses for MIP detection

- Small variations from laser tests: no significant contribution from substrate to collected charge

Mean

RMS

**Devis Contarato**

VXD Ladder Engineering: from STAR to ILC

+3%

7%

A Vertex Detector for the ILC

**Ringberg, May 28-31, 2006**

## **ILC LCRD Project at LBNL**

- New Linear Collider R&D (LCRD) project for FY 2006-2008

- Design and prototype low mass detector modules

- Fully characterize mechanical behavior with thinned Si chips

- Assess sensor technology specifics for CMOS and DEPFET pixels

- Study air flow cooling in terms of heat extraction and ladder stability

- Investigate off-line software alignment procedures using existing algorithm developed for BaBar

- Project recently approved! Funds starting with 55 k\$ for 2006, to be increased in 2007-2008

Devis Contarato VXD Ladder Engineering: from STAR to ILC