Theresa Goldschmidt

### Commissioning and Characterization of PXD Power Supply Calibration

International DEPFET workshop

Munich

16<sup>th</sup> May 2022

#### **MOTIVATION**

### Calibration drift and changes through repairs expected

- → Set-up at KEK needed

- Commission set-up in Bonn

- Study calibration stability and drift

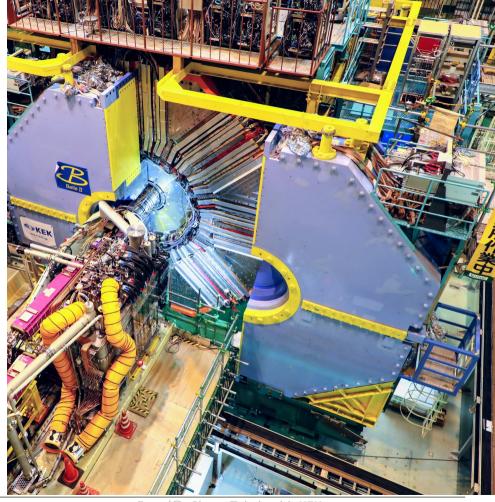

Foto/©: Shota Takahashi, KEK

# THE SET-UP WORKING PRINCIPLE FIRST CALIBRATIONS OUTLOOK

#### THE BELLE II POWER SUPPLY

- Supplies the PXD module with 24 different voltages

- Remote sensing of each channel

14m long \_ power cables

Monitoring information of node 56

|         |                  |                  |                       |                      |              |                      | _ |

|---------|------------------|------------------|-----------------------|----------------------|--------------|----------------------|---|

|         | Set Voltage (mV) | Set Current (mA) | Itage at Regulator (m | Voltage at Load (mV) | Current (mA) | Regulator Status Bit |   |

| DHP_IO  | 0                | 0                | -6                    | -4                   | -8           | LOW                  |   |

| SW_DVDD | 0                | 0                | -6                    | -6                   | -4           | LOW                  |   |

2 set values

3 monitoring values

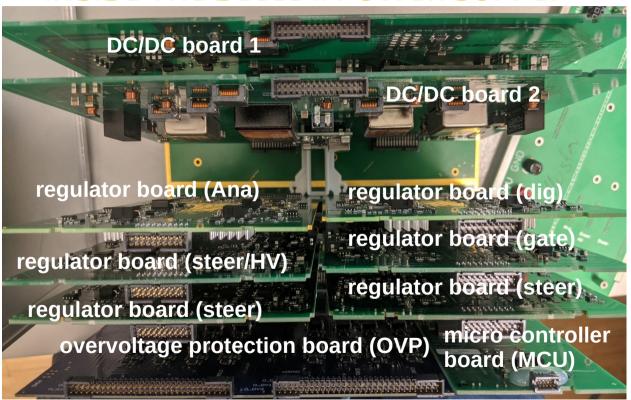

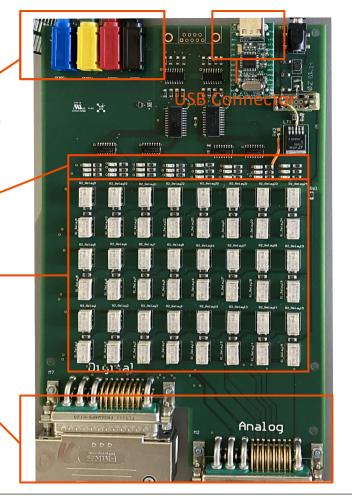

#### INSIDE THE BELLE II POWER SUPPLY

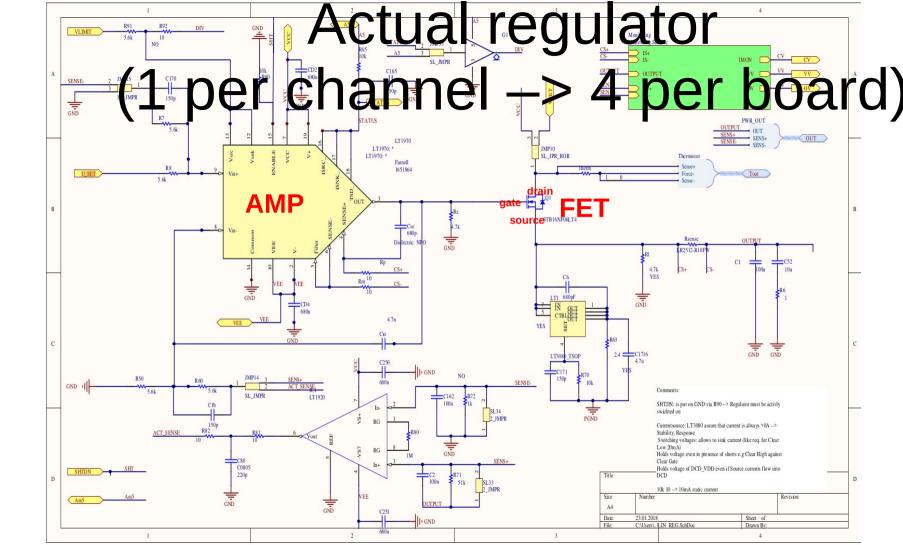

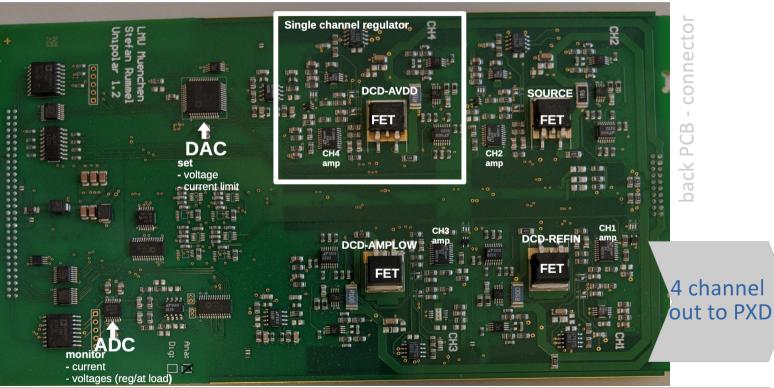

### THE REGULATOR BOARD: 4 CHANNELS ON ONE BOARD EXAMPLE: ANALOG BOARD

DC power in

ront PCB - connector

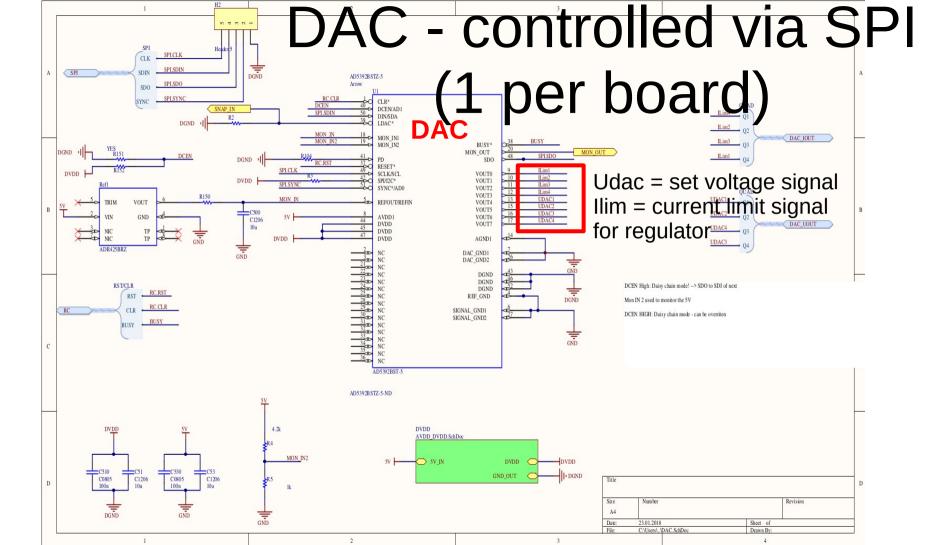

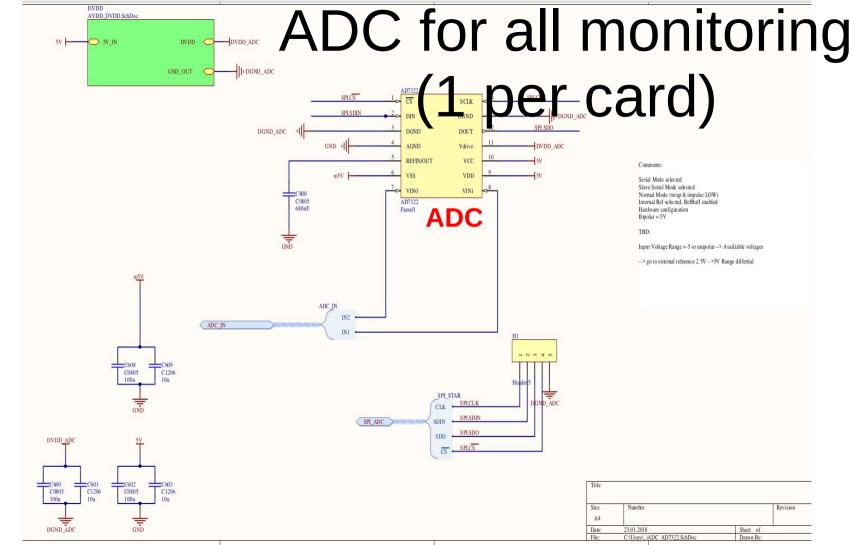

#### THE DEVICES

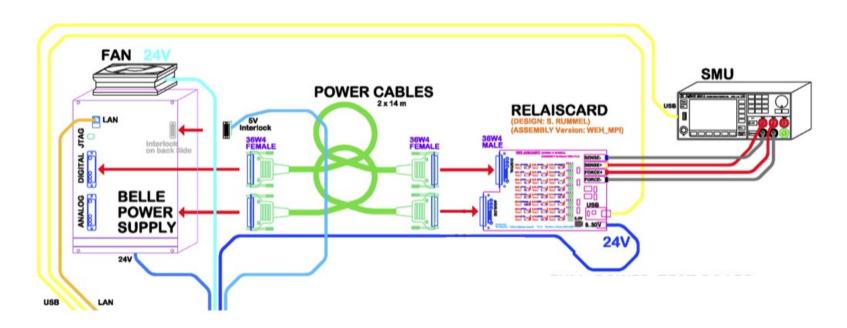

Drawn by W. Haberer haberer@mpp.mpg.de

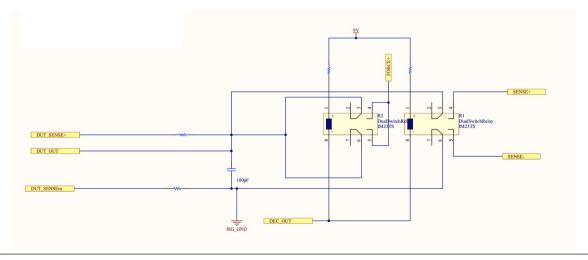

#### THE RELAISBOARD

Job of relaisboard:

→ Connecting one channel at a time to SMU

Two Relais for each channel:

→ Forcelines and senselines

connectors for force and sensing to SMU

control LEDs

relays for each channel

analog/digital connector to PS

#### THE SOURCE MEASURE UNIT (SMU)

- "Simulates the PXD" in the calibration process

- Function of device: measures I/V, forces I/V

controlled/read out by PC

Force- and sense connectors

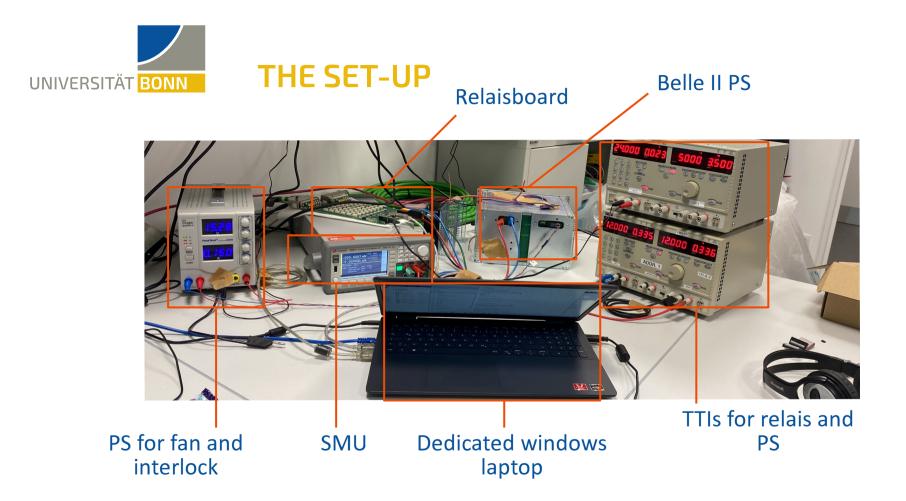

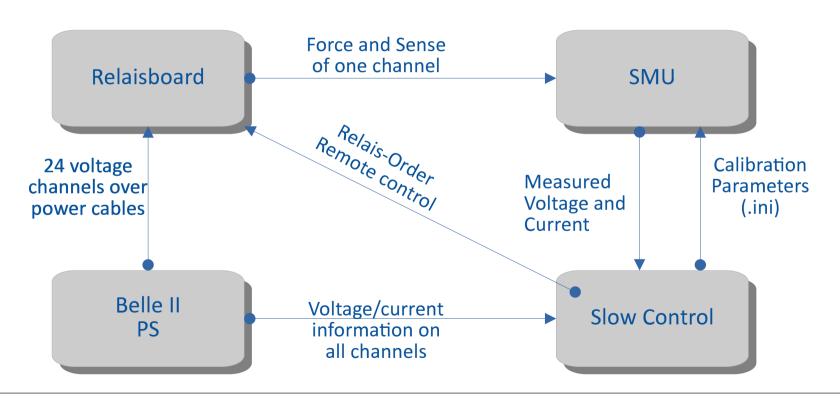

#### THE SOFTWARE

- → The software runs on dedicated Windows laptop

- Remote control and monitoring of the SMU, the relaisboard and PS

- What else is it used for:

- → Has eclipse to flash <u>old</u> chromosome (XME)-based version of the firmware

https://stash.desy.de

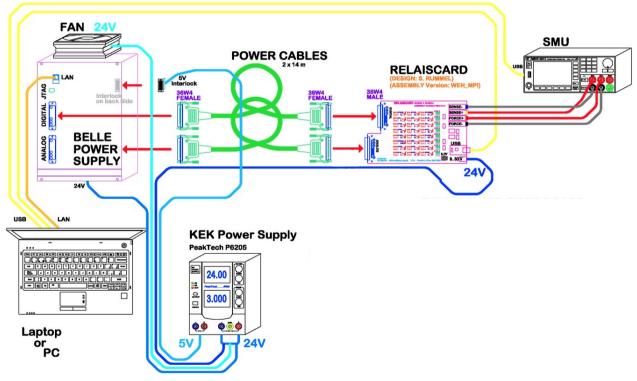

#### THE SET-UP

Drawn by W. Haberer haberer@mpp.mpg.de

# THE SET-UP THE WORKING PRINCIPLE FIRST CALIBRATIONS OUTLOOK

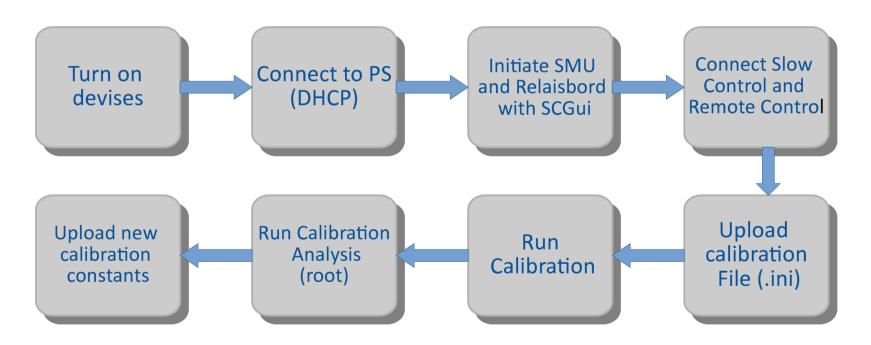

#### **CALIBRATION WORKFLOW**

# THE SET-UP THE WORKING PRINCIPLE FIRST CALIBRATIONS OUTLOOK

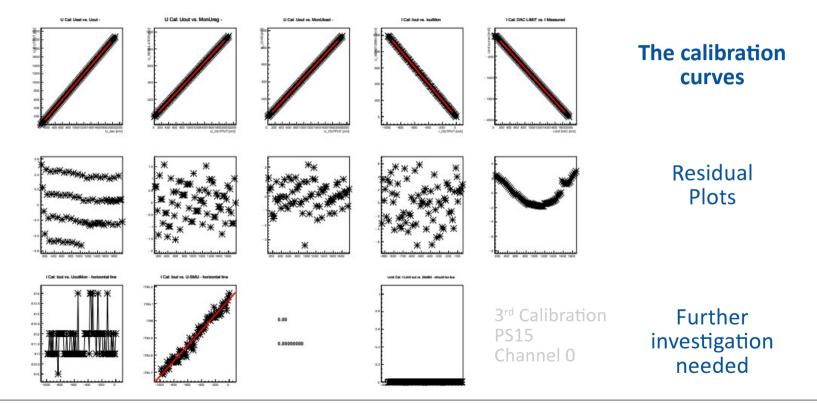

#### **THE CALIBRATION CURVES**

#### **UPLOADING THE CALIBRATION DATA**

SCGUI channel monitoring **before** calibration

|           | Set Voltage (mV) | Set Current (mA) | Itage at Regulator (m | Voltage at Load (mV) | Current (mA) | Regulator Status Bit | UPS Satus         |

|-----------|------------------|------------------|-----------------------|----------------------|--------------|----------------------|-------------------|

| DHP_IO    | 0                | 0                | -6                    | -4                   | -8           | LOW                  | Thermal Sta       |

| SW_DVDD   | 0                | 0                | -6                    | -6                   | -4           | LOW                  | OVP Fast Sa       |

| DCD_DVDD  | 0                | 0                | -7                    | -4                   | -7           | LOW                  |                   |

| DHP_CORE  | 0                | 0                | -6                    | -4                   | -2           | LOW                  |                   |

| RefIn     | 0                | 0                | -10                   | -4                   | -9           | LOW                  |                   |

| Source    | 0                | 0                | -8                    | -4                   | -6           | LOW                  |                   |

| DCD_AVDD  | 0                | 0                | 1                     | -4                   | -2           | LOW                  |                   |

| AmpLow    | 0                | 0                | -8                    | -4                   | -3           | LOW                  | Start             |

| CCG1      | 0                | 0                | 1757                  | 1202                 | -3           | LOW                  |                   |

| CCG2      | 0                | 0                | 1759                  | 1203                 | -8           | LOW                  | Stop              |

| DRIFT     | 0                | 0                | 1759                  | 1203                 | -8           | LOW                  | :mergencyShutdowr |

| CCG3      | 0                | 0                | 1759                  | 1203                 | -4           | LOW                  | Soft Reset        |

| POLYCOVER | 0                | 0                | -4                    | -4                   | -9           | LOW                  |                   |

| HV        | 0                | 0                | -1                    | -8                   | -9           | HIGH                 |                   |

| GUARD     | 0                | 0                | -6                    | -6                   | 10           | LOW                  |                   |

| BULK      | 0                | 0                | -6                    | -4                   | -13          | LOW                  |                   |

| GateON1   | 0                | 0                | 1756                  | 1940                 | -7           | LOW                  |                   |

| GateON2   | 0                | 0                | 1757                  | 1942                 | -4           | LOW                  |                   |

| GATEOFF   | 0                | 0                | 1755                  | 1942                 | -25          | LOW                  |                   |

| GateON3   | 0                | 0                | 1756                  | 1943                 | -7           | LOW                  |                   |

| Clear_ON  | 0                | 0                | -2                    | -3                   | 2            | LOW                  |                   |

| SWREF     | 0                | 0                | -7                    | -9                   | -6           | LOW                  |                   |

| SWSUB     | 0                | 0                | -8                    | -8                   | 2            | LOW                  |                   |

| Clear_OFF | 0                | 0                | -4                    | -3                   | -2           | LOW                  |                   |

PS 87

#### **UPLOADING THE CALIBRATION DATA**

SCGUI channel monitoring **after** calibration

|           | Set Voltage (mV) | Set Current (mA) | Itage at Regulator (m | Voltage at Load (mV) | Current (mA) | Regulator Status Bit | UPS S            |

|-----------|------------------|------------------|-----------------------|----------------------|--------------|----------------------|------------------|

| DHP_IO    | 0                | 0                | 6                     | 2                    | -6           | LOW                  | Thern            |

| SW_DVDD   | 0                | 0                | 4                     | 3                    | -1           | LOW                  | OVP F            |

| DCD_DVDD  | 0                | 0                | 2                     | 2                    | 0            | LOW                  |                  |

| DHP_CORE  | 0                | 0                | 5                     | 1                    | 0            | LOW                  |                  |

| Refln     | 0                | 0                | 12                    | 2                    | 0            | LOW                  |                  |

| Source    | 0                | 0                | -5                    | 5                    | -8           | LOW                  |                  |

| DCD_AVDD  | 0                | 0                | 13                    | 2                    | 2            | LOW                  |                  |

| AmpLow    | 0                | 0                | 7                     | 1                    | 0            | LOW                  | Start            |

| CCG1      | 0                | 0                | 1                     | 1                    | 0            | LOW                  |                  |

| CCG2      | 0                | 0                | 0                     | 1                    | 0            | LOW                  | Stop             |

| DRIFT     | 0                | 0                | 0                     | 2                    | 0            | LOW                  | :mergencyShutdow |

| CCG3      | 0                | 0                | -4                    | -2                   | 0            | LOW                  | Soft Reset       |

| POLYCOVER | 0                | 0                | 5                     | 9                    | 0            | LOW                  |                  |

| HV        | • 0              | 0                | -319                  | -242                 | -629         | HIGH                 |                  |

| GUARD     | 0                | 0                | -5                    | -3                   | 0            | LOW                  |                  |

| BULK      | 0                | 0                | 14                    | 28                   | 0            | LOW                  |                  |

| GateON1   | 0                | 0                | -2                    | 0                    | 0            | LOW                  |                  |

| GateON2   | 0                | 0                | -5                    | -1                   | 0            | LOW                  |                  |

| GATEOFF   | 0                | 0                | 4                     | -6                   | 0            | LOW                  |                  |

| GateON3   | 0                | 0                | 3                     | 1                    | 0            | LOW                  |                  |

| Clear_ON  | 0                | 0                | 19                    | 8                    | 0            | LOW                  |                  |

| SWREF     | 0                | 0                | -12                   | -7                   | 0            | LOW                  |                  |

| SWSUB     | 0                | 0                | -9                    | -9                   | 0            | LOW                  |                  |

| Clear_OFF | 0                | 0                | 16                    | 14                   | 0            | LOW                  |                  |

PS 87

#### **UPLOADING THE CALIBRATION DATA**

SCGUI channel monitoring after calibration

|           | Set Voltage (mV) | Set Current (mA) | Itage at Regulator (m | Voltage at Load (mV) | Current (mA) | Regulator Status Bit | UPS Satus                  |

|-----------|------------------|------------------|-----------------------|----------------------|--------------|----------------------|----------------------------|

| DHP_IO    | 0                | 0                | 6                     | 2                    | -6           | LOW                  | Thermal Status             |

| SW_DVDD   | 0                | 0                | 4                     | 3                    | -1           | LOW                  | OVP Fast Satus             |

| DCD_DVDD  | 0                | 0                | 2                     | 2                    | 0            | LOW                  | OVI Tust sucus             |

| DHP_CORE  | 0                | 0                | 5                     | 1                    | 0            | LOW                  |                            |

| Refln     | 0                | 0                | 12                    | 2                    | 0            | LOW                  |                            |

| Source    | 0                | 0                | -5                    | 5                    | -8           | LOW                  |                            |

| DCD_AVDD  | 0                | 0                | 13                    | 2                    | 2            | LOW                  |                            |

| AmpLow    | 0                | 0                | 7                     | 1                    | 0            | LOW                  | Start                      |

| CCG1      | 0                | 0                | 1                     | 1                    | 0            | LOW                  |                            |

| CCG2      | 0                | 0                | 0                     | 1                    | 0            | LOW                  | Stop                       |

| DRIFT     | 0                | 0                | 0                     | 2                    | 0            | LOW                  | :mergencyShutdowr          |

| CCG3      | 0                | 0                | 4                     | 2                    | 0            | LOW                  | Soft Reset                 |

| POLYCOVER | 0                | 0                | 5                     | 9                    | 0            | LOW                  |                            |

| HV        | • 0              | 0                | -319                  | -242                 | -629         | HIGH                 |                            |

| GUARD     | 0                | 0                | -5                    | -3                   | 0            | LOW                  |                            |

| BULK      | 0                | 0                | 14                    | 28                   | 0            | LOW                  | Due le le recent de la LIV |

| GateON1   | 0                | 0                | -2                    | 0                    | 0            | LOW                  | Problems with HV           |

| GateON2   | 0                | 0                | -5                    | -1                   | 0            | LOW                  | channel                    |

| GATEOFF   | 0                | 0                | 4                     | -6                   | 0            | LOW                  |                            |

| GateON3   | 0                | 0                | 3                     | 1                    | 0            | LOW                  | → Not understood           |

| Clear_ON  | 0                | 0                | 19                    | 8                    | 0            | LOW                  |                            |

| SWREF     | 0                | 0                | -12                   | -7                   | 0            | LOW                  | at this point              |

| SWSUB     | 0                | 0                | -9                    | -9                   | 0            | LOW                  |                            |

| Clear_OFF | 0                | 0                | 16                    | 14                   | 0            | LOW                  |                            |

PS 87

#### **CHALLENGES FACED SO FAR**

#### **Setting up the Software is not trivial:**

- PS with old firmware has no static IP

- → Communication via DHCP server

- Installing everything to flash old firmware

- → Programs used very out of date

- Git master branch does not contain correct versions needed for calibration

https://confluence.desy.de

# THE SET-UP THE WORKING PRINCIPLE FIRST CALIBRATIONS OUTLOOK

#### **GOALS FOR MY THESIS**

- 1) Commissioning of calibration set-up in Bonn

- Including working HV channel

- 2) Generating the calibration constants and plots with **Python**

- Slope and offset given with plots

- 3) Automatic pass/fail for successful calibration

- 4) Drift/stability studies

- 5) **Comparison** between different PS units

- 6) Update and complete **documentation**

#### **FURTHER OUTLOOK**

#### If there is enough time, we would like to...

... Change from Windows to Linux

... Make it work with the latest firmware

... Simplify the calibration process

... Simplify the Set-Up for calibration

### Thank you!

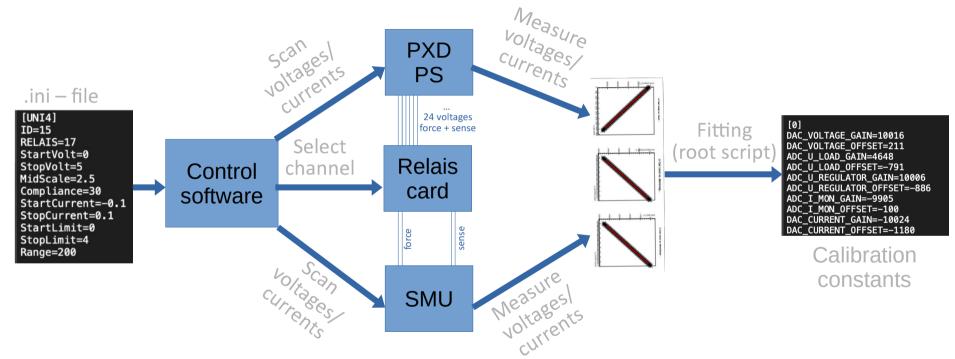

#### GENERATING THE CALIBRATION CONSTANTS

- 80 measuring points set for each channel

- Voltage range and current change set for each channel

```

[0]

DAC_VOLTAGE_GAIN=10016

DAC_VOLTAGE_OFFSET=211

ADC U LOAD GAIN=4648

ADC_U_LOAD_OFFSET=-791

ADC_U_REGULATOR_GAIN=10006

ADC_U_REGULATOR_OFFSET=-886

ADC_I_MON_GAIN=-9905

ADC_I_MON_OFFSET=-100

DAC_CURRENT_GAIN=-10024

DAC_CURRENT_OFFSET=-1180

```

19/05/2022 25

#### THE SIGNAL-PATH

#### **CALIBRATION WORKFLOW**

#### THE CALIBRATION CONSTANTS

3<sup>rd</sup> Calibration PS15 Channel 0

| [0]                         |                                                       |

|-----------------------------|-------------------------------------------------------|

| DAC_VOLTAGE_GAIN=10016      | output voltage (SMU)                                  |

| DAC_VOLTAGE_OFFSET=211      | vs. input voltage                                     |

| ADC_U_LOAD_GAIN=4648        | monitored voltage at load vs. measured output voltage |

| ADC_U_LOAD_OFFSET=-791      | vs. Measured output voltage                           |

| ADC_U_REGULATOR_GAIN=10006  | monitored voltage at regulator                        |

| ADC_U_REGULATOR_OFFSET=-886 | vs. measured output voltage                           |

| ADC_I_MON_GAIN=-9905        | monitored output current                              |

| ADC_I_MON_OFFSET=-100       | vs. measured output current                           |

| DAC_CURRENT_GAIN=-10024     | measured output current                               |

| DAC_CURRENT_OFFSET=-1180    | vs. set DAC limit                                     |

#### **PS-REMOTE CONTROL**

- Remote control of SMU

- Initializing of relaisboard

- Uploading information for calibration

- → .ini file containing information on each channel

- Monitor progress of calibration

[UNI4]

ID=15

RELAIS=17

StartVolt=0

StopVolt=5

MidScale=2.5

Compliance=30

StartCurrent=-0.1

StopCurrent=0.1

StartLimit=0

StopLimit=4

Range=200

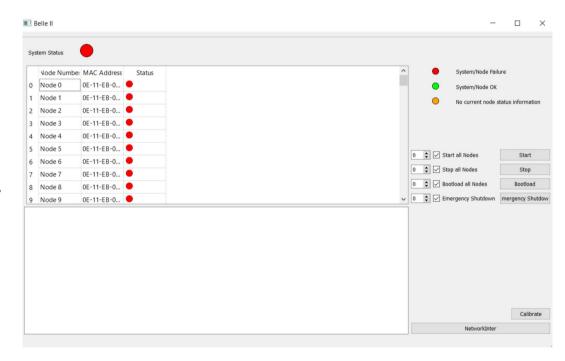

#### **SLOW CONTROL GUI**

- List of the nodes

- Resetting the calibration constants to default

- Monitoring each channel for the DUT

- Uploading new calibration constants

#### THE DOUBLE RALAIS

- Calibration of sensing for each channel

- → Ensuring correct voltage at DUT

- Double relais to connect force and sense and force to SMU