LMU – Cluster Universe Stefan Rummel

# Power supply for the BELLE II PXD

**5th International Workshop on DEPFET Detectors and Applications**

29.09-30.09. Valencia

### **Overview**

- News from LMU

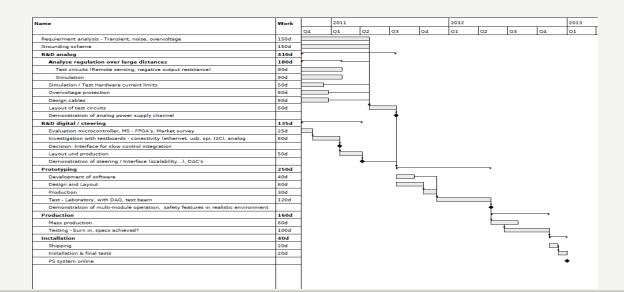

- PS project schedule

- Requirement analysis

- Parameter definitions currents, voltages

- Transient behavior

- Radiation, B-Field

- Position of PS

- Regulation over long distances and test structures

- PS Slowcontrol

- Since July member of the BELLE II collaboration

- Regular EVO meeting on PS development

•Group is growing – Electronics Engineer Andreas Seiler has joint us in of August

- Setup of electronics lab is almost finished

- Mixed signal oscilloscope / current probe

- AC/DC active load

- Signal generator, 6.5 digit DMM, PS's

- Soldering equipment

- Layout program Altium Designer

- ...

- Important milestones:

- Demonstration regulation under realistic conditions (cable, distance, noise, transients...)

- Demonstrate connectivity, steering of analog part

- Prototype: demonstration of multi module operation, safety features

- Prototype for testing of ladders in 06/2012

- Commissioning beginning of 2013

### **Requirements update**

### **Position of PS**

- Baseline: Outside of detector (same as DHH)

- Moderate distance of ~15m from IP

- Primary supplies in electronics hut 30m from IP

- Magnetic field ~10 Gaus ( ~ mT)

- Estimate on radiation based on outer layer of KLM to our current best knowledge 0.48Hz/cm2

- •Back on the envelope calculation gives:

- → 50rad over 5 years including factor 100 safety (assuming MIPS)

- Radiation and magnetic field seem to be no problem outside of the detector

- Commercial components should do the job

- High voltage increased from 40V to 80V due to lower resistivity silicon, punch through biasing and thicker detector

- For calibration propose the Gate voltage must be variable from threshold to nominal value (~ V\_SOURCE to V\_SOURCE + 6V)

- Ganging has also impact on power consumption:

- I\_SOURCE doubles from 100mA to 200mA

- Currents of steering voltages

- Rest should be stable

### **Transient behaviour**

#### No regulation is ideal

- DC regulation not perfect

- Load steps lead to temporary deviations

- Deviations need to be controlled:

- Overshoots can damage oxide

- Undershoot may lead to loss of data

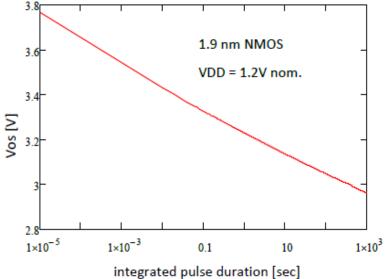

- two DHP voltage domains: core with thin gate oxide and IO with thick gate oxide MOSFETs

- recommended values according to the equations in the IBM CMOS 90nm (CMS9FLP) Technology Design Manual for gate dielectric reliability voltage limits:

- Vdc max: maximum static DC voltage (@ 100.000 operation hours, T = 30°C)

- Vos 1%: maximum overshoot for periodic signals, calculated for overshoot pulse width equal to 1% cycle time

- overshoot due to power switching has much less duty cycle

- transient stress damage is a product of pulse duration and the number of events = integrated pulse duration

|             | Tox<br>[nm] | V nom<br>[V] | Vdc max<br>[V] | Vos 1%<br>[V] |

|-------------|-------------|--------------|----------------|---------------|

| Thin oxide  | 1.9         | 1.2          | 1.6            | 2.7           |

| Thick oxide | 5.2         | 1.8          | 3.5            | 4.2           |

- •Assuming: 50us overshoot, 1 overshoot/run, 10min/run

- $\rightarrow$  Duty cycle <10<sup>-7</sup>

- Numbers at 30degC

- Need some room for radiation induced damage

•"Vos 1%" should be conservative – but some doubts remain...

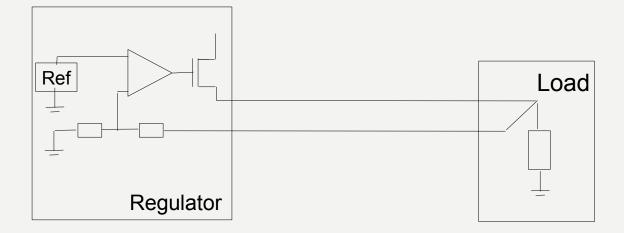

### **Regulation over long distances**

## Regulation over large distaces

- Twofold approach:

- Simulation (Matlab, Spice)

- Experimental

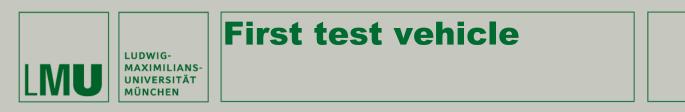

- Test regulator

- Long cables

- •Discrete pass element linear regulator

- •Hardware current limit

- •Various ways of remote sensing no, passive, active

- Why LT1970?

- Integrated current limit amplifier hardware current limit

- Enable pin and thermal shutdown

- Specified from 5V to 36V supply voltage

- >500mA output current

- Also used in NI PXI-4110 PS

- Very low dropout voltage

- Output can be set down to 0V

- Power consuming part separated from "intelligence"

- FETS with low thermal resistance packages available → easy thermal management

- NMOS source at output → good PSSR

- Precise current sensing on "high side" no additional resistor between load and regulator

- Can be easily configured as current sink

- Need additional voltage (few mA) to drive the FET

- Allows a unified design which serves for ALL voltages (except HV)

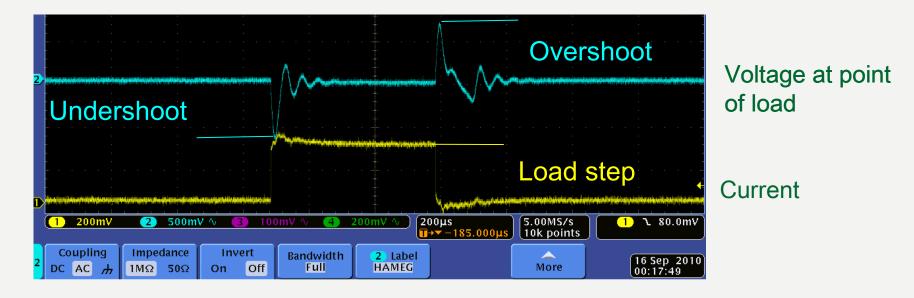

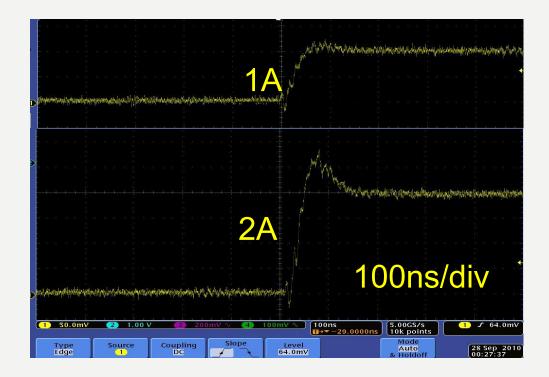

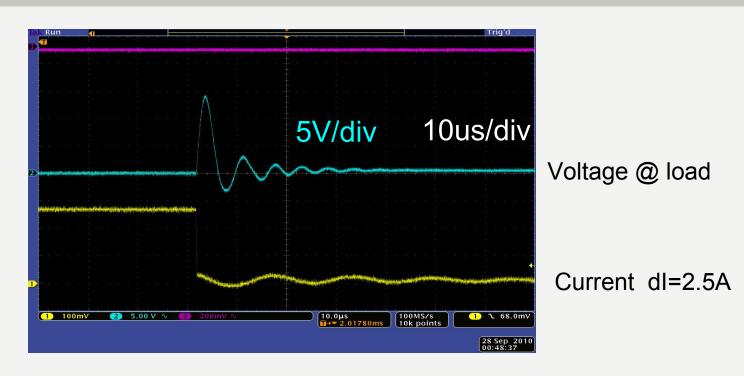

- Circuit to simulate fast transients (few Amps @ 50ns risetime)

- Long cables in AWG12/18 as TDR cable

- Test bench is available

- Load and regulator share common ground

- Realistic delays

An interesting the second

200µs ∎→▼ –185.000µs

2 Label

HAMEG

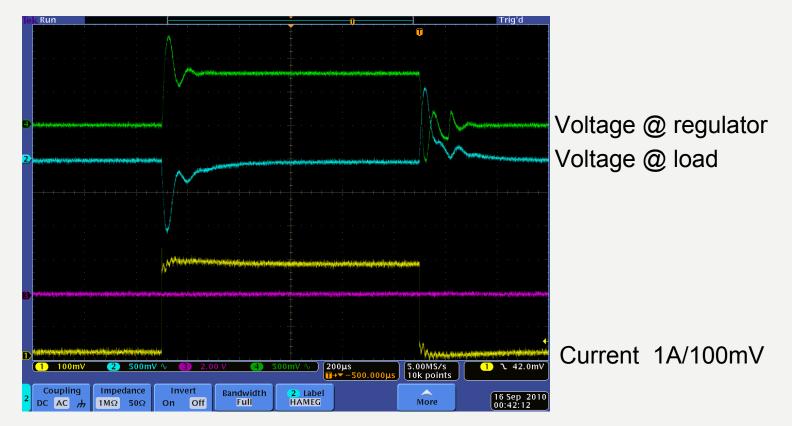

2.5A load step

1 **1** 80.0mV

16 Sep 2010 00:17:49

5.00MS/s 10k points

$\wedge$

More

• Wire: 7.5m, AWG 18  $\rightarrow$  170m $\Omega$

On

Invert

Off

Bandwidth

Full

• (0.1/2.6)A load step

2

Impedance

1MΩ 50Ω

Overshoot: 700mV for 20us

500mV ∿

200mV

Coupling

DC AC H

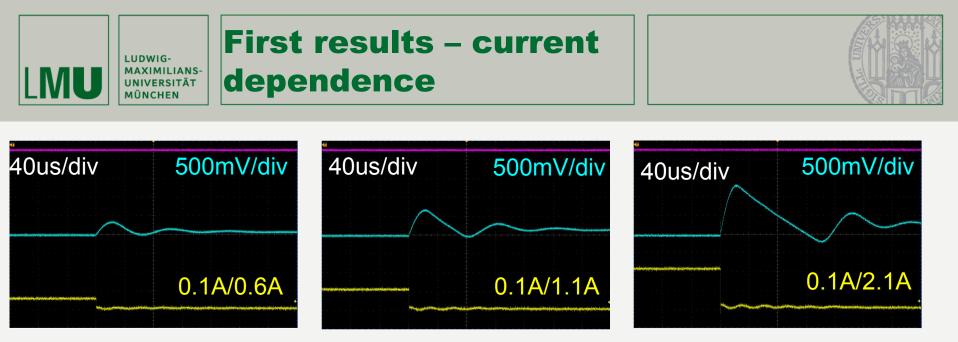

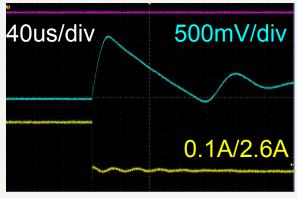

### **First results**

- Wire: 15m, AWG 18, 320mΩ

- (0.1/2.6)A load step

- Overshoot: 1V for 20us

- Increase of 40% compared to 7.5m

- Wire: 15m, AWG 18, 320mΩ

- (0.1/2.6)A load step

- Load capacity 100nF

- Overshoot: ~14V

"DHP"

- Wire: 15m, AWG 18,  $320m\Omega$

- Load capacity 10uF

- $\rightarrow$  Overshoot scales with current

### **Comments/ Next steps**

•Up to now regulator behaved quite stable ( 100nF - 50uF ceramic capacitors, with  $100m\Omega$  ESR, various cable length)

- •Get more experience with the regulator:

- Region of stability

- Comprehensive DC characterization

- Noise

- •Improve sensing:

- Reduce DC error: Active sense amplifier with high input impedance

- Test impact of termination (at HF)

- Test current limit

- Include flex (prototype) into tests

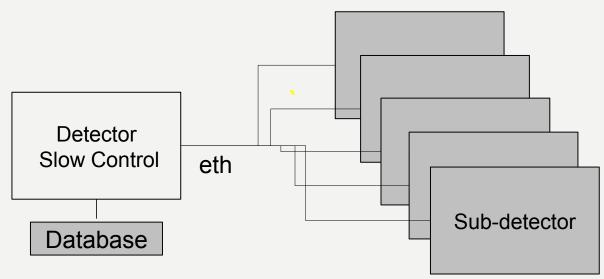

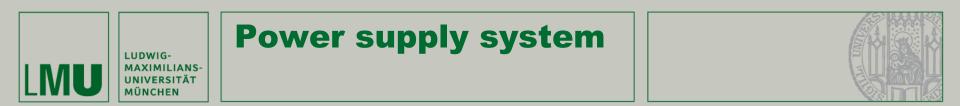

### **Slow control**

- Slow control

- Control of services (power, cooling)

- Logging of temperatures, voltages, currents, calibration data...

- •Distributed system

- ·Connected via Ethernet

- ·Each sub-detector provides a producer

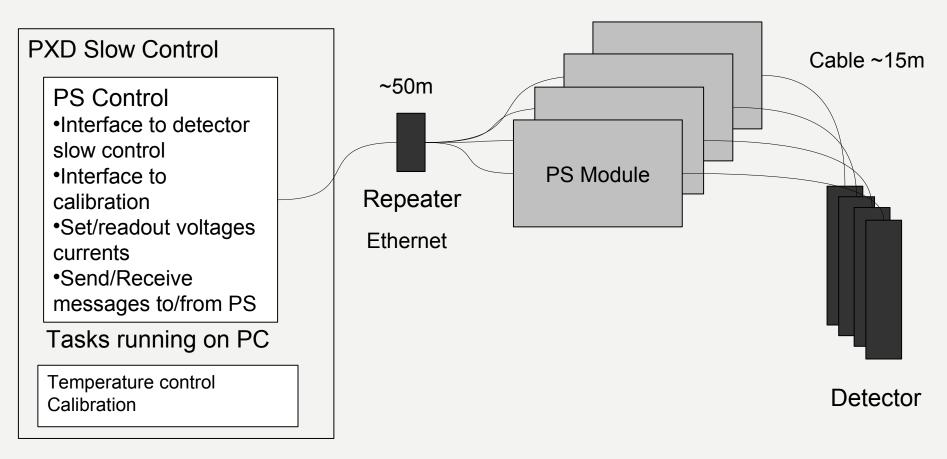

### **Power supply module**

- Tasks on MCU

- Continuous reporting to PS control (~10Hz)

- Error handling

- Error messages in case of failures

- Receive messages from control

- Readout currents/voltages

- Set voltages and currents

- Start and stop sequences

- Looked into various MCU architectures identified ARM Cortex e.g. STM32F as interesting

Interface to outer world ETHInterface to analog section (SPI, I2C)

- TUM computer science chair for "Robotics and Embedded Systems" with strong background in safety critical systems, embedded systems, real time applications...

- First exploratory discussion with Prof. Knoll

- •Showed interests in the software part of the PS slow control (embedded part and PC)

### **Open issue**

- Overvoltage protection

- For low currents no problem can be made on PS level

- Wishlist: High current OVP on patch panel

- Radhard solution requiered

- Currently looking into ATLAS-SCT solution

- Maybe we can relax this:

- DHP core: Vdc max-Vnom = 400mV

- DHP IO: Vdc max-Vnom = 1.7V

- PS voltage at 1A: Vnom+300mV (AWG12 15m + 150mOhm flex)

- → OVP @ PS is able to limit the voltage to safe regions

- Requirements on voltages, transient behavior are converging

- PS development at LMU has started, first circuitry tested

- Results under realistic conditions cable length, various loads can be expected till next B2GM

### **Backup**

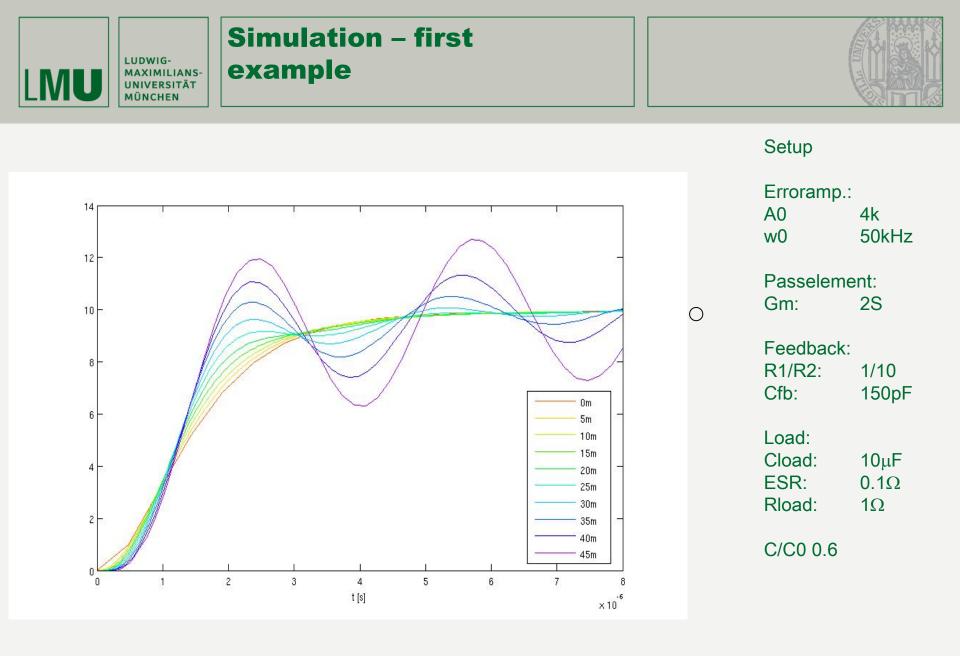

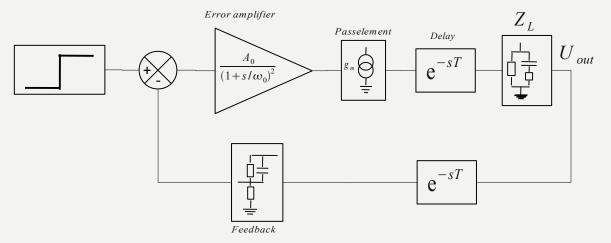

Simulation of regulator response with delays

Delay at least L/c c~0.6c0 → 55ns for 10m cable

Investigated model:

Figure of merit:

- Step response

- Settling time, over shoot, rise time...

- Phase margin