P. Ahlburg, F. Bernlochner, J. Dingfelder, H. Krüger, B. Paschen, P. Wolf

# PXD Power Supply Over Voltage Protection (OVP) Studies

PXD Workshop and 25th International Workshop on DEPFET Detectors and Applications

May 22, 2023

### **OVER VOLTAGE PROTECTION BOARD**

- Part of the PXD-Power Supply (PXD-PS)

- Protects the detector and associated electronics (ASICs) against overvoltage/under-voltage conditions

- OVP board protects 24 conditions

(23 voltage channels)

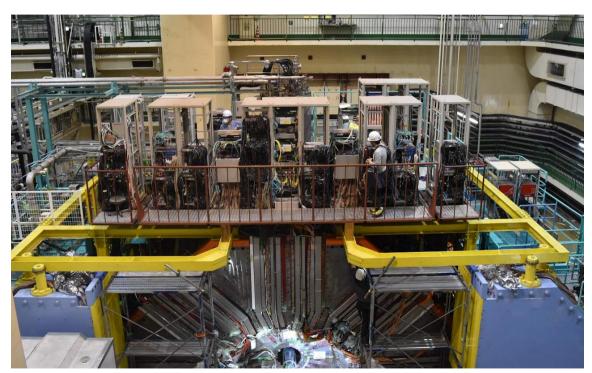

- Approx. 15 m outside of the Belle II experiment (on top of Belle II)

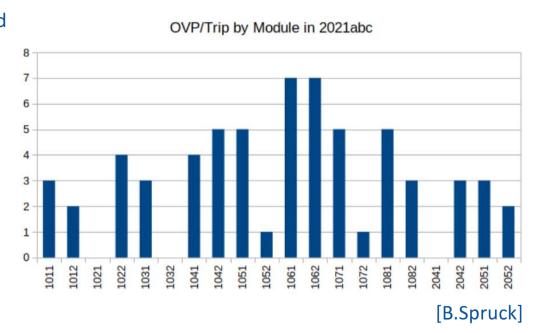

#### **OVP ISSUES AT BELLE II**

- OVP events ("HV Trip") rate increased in spring 2021 (beam currents were increased)

- Rate approx. 0.5-1 per day

- Talks by Björn Spruck:

- PXD HV "Trips" Issues By Over-Voltage-Protection (link)

- Update on PXD HV "Trips" Issues

By Over-Voltage-Protection (link)

#### OVP ISSUES AT BELLE II

- OVP events ("HV Trip") rate increased in spring 2021 (beam currents were increased)

- Rate approx. 0.5-1 per day

- Talks by Björn Spruck:

- PXD HV "Trips" Issues By Over-Voltage-Protection (link)

- Update on PXD HV "Trips" Issues

By Over-Voltage-Protection (link)

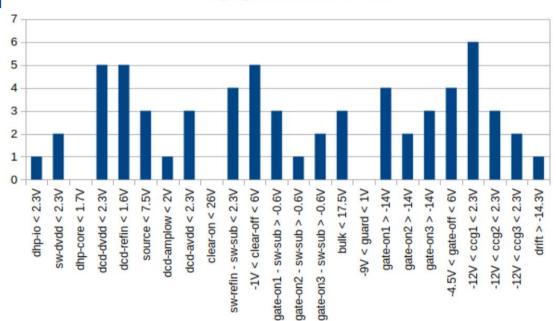

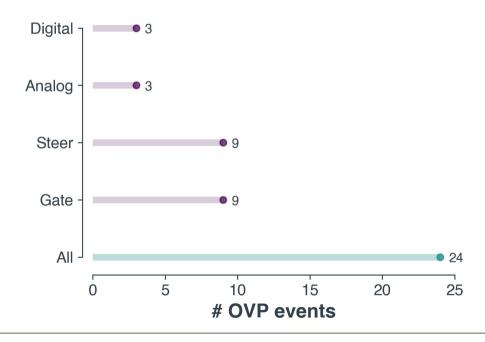

#### OVP/Trip by Channel in 2021abc

[B.Spruck]

#### POSSIBLE REASONS FOR OVP EVENTS

- Observation: OVP events occur even when voltage regulators are switched off

- Effect of radiation on the logic can cause triggering of OVP events

- Single Event Upsets (SEUs) can trigger an OVP event

- Vulnerable to these events: Control logic implemented in the Complex Programmable Logic Device (CPLD)

**CPLD** on the OVP board

22/05/2023 5

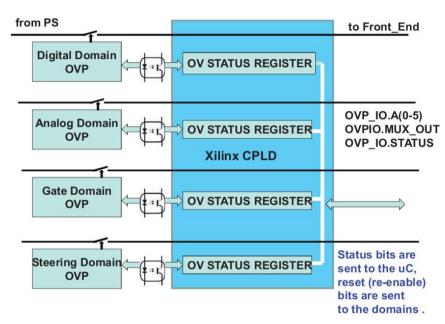

## **OVER VOLTAGE PROTECTION (OVP)**

- Voltages are grouped in 4 domains:

Analog, Digital, Steering and Gate

- Four independent grounds

- Each supply channel is equipped with the protecting circuitry

- Central logic unit (Xilinx CPLD) is connected to all protecting circuits (optocouplers)

- Collects status bits from every channel

[P.Kapusta]

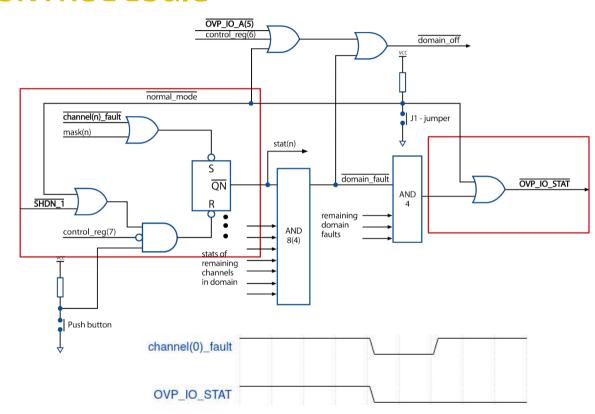

#### **CPLD CONTROL LOGIC**

- Control logic in the CPLD:

- 1. After detecting an error condition in a channel, **channel(n)\_fault** is received

- 2. The signal is fed into an asynchronous latch (set S)

- 3. A general fault signal is sent: **OVP IO STAT**

- 4. An "emergency off" is issued

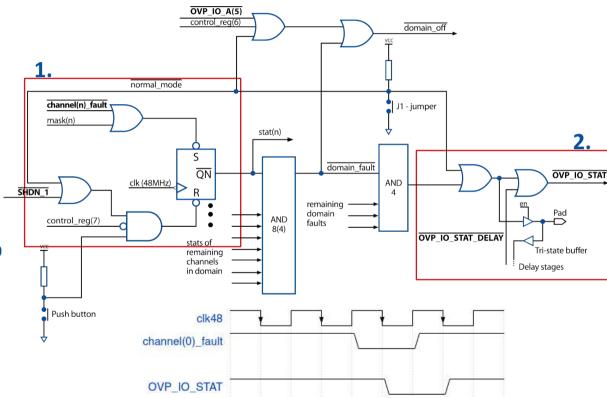

#### **CPLD CONTROL LOGIC**

- Countermeasures against SEUs:

- 1. Use of a **flip-flop (clocked)** instead of latch: reduces the probability of triggering on a short fault signal / resets state after SEU

- Pulse length filter for OVP\_IO\_STAT signal to prevent short pulse signals within the CPLD

- Clock frequency is transmitted from second CPLD via an existing line

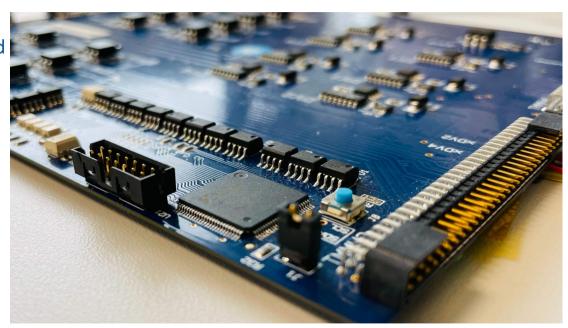

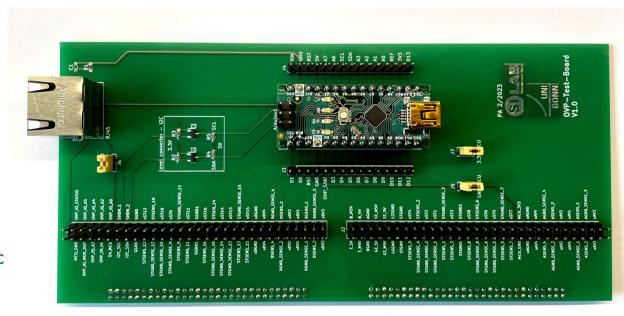

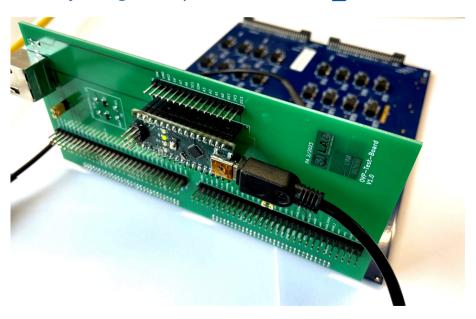

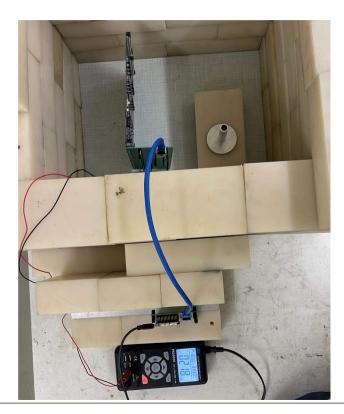

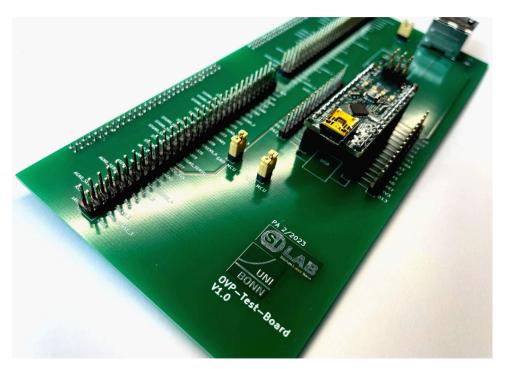

## **OVP-TEST-BOARD**

- Logic behavior tested in simulations

- OVP-Test-Board designed for stand-alone OVP tests

- Houses an Arduino Nano

- Communicate with auxiliary

CPLD (via *I2C*) -> status of

individual channels, write

masks or reset the control logic

- Signals on the OVP board can be measured

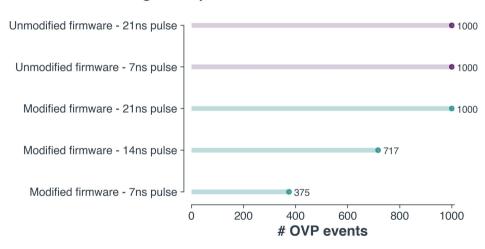

### **OVP-TEST-BOARD MEASUREMENTS**

Injecting short pulses to channel\_fault

#### **OVP testing - 1000 pulses**

- Goal: Verify that changes in logic lead to a reduction in OVP events by SEU

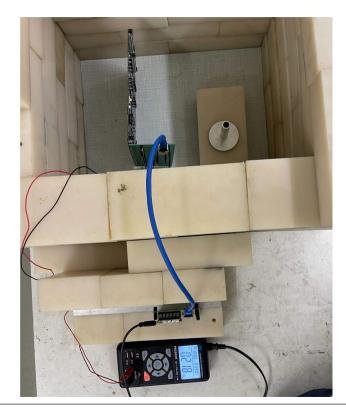

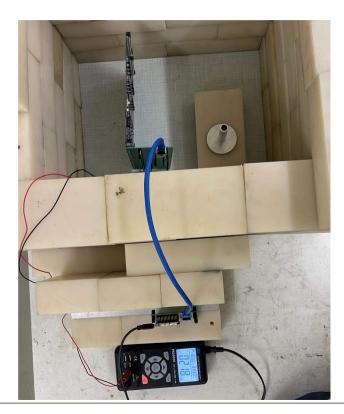

- Neutron source measurement at Helmholtz-Institut für Strahlen- und Kernphysik (HISKP) in Bonn

- Measured 303 muSv/h (distance 17.5cm)

- Duration of the measurement: 18 h

**Neutron detector**

**Neutron source**

#### **OVP old firmware - Neutron source**

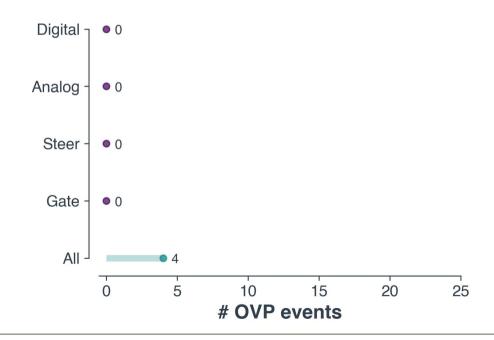

#### **OVP** new firmware - Neutron source

#### **CONCLUSION**

- Simulation and measurements show desired reduction of SEU triggered OVP events

- Tests of the OVP board installed in the PXD-PS show the functionality of the new firmware

- But: Information about which channel triggers is missing

- Possible solution already under test

### **DOCUMENTATION**

Documentation and files on: https://github.com/SiLab-Bonn/PXD-OVP