0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0 0

# **SWITCHER-B 2.3 – PROBE CARD TESTS**

Treis, Koffmane

## **SWITCHER-B 2.3**

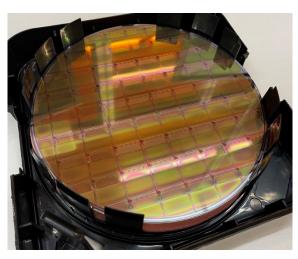

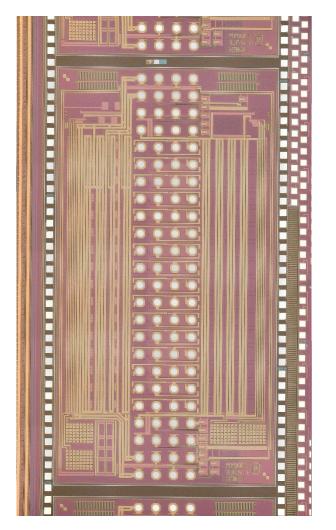

- Two 200 mm wafers were received end of 2022

- SwticherB with pads (no bumps yet)

- Dedicated probe card ordered in 2022 for test on pads

- PA200 4inch probe card holder ordered and installed in 2022

## **SETUP ISSUES**

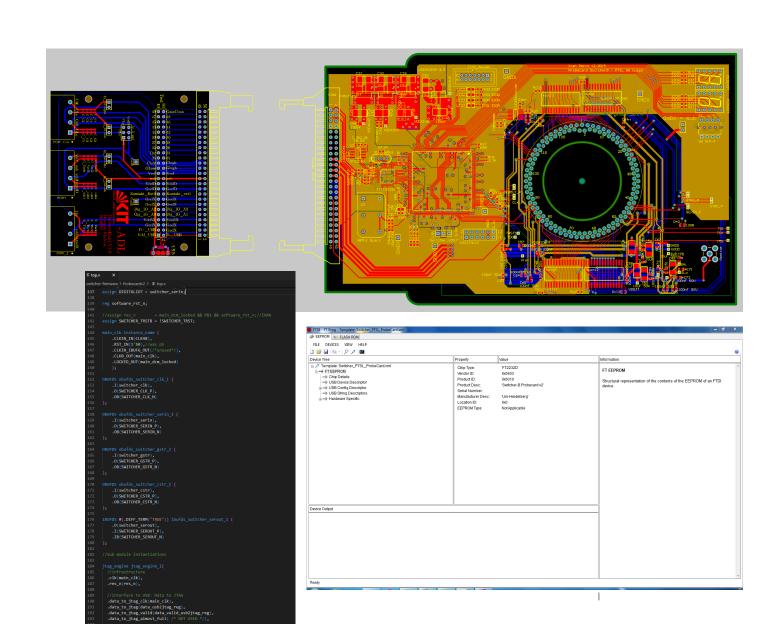

- Pin header orientation mirrored on delivery card (work around possible)

- short due to solder paste under the micro USB connector

- EEPROM for the configuration of the USB interface not programmed on new probe card (FT2232C default settings don't fit to probe card)

- res\_n assignment commented in Verilog code (all blocks in reset, no USB communication)

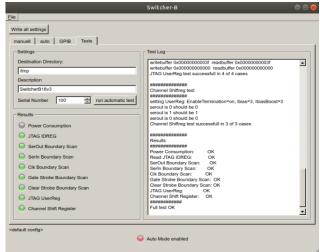

### **TEST RESULTS**

- SW-VDDD 1.8 V, 3 mA

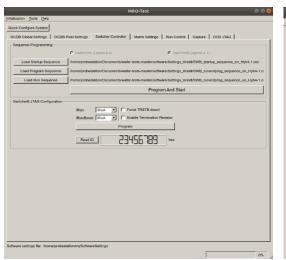

- JTAG chip ID readback okay (0x23456789)

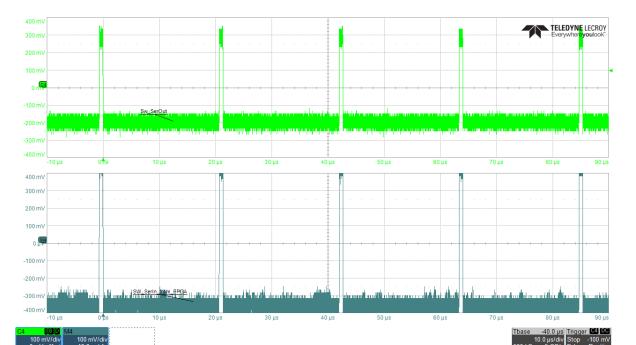

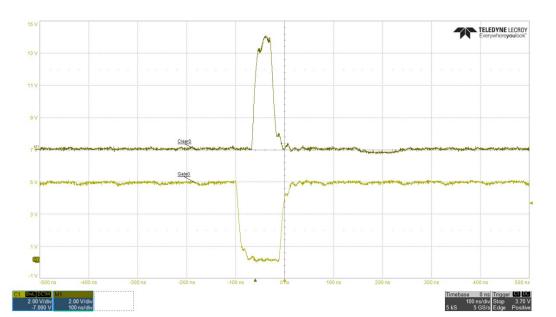

- SW\_SerOut okay, probed on pads on probe card

- random channels (gate0/clear0, gate1/clear1, gate28/clear28) probed on pads on probe card with different timings

- skipping gate1 applied in software and checked on the scope (gate0 is extended)

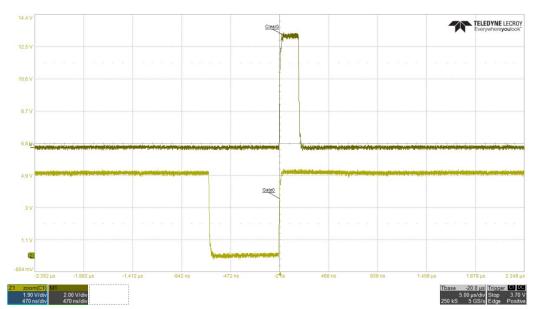

- Sw-Sub connected to GND, GateLow and ClearLow set to 0 V, GateHigh = 5V, ClearHigh = 7V

## **TEST RESULTS**

- random channels (gate0/clear0, gate1/clear1, gate28/clear28) probed on pads on probe card with different timings

- skipping gate1 applied in software and checked on the scope (gate0 is extended)

- Sw-Sub connected to GND, GateLow and ClearLow set to 0 V, GateHigh = 5V, ClearHigh = 7V

# **OPEN TOPICS**

- Test with application like Sw-Sub,

GateLo and ClearLo voltages

- Re-work probe card for bumped SwitcherB (needles not in a good shape)

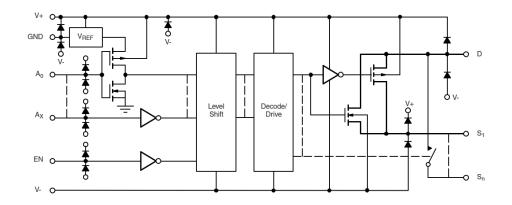

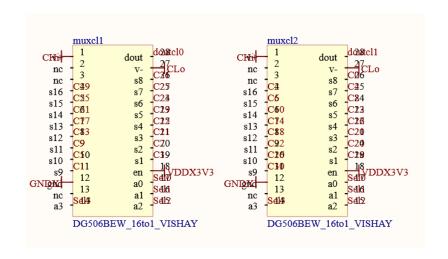

#### **SCHEMATIC DIAGRAM** Typical Channel